My no DAC project has achieved successful result after two months trial and error, though it's still under developing. I started to design 1bitDSM(no DAC) PCB to be able to have low noise floor fluctuation because it's relevant to SQ very much in my setup. THD has almost nothing to do with SQ. Theoretically speaking, the best solution to have low fluctuation is 1bitDSM, where no linearity is required in conversion from digital to analog. You can convert PCM into 1bitDSM(DSD) with hardware and make DSD into an analog signal with discrete parts. There are many ways to realize such DAC without a DAC chip. My attempt is FPGA and transistors to satisfy excellent performance which can compete with a modern commercial chip.

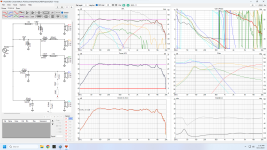

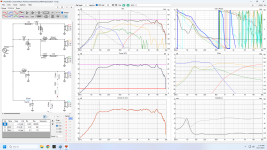

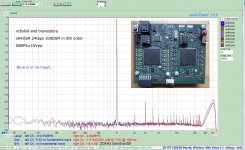

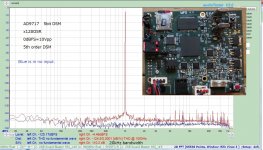

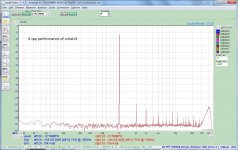

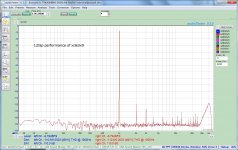

Two major strategies are mandatory to achieve the goal. FPGA and transistors with them can already outperform my DIYed 5bit DSM DAC, though the 1st pic is still an experimental result. THD+N is around 113dB, which is an almost impossible number for my 5bit DSM because it has a DAC chip(AD9717). The most challenging or impossible thing for a DAC chip is to have no noise floor fluctuation. I'm sure as long as a DAC chip has a resolution, even if it's 2bit, noise floor fluctuates as the amplitude becomes large. The 2nd pic is DIYed 5bitDSM(my 3bitDSM version also has the same plot). THD+N of 5bitDSM is around 110dB. If it wouldn't have a noise floor increase, you could have the same value as pic 1. THD is excellent because this is just after calibration. It matters little, and two or three days later you can't have the same number.

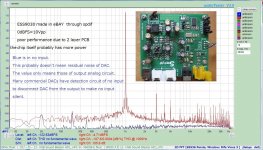

The 3rd pic is ES9038 made in eBay. This isn't a real performance of the chip since PCB is poor. If you use the chip at -0.1dBFS, the performance becomes far worse(the plot is at -2dBFS). Recent commercial chips usually don't have the best performance at fullscale. PCB construction is inevitably essential. I'm sure even carefully designed PCB can't remove noise floor fluctuation. So is AK4499. AK's homepage has two plots.

TECHNOLOGY | VELVET SOUND | AKM - Asahi Kasei Microdevices

One(the former) is at -155dBFS,the other(the latter) is at 0dBFS. You can see a moderate(6 to 8dB) noise floor increase. I would say low noise floor fluctuation doesn't exist in their to-do list.

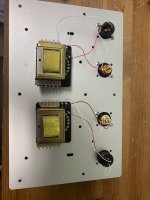

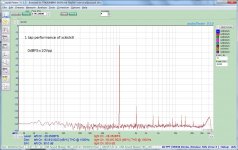

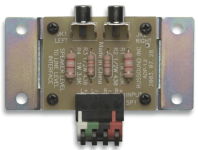

1bitDSM itself has an ordinary performance like the 4th pic, though noise floor level and absolute THD are excellent. Small signal level(-28.35dB) prevents you from high performance. One of the two necessary strategies is analog FIR, which is used by pcm1792 in DSD mode. I haven't yet fully understood why it can increase signal amplitude without degradation of THD+N. It can magically boost the signal. S becomes large by analog FIR while THD+N is intact, where you automatically have a better performance like the pic1. The 5th pic is 6taps analog FIR. Noise floor and absolute THD is almost the same as 1tap. Only the signal does increase. The 6th pic is 12taps. The magic increases only the signal again.

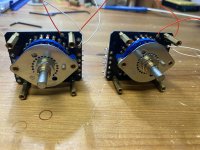

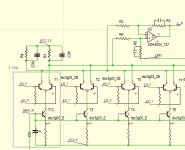

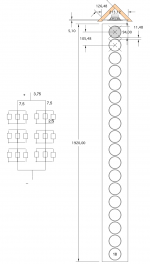

The rest of the two strategies is ECL like the 7th pic. If you replace T13 with a register, it's true ECL. T13 configured to constant current determines signal gain by T1. LN_0 and LP_0 are complementary 1bitDSM signal to switch two transistors of T1. When one is active, the other is inactive. Constant current defined by T13 passes through R4 or R1, where the digital signal(1bitDSM) is converted into an analog voltage. The significant advantage of ECL like conversion is PSRR. LN_0 and LP_0 are a dirty signal from the digital section. But the constant current of T13 is almost irrelevant to base voltage of two transistors of T1, which can result in noise-free transfer to the analog voltage across R4 or R1.

There may be several solutions to have isolation between the digital section and the analog one to have low residual noise. No DAC(1bitDSM) project usually has zero PSRR, where ends up less THD+N and prevents 1bitDSM without a DAC chip from the high-end application. If you have better isolation from the digital side, 1bitDSM can have high SNR. ECL is one of the strategies to make noDAC brilliant. ECL is easy to extend, i.e.,2taps,4taps, and more. The more, the better. The disadvantage is instability. It sometimes ends up an oscillation. I have now 24taps with moderate stability. I haven't yet fixed the oscillation problem. I'm not sure if I can have 32taps for further improvement. I'm still on the way.

The 8th pic is x128OSR in 8th order DSM. It has almost the same performance as x64. Noise shaping is, of course, better than x64. Xc6slx9 can have up to 5th order. More than 6th is done by external digital PCB(xc6slx25), which is the same one as my 5bitDSM DAC. The pulse train is transferred through an optical cable to keep high isolation. Onboard Xtal based OSC can successfully recover a clean clock(the 9th pic).