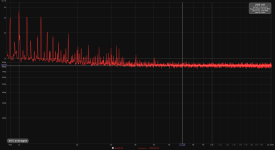

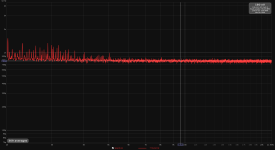

I measured a few BJTs for resulting noisefloor in the de/dienoiser circuits, mostly on the discrete supplies, as the denoiser offers a bit lower noisefloor with those. For LM317 with denoiser the regulator noise dominates.

Seems that BC817/BC807 offer a lower noisefloor than with BC337/BC327. 2N4401/2N4403 are almost on par with BC8x7.

MPSA06/MPSA56 measured the lowest noisefloor out of the whole bunch.

I made a more precise calibration for ADC with LNA attached. The input impedance of the LNA is 8k, and with a 1k resistor the error is more than 10%. I used 204R and 60R to fine tune the value that the REW calibration found. The REW calibration is done with only the ADC.

I had to go from 1.47V that REW calibration found to 1.41V. I've also done some tweaking in the LNA circuit and now my LNA's noisefloor measures around 0.47nV/sqrtHz with its input shorted.

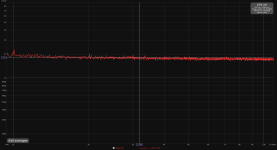

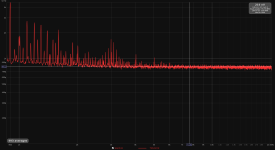

The pictures are as follows:

1. 204R resistor

2. 60R resistor

3,4. BC337 denoiser and BC3x7 dienoiser

5,6. BC817 denoiser and BC8x7 dienoiser

7,8. 2N4401 denoiser and 2N440x dienoiser

9,10. MPSA06 denoiser and MPSAx6 dienoiser

Seems that BC817/BC807 offer a lower noisefloor than with BC337/BC327. 2N4401/2N4403 are almost on par with BC8x7.

MPSA06/MPSA56 measured the lowest noisefloor out of the whole bunch.

I made a more precise calibration for ADC with LNA attached. The input impedance of the LNA is 8k, and with a 1k resistor the error is more than 10%. I used 204R and 60R to fine tune the value that the REW calibration found. The REW calibration is done with only the ADC.

I had to go from 1.47V that REW calibration found to 1.41V. I've also done some tweaking in the LNA circuit and now my LNA's noisefloor measures around 0.47nV/sqrtHz with its input shorted.

The pictures are as follows:

1. 204R resistor

2. 60R resistor

3,4. BC337 denoiser and BC3x7 dienoiser

5,6. BC817 denoiser and BC8x7 dienoiser

7,8. 2N4401 denoiser and 2N440x dienoiser

9,10. MPSA06 denoiser and MPSAx6 dienoiser

Attachments

-

204R_REW.png72.7 KB · Views: 214

204R_REW.png72.7 KB · Views: 214 -

60R_REW.png70.4 KB · Views: 191

60R_REW.png70.4 KB · Views: 191 -

nfb_bc337_denoiser.png104.5 KB · Views: 192

nfb_bc337_denoiser.png104.5 KB · Views: 192 -

nfb_bc3x7_dienoiser.png100.8 KB · Views: 196

nfb_bc3x7_dienoiser.png100.8 KB · Views: 196 -

nfb_bc817_denoiser.png110.5 KB · Views: 205

nfb_bc817_denoiser.png110.5 KB · Views: 205 -

nfb_bc8x7_dienoiser.png109.3 KB · Views: 115

nfb_bc8x7_dienoiser.png109.3 KB · Views: 115 -

nfb_2N4401_denoiser.png105.2 KB · Views: 120

nfb_2N4401_denoiser.png105.2 KB · Views: 120 -

nfb_2N440x_dienoiser.png111.1 KB · Views: 121

nfb_2N440x_dienoiser.png111.1 KB · Views: 121 -

nfb_MPSA06_denoiser.png98.6 KB · Views: 118

nfb_MPSA06_denoiser.png98.6 KB · Views: 118 -

nfb_MPSAx6_dienoiser.png96.5 KB · Views: 122

nfb_MPSAx6_dienoiser.png96.5 KB · Views: 122

I measured a few BJTs for resulting noisefloor in the de/dienoiser circuits, mostly on the discrete supplies, as the denoiser offers a bit lower noisefloor with those. For LM317 with denoiser the regulator noise dominates.

There's something I am scratching my head -- chart 2 is spot-on for the noise of a 60 Ohm resistor in and of itself, but if the noise floor of your LNA is in the vicinity of 550pV/RtHz the FFT should show the RMS'd value of DUT + measurement instrument which would be about 15% higher at these levels.

I added a 4th 2N4403 to the LNA circuit, the noise dropped to 470pV/RtHz.

Since the input impedance of the LNA is 8k, would a 1k resistor noise measure true?

Since the input impedance of the LNA is 8k, would a 1k resistor noise measure true?

There's something I am scratching my head -- chart 2 is spot-on for the noise of a 60 Ohm resistor in and of itself, but if the noise floor of your LNA is in the vicinity of 550pV/RtHz the FFT should show the RMS'd value of DUT + measurement instrument which would be about 15% higher at these levels.

So when calibrating with the LNA added to the ADC, do I need to tweak the calibration value in a way that the total measured noise is for example the noise of the 60R resistor + the noise of the LNA with shorted input? Say the LNA noise with its input shorted is 470pV/RtHz and 60R resistor noise is 985pV/RtHz, so the shown value when measuring the 60R noise should be 1.45nV/RtHz?

A low resistor will definately give wrong results as the resistor and LNA noises add up. Just follow the advice I gave on post #123.

You cannot add noise densities. Adding 2 noise sources with same noise level will end up with 3dB increase of noise.

You cannot add noise densities. Adding 2 noise sources with same noise level will end up with 3dB increase of noise.

Last edited:

So if the LNA noise is more or less than that of a 14R resistor, measuring the noise of a 14R resistor with it should result in a 3dB increase, so around 670pV/RtHz?

It may be easier to use the total noise that REW displays. So measure a resistor that adds 3dB to total noise.

Then how do I extract the true noise of the DUT from the measured value? Say that of the BC8x7 dienoiser?

The "3dB resistor" is just used to determine the LNA noise. The vertical scale calibration is a separate issue. Use a 1k resistor for calibrating the scale.

But with a 1k resistor and 8k input impedance wouldn't the measured value be more than 10% off?

I'll try later tonight to measure different resistor values until I get a 3dB increase. Thanks for the info!

Yes, measuring 1k resistor noise with 8k input impedance may not be accurate. But also your ADC may not have a flat noise floor which also has an impact on these measurements. So the results are more or less approximations.

That might be the case, but for noise measurements, 10% is nothing in absolute terms. It can make sense for comparisons, under exactly identical conditions.But with a 1k resistor and 8k input impedance wouldn't the measured value be more than 10% off?

More worrying is the effect of the noise current with 1K and a BJT input.

BJT's can achieve very low noise voltages, but suffer from non-negligible noise current

Yes, measuring 1k resistor noise with 8k input impedance may not be accurate. But also your ADC may not have a flat noise floor which also has an impact on these measurements. So the results are more or less approximations.

Yes my ADC has some LF noise. To me it looks clean from 3-4kHz and up. As long as I'm looking in that area I should be able to see what's going on.

I personally have no real use for absolute values. They don't really help me in any way. I found differential measurements to be more useful, as Elvee said, under the same conditions.

I was able to measure the noise on my LNA using the +3dB method and ended up with 8.7ohms resistance or 375pV/sqrtHz.

I was not able to use the total noise figure to do this. I had to use a noise figure for a bin that didn't have any trash in it. It came out perfectly then.

I was not able to use the total noise figure to do this. I had to use a noise figure for a bin that didn't have any trash in it. It came out perfectly then.

I was able to measure the noise on my LNA using the +3dB method and ended up with 8.7ohms resistance or 375pV/sqrtHz.

I was not able to use the total noise figure to do this. I had to use a noise figure for a bin that didn't have any trash in it. It came out perfectly then.

Well, I’m sure I can get 100 pV/rtHz noise floor if I switch off LNA power supply. 😀 😀

Using one “best” bin for determining LNA noise floor is creative but wrong method. Noise floor of your LNA is likely around 500 – 700 pV/rtHz, depending on type and number of input transistors. I.e. going from 3 to 4 input transistors will reduce noise by 15%. 375 pV/rtHz could be achieved using more than 8 low noise JFETs , but not with only 3 – 4 transistors at input.

You could use dBV value that corresponds to average noise level above 1 kHz with shorted input and then adjust variable resistor at the input till level is + 3 dBV from shorted input reading.

8 kΩ LNA input impedance is in parallel with 1 kΩ calibration resistor. So, we have 890 Ω at the input and correct noise level is 3.8 nV/rtHz instead of 4 nV/rtHz. I don’t know if current noise will dominate over voltage noise If BJT is used at the LNA input with kΩ range resistors as calibration source.

Therefore, it is good to crosscheck with 62 Ω resistor which will produce 1 nV/rtHz noise density. But, here we have another problem: LNA noise and resistor noise add up and it is very important to know LNA noise, to be able to know what reading will be correct.

Noise adds like sqrt/total noise = LNA noise ** + R noise **

I.e. if LNA noise is 600 pV/rtHz and 62 Ω resistor produces 1 nV/rtHZ, correct reading at ARTA or REW is noise density of 1.17 nv/rtHz.

By the same math method, we can extract correct DUT noise level even when measurements are taken around LNA noise floor.

Regarding the noise measurements trying to find the noise density minimum is IMO not the best approach for comparisons especially if the frequency is not always the same (e.g. 1kHz). REW also displays the total noise from 22Hz to 22kHz. This would be better figure of merit since it covers all audio frequencies and may indicate anomalies in low or high frequency noise. However this would require the LNA and the ADC to have a relatively flat noise floor and to be free of mains related noise.

Last edited:

I agree that it is hard to give generally good calibration procedure as LNA’s differ enough to require different considerations while calibrating. But, we should determine general methods as how it can be done and what should be taken in the consideration.

Otherwise, forum members will publish incomparable data which is only good for themselves as relative measurement. Meaning, mine A measurement is better than mine B by xx value, but I don’t’ know how it actually stands.

Otherwise, forum members will publish incomparable data which is only good for themselves as relative measurement. Meaning, mine A measurement is better than mine B by xx value, but I don’t’ know how it actually stands.

- Home

- Amplifiers

- Power Supplies

- Measurement data and techniques for Elvee's De-Noizator: all implementations