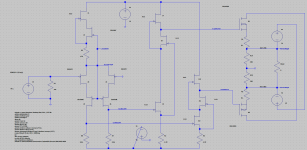

Hi, I have tried to run the last in a LTSpice schematic. simulation and has problems in transient over 0.5V in. Can you share .asc? The last .asc is not running correctly either

Most likely an incorrect simulation. In which there is no need. The design was repeated more than once, in different versions.

Hi, I have tried to run the last in a LTSpice schematic. simulation and has problems in transient over 0.5V in.

In this circuit, it is necessary to take into account the Idss (Zero-Gate Voltage Drain Current VDS = 15 V, IGS = 0) of each transistor, otherwise the readings will be incorrect.

Idss T7-T10 affects the offset of the SiC JFET gate. I have collected several amps already and they all work great.

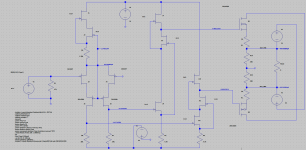

From post #200 schematic. I have 0.45 mA in R3, it is ok right? Forget output stage for a while, because I will build a different one. It seems to have a huge gain in LTP. How can I reduce this gain? With 0.1V input I exhaust voltage in, 30Vpp with clipping. Maybe I increase load of 2nd stage?

Through R3, the current should be 0.35mA + 0.35mA = 0.7mA. Resistor R3 needs to set a current of 0.35 mA through R6. The voltage across R6 is 13.65 V.

This is very interesting, we are waiting for positive results.Forget output stage for a while, because I will build a different one. It seems to have a huge gain in LTP.

Yes, the Jfet gate has an approximate amplitude of 24-30 V, but it's nice to get even higher amplitude to increase the power.

The voltage on R6 should be about 14,8 V, as in the circuit.

Attachments

Last edited:

It is because I have tried everything and I found there some progress.... How much current on R3?

J1, J2 - It is a stable current generator. I measured J113, Idss currents were from 8 mA to 18 mA.

J112 - 60 mA.

J112 - 60 mA.

Last edited:

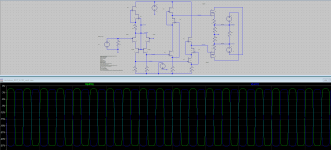

Changed rest of JFETs to J177 and now we are much better. Seems that spice models for 2sk to be wrong.

Anyway, still gain is huge, we can easily work this a full amplifier without pre. I am working to raise up amplitude, so we can have more power on the output.

Second stage is Vbe, correct? I can add more FETs, right?

BTW your LTP stages is beautiful, waiting for the nice SITs to come and I will build it.

Anyway, still gain is huge, we can easily work this a full amplifier without pre. I am working to raise up amplitude, so we can have more power on the output.

Second stage is Vbe, correct? I can add more FETs, right?

BTW your LTP stages is beautiful, waiting for the nice SITs to come and I will build it.

Have you already bought SITs? If not, it is better to try carbides. They have characteristics close to SIT.

I am working to raise up amplitude, so we can have more power on the output.

It would be very good.

P.S. 2SK182 current is regulated by changing the stabilized voltage -31V.

- Home

- Amplifiers

- Solid State

- JFET-only Circlotrons without negative feedback