👆

Any good places to read/learn about how much resistance is correct? Or is this just a matter of playing around in PSUD?

Sometime this year I have planned in my head a “universal” dual mono FW power supply using the new monoblock chassis. Idea is basically the PS you did for the M2X, twin donuts, bridge rectifiers, and CLC in chassis without heatsinks. Then umbilicals “R” to monoblocks with dual heatsinks and 2 different FW amps installed, ie right channel M2X and SissySIT in one chassis, just switch umbilical to “switch” amplifiers. In amp chassis do a final C stage with screw top can Caps with paralleled motor run caps. So between PS chassis and amp chassis PS is CLCRC.

Any good places to read/learn about how much resistance is correct? Or is this just a matter of playing around in PSUD?

Sometime this year I have planned in my head a “universal” dual mono FW power supply using the new monoblock chassis. Idea is basically the PS you did for the M2X, twin donuts, bridge rectifiers, and CLC in chassis without heatsinks. Then umbilicals “R” to monoblocks with dual heatsinks and 2 different FW amps installed, ie right channel M2X and SissySIT in one chassis, just switch umbilical to “switch” amplifiers. In amp chassis do a final C stage with screw top can Caps with paralleled motor run caps. So between PS chassis and amp chassis PS is CLCRC.

Of course, It´s just a simple model of a CLCRC power supply. Just run the simulation and look at the voltage after the choke. In the end I just built it like that with the ringing and thought oh well maybe the soft start before the transformer and transformer resistance will also help. It works very well - not sure if I measured the ringing or the absence thereof. Hmm I could have a look one of these days.but if you still have the .asc file you used for this, would you mind sharing it.

Attachments

Thanks for your replies

Paralelling sound like a good solution with regards to lower dc resistance. Thanks.

The size of the resistor to be determined in LTspice?

That's a beutiful build for ZeroWAF, he is a lucky guy.

4.7mH - 2A - 0.15Ω , do you have any series or parallel resistor with these?

You are the choke guy 😉 I'm trying to learn.

Is the 2A rating for DC saturation only?

If you run this at 1.7A and impose a 1A peak to peak AC current,

will there be no saturation for AC?

Thanks a lot 🙂

I had a quick play with this. Looks like less DCR in the choke gives more ringing and vice versa.

Looks like a small 70mΩ resistor in parallel with the choke kills the rest of the ringing?

More thoughts on this is welcome.

Will have to have a further play with this, thanks again

I used the Hammond 154B chokes (3mH, 1.5A DC) with 2.2 Ohm, 3W resistors in parallel with the chokes.

Paralelling sound like a good solution with regards to lower dc resistance. Thanks.

The size of the resistor to be determined in LTspice?

you can see example of dual mono CLC PSU in latest posting in LuDEF thread

That's a beutiful build for ZeroWAF, he is a lucky guy.

4.7mH - 2A - 0.15Ω , do you have any series or parallel resistor with these?

You are the choke guy 😉 I'm trying to learn.

Is the 2A rating for DC saturation only?

If you run this at 1.7A and impose a 1A peak to peak AC current,

will there be no saturation for AC?

Of course, It´s just a simple model of a CLCRC power supply

Thanks a lot 🙂

I had a quick play with this. Looks like less DCR in the choke gives more ringing and vice versa.

Looks like a small 70mΩ resistor in parallel with the choke kills the rest of the ringing?

More thoughts on this is welcome.

Will have to have a further play with this, thanks again

with setup shown in previously posted link, there is no ringing at all

I did made some preceding sims with PSUD, confirmed with scope

I did made some preceding sims with PSUD, confirmed with scope

Is the ringing we are talking about is only on startup?

If so I guess a slow start would take care of that.

If so I guess a slow start would take care of that.

With this thread popping up, it reminds me, I had the thought of CLC in the back of my mind not long ago.

As you do, I got a bit carried away looking through the Hammond models to see what might be - from a specs basis - the optimum one there for the purpose and saw the 190M10

https://www.hammfg.com/part/195M10

I thought it had the highest inductance at 20mH balanced with lowest DCR at 0.013 ohms. Would be good to hear what others think, large, heavy and expensive yes, but would the logic be correct?

Whether it would make a difference past a more sensible choke, that's another thing as well...

As you do, I got a bit carried away looking through the Hammond models to see what might be - from a specs basis - the optimum one there for the purpose and saw the 190M10

https://www.hammfg.com/part/195M10

I thought it had the highest inductance at 20mH balanced with lowest DCR at 0.013 ohms. Would be good to hear what others think, large, heavy and expensive yes, but would the logic be correct?

Whether it would make a difference past a more sensible choke, that's another thing as well...

My limited understanding is that every rapid change in current draw might cause ringing. The biggest change of course is on startup hence a soft start should help. I wass worried the ringing could raise the voltage to unsafe levels for my JFETs. As a class A amp has a constant current draw I didn´t worry much about ripple during operation.Is the ringing we are talking about is only on startup?

Yes, we are interested if there is any ringing at CLC output on load change, or what transient response looks like. I’ve set up test case with CLC as 33 mF – 25 mH/0.9 Ω – 33 mF. As chokes were used secondaries of two smaller transformers. As load was used current sink governed by signal generator (my standard test equipment for power supplies). Load was 5 A peak to peak at 1 kHz and limited rise time to stay within possible speed of change for the real audio signal.My limited understanding is that every rapid change in current draw might cause ringing.

Test reveals that there is absolutely no ringing and response is clean. Response using 65 mH/0.3 Ω was the same (ripple was cut by half).

Most interesting fact may be that CLC transient response was exactly the same as with CRC consisting of 33 mF – 0.33 Ω – 33 mF.

My conclusion is that with choke we get much lower ripple and less voltage sag at very low frequency load. But, from several hundred Hz and up, performance of PS completely depends on output capacitor and is exactly the same for CRC or CLC.

Most A class amps have constant current draw only without signal. When playing music, current change (PS load) is proportional to input signal.As a class A amp has a constant current draw I didn´t worry much about ripple during operation.

You got me thinking there - thank you also for the measurements.Most A class amps have constant current draw only without signal. When playing music, current change (PS load) is proportional to input signal.

On the positive half cycle the plus rail has more draw and the negative rail less draw and the other ways round on the negative cycle. With a balanced class A monoblock -like I use- the current draw of both "channels" summed should just cancel each other to be constant. The more current draw during the positive half cycle on the positive rail from the one channel above gets equalised by the less current on the positive rail from the inverted channel. Of course I could be wrong 😊

Edit - Summary:

- Class A or A/B: the rail currents follows the signal and ringing could be an issue on transients

- balanced Class A: the rail currents in sum for both channels is constant and ringing only might occur on power up

Last edited:

Seems right. 👍Edit - Summary:

- Class A or A/B: the rail currents follows the signal and ringing could be an issue on transients

- balanced Class A: the rail currents in sum for both channels is constant and ringing only might occur on power up

Just to clarify, I checked as well pure square wave load with 1 us rise time and frequency up to 20 kHz. Response was always clean. At higher frequency, response changed from sawtooth to pure square wave, with smaller peak to peak value. That is expected as output capacitor is able to sustain its voltage for this short period of high load.

This is like shorting the choke and you will have higher ripple.Looks like a small 70mΩ resistor in parallel with the choke kills the rest of the ringing?

I´m afraid this makes another oscillator and higher ripple.I used a 1000uf onboard bypass capacitor to reduce ringing in my CLC supply.

Ther more mH the lower the ripple but also more ringing. I don´t know how bad the ringig is - it seems to have a frequency below 10 Hz with typical values. With a little damping in form of a higher coil resistance (0,013 Ohms seems quite low) or series resistor one can get rid of the ringing and get lower ripple at the cost of a higher voltage drop. If I had to do it again, I would choose a higher transformer secondary and install that 0R2 Ohms resistor.I thought it had the highest inductance at 20mH balanced with lowest DCR at 0.013 ohms. Would be good to hear what others think, large, heavy and expensive yes, but would the logic be correct?

This is like shorting the choke and you will have higher ripple.

Ahhh 🙄 of course

I'm just trying to learn about theese chokes.

In electronics as in other parts of life there seems to always be a but of compromises 😏

Thanks ozorfis, that's good to know. I guess this is something which would show in PSUD2, I'll have a play around with it tomorrow. I just need to understand those graphs better 😀Ther more mH the lower the ripple but also more ringing. I don´t know how bad the ringig is - it seems to have a frequency below 10 Hz with typical values. With a little damping in form of a higher coil resistance (0,013 Ohms seems quite low) or series resistor one can get rid of the ringing and get lower ripple at the cost of a higher voltage drop. If I had to do it again, I would choose a higher transformer secondary and install that 0R2 Ohms resistor.

I’ve set up test case with CLC as 33 mF – 25 mH/0.9 Ω – 33 mF..... Response using 65 mH/0.3 Ω was the same (ripple was cut by half).

Very interesting.

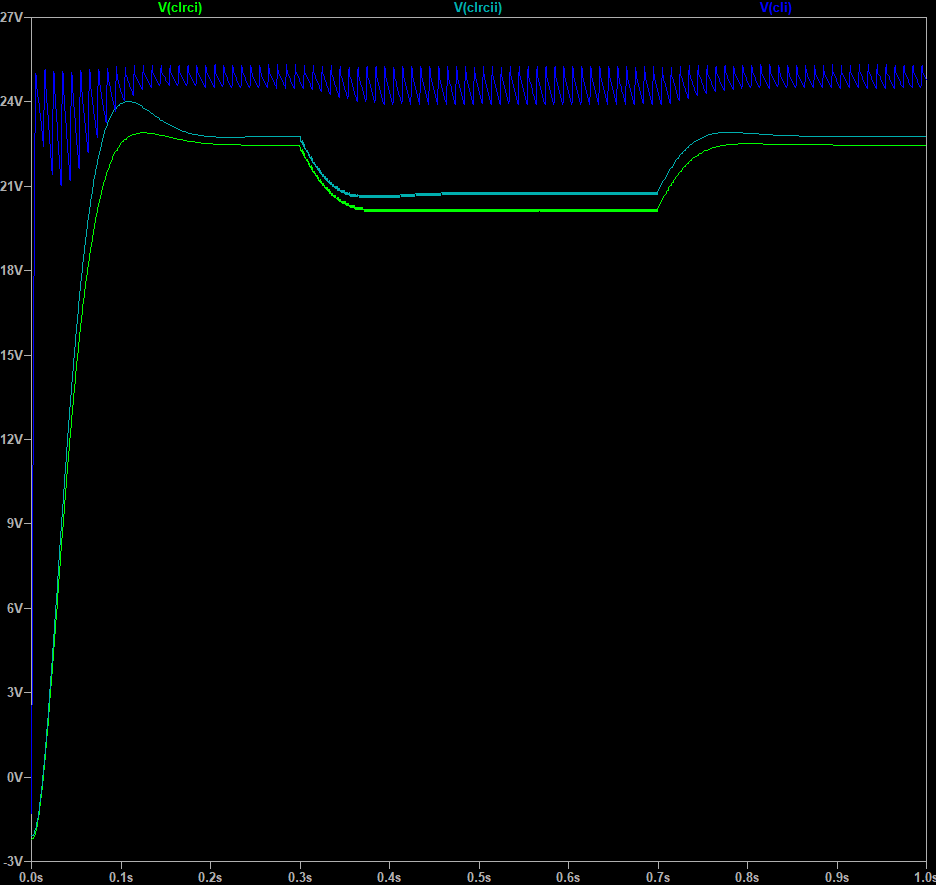

Here is how it sims in LTspice

green= 65mH-0.3Ω

cyan= 20mH-0.013Ω (Hammond 195M10)

red=20mH-0.9Ω

Here is how it sims with additional series resistor

green= 65mH-0.3Ω +1.6Ω

cyan= 20mH-0.013Ω +1Ω (Hammond 195M10)

red= 20mH-0.9Ω +0.15Ω

The red=20mH-0.9Ω seem to correspond to what PRR said here

Try to aim for 20mH-100mH, near 1 Ohm. (Less will ring, more is distressing voltage drop.)

I don't know what i'm looking at here.

If it is only on startup a slow start would take care of that.

But, what effect it would have on playing music?

Maybe it does not matter?

Test reveals that there is absolutely no ringing and response is clean....... Most interesting fact may be that CLC transient response was exactly the same as with CRC consisting of 33 mF – 0.33 Ω – 33 mF.

Here is how my sim was set up.

I was using LT4320 as that is what I will use in my new psu.

Very interesting.

Here is how it sims in LTspice

green= 65mH-0.3Ω

cyan= 20mH-0.013Ω (Hammond 195M10)

red=20mH-0.9Ω

View attachment 1047916

Here is how it sims with additional series resistor

green= 65mH-0.3Ω +1.6Ω

cyan= 20mH-0.013Ω +1Ω (Hammond 195M10)

red= 20mH-0.9Ω +0.15Ω

View attachment 1047921

The red=20mH-0.9Ω seem to correspond to what PRR said here

I don't know what i'm looking at here.

If it is only on startup a slow start would take care of that.

But, what effect it would have on playing music?

Maybe it does not matter?

Nice post! You show very clearly that more inductance leads to more ringing, and that more inductance requires more series resistance to suppress the ringing. I've been modelling in PSUD2 recently, and drawn the same conclusions.

The big question is how much this matters. I wish I knew! I'd guess that varying current draw may provoke some ringing, so it probably isn't just a start-up issue. No? But then the next question is whether that matters - if the amplifier has decent rejection of ripple at 100 or 120 Hz, how well can it reject ringing at around 20 Hz, or at subsonic frequencies?

One thing that seems clear, though, is that additional series resistance in the PSU is undesirable - it will make the rail voltage less 'stiff' with varying current draw. In fact I'm wondering if the best CLC supply is one with just a very small amount of inductance. A mere 1 mH will reduce ripple substantially compared with CRC, but require no more series resistance. Win win?

My test only confirms that CLC with values as tested, has perfectly clean output with no ringing caused by the sudden load change. Startup behavior is a different matter. Your simulation covers startup and static load situation. Though, I believe that startup voltage will not peak at such high values as predicted by sim. If you already haven’t, set inductor max. current to 3A and add some parasitic capacitance to inductor parameters (100 -300 pF). 33 mF capacitors should have 14 mΩ ESR and some ESL, like 10 nH.

Instead of constant current load, use pulse setting with, in example, something like I1 = 1A, I2 = 5A, Tdelay 200 ms, Trise & Tfall 5 us, Ton 500 us, period 1 ms and Ncycles = 1000. This would show response on transient load, similar to my test.

Actual test was performed with LT4320 PS board (prasi’s LT4320 CRC boards). 🙂

It’s still on the bench but I don’t have any low DCR/several mH choke to check how that combination behaves.

Instead of constant current load, use pulse setting with, in example, something like I1 = 1A, I2 = 5A, Tdelay 200 ms, Trise & Tfall 5 us, Ton 500 us, period 1 ms and Ncycles = 1000. This would show response on transient load, similar to my test.

Actual test was performed with LT4320 PS board (prasi’s LT4320 CRC boards). 🙂

It’s still on the bench but I don’t have any low DCR/several mH choke to check how that combination behaves.

ianbo, thanks

I have been wondering about and simming the small ones too

I will post when I find some more playtime 🙂

tombo56

Thank you very much for you inputs here.

Both you and Zen Mod have not found ringing on scops and that counts for more than sims and is valuable info.

I will do a bit more simming before I call it quits.

I had inductor max. current to 5A.

I have now changed it to 3A and added 200pF.

It did not make a lot of difference on the startup peak voltage.

I had and have 18mΩ ESR wich is the value of 33mF CDE SLPX and guestimated 20nH.

Thanks for the tip on pulse loading, I've set it to PULSE(1A 5A 300ms 5us 5us 500us 1ms 400)

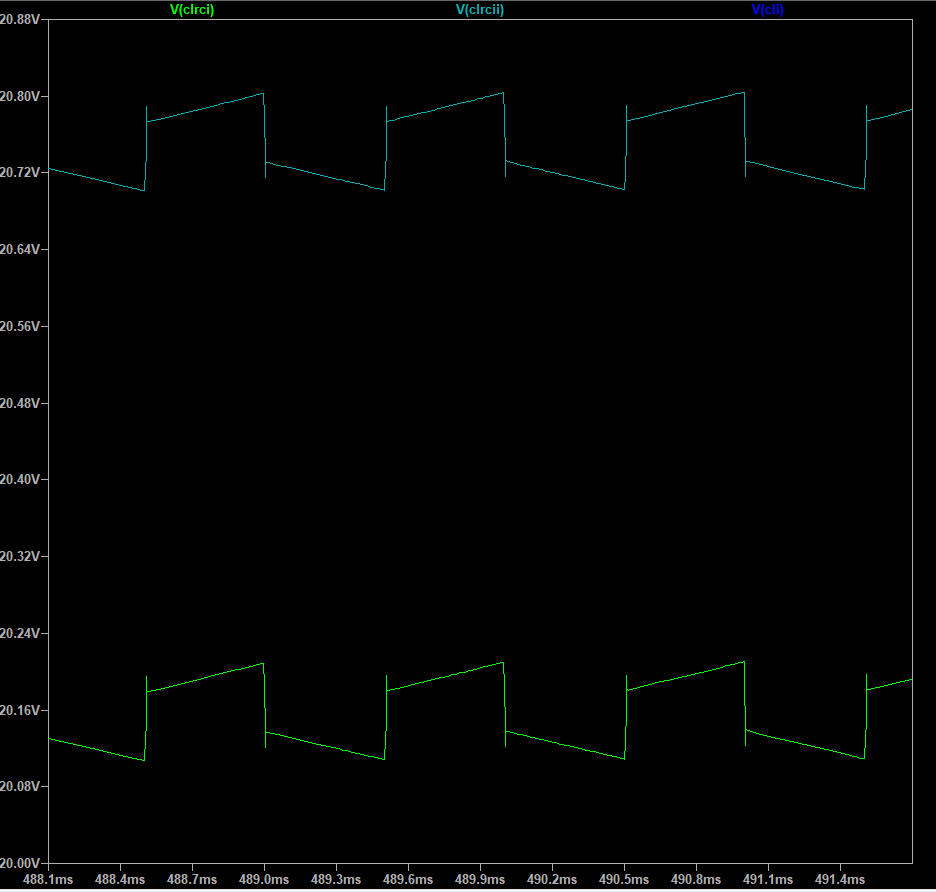

cyan is for your 20mH 0.9Ω

green is for the same, but with 0.15Ω in serie.

blue is the ripple on choke input

It does sag a bit

This is a close up of the pulses on the supply line

sims like I need to find a lot more play time 😏

If I find something more of interes I'll post some more

I have been wondering about and simming the small ones too

I will post when I find some more playtime 🙂

tombo56

Thank you very much for you inputs here.

Both you and Zen Mod have not found ringing on scops and that counts for more than sims and is valuable info.

I will do a bit more simming before I call it quits.

I had inductor max. current to 5A.

I have now changed it to 3A and added 200pF.

It did not make a lot of difference on the startup peak voltage.

I had and have 18mΩ ESR wich is the value of 33mF CDE SLPX and guestimated 20nH.

Thanks for the tip on pulse loading, I've set it to PULSE(1A 5A 300ms 5us 5us 500us 1ms 400)

cyan is for your 20mH 0.9Ω

green is for the same, but with 0.15Ω in serie.

blue is the ripple on choke input

It does sag a bit

This is a close up of the pulses on the supply line

sims like I need to find a lot more play time 😏

If I find something more of interes I'll post some more

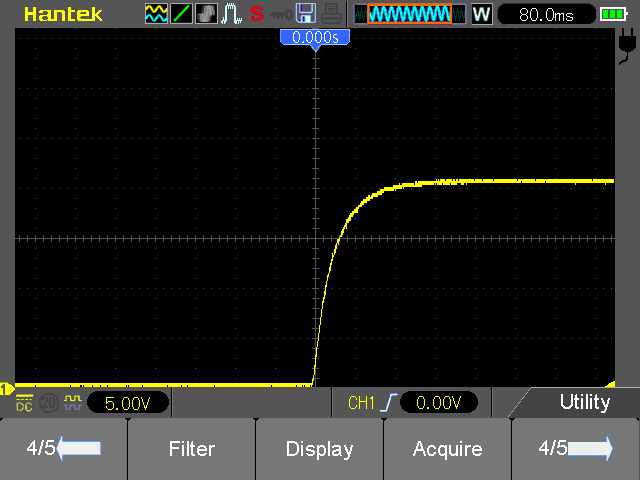

For comparison between sim and real circuit, here is startup voltage waveform of 33 mF – 25 mH/0.9 Ω – 33 mF CLC supplied by 300 VA transformer. It’s evident that there is no voltage overshot. Transformer was directly plugged to mains (no soft start).

Simulation has ideal voltage sources, so it would be better to add supply internal resistance as 0.1 to 0.2 Ω.

Simulation has ideal voltage sources, so it would be better to add supply internal resistance as 0.1 to 0.2 Ω.

- Home

- Amplifiers

- Pass Labs

- CLC vs. CRC