This (bridged T bal) is for DEM 16/17.

I compared to the L-pad and this one giving better shape and less spikes on the edges.

With the pins 16 and 17 input circuit.

You need a fairly complete circuit for the oscillator sim to make sense.

My sims suggest we get nearly a sinewave at the input anyway. Of course, I simulate the internal 470pf cap for non-A chips.

You are in effect feeding the Emitters of flip-flop like it was done before IC's. A lot of design choices in the TDA1541 are down to the silicon tech "back then", mandating almost "NPN only" (also visible inside the contemporary NE5534/32).

Thor

Ok, conclusion of the Digital input attenuation investigation:

If we use a John Brown style resistor attenuator scaled to match Cin of TDA1541 vs nothing we get the results above (6.144MHz - BCK).

I model the substrate as 32 Ohm resistor, as this is my best guess, but we really do not know what it is. Same for values in the input circuit and values, all (well) educated guesses.

Anyway, with full 3.3V CMOS drive we see capacitive saturation effects in the differential pair and nearly 800mV PP spikes on the substrate.

Just the resistive attenuator and the (simulated) slow transistors large input capacitance create sufficient slower edges that we get a clean (if delayed - hence this is needed on all inputs) that our PP noise is reduced to ~47mV PP with slower edges - so an at least 24dB lower noise level and possibly less coupling through slow edges.

I tried a lot of of alternatives, non really perform significantly different or better at least in the sim.

Despite being set as 10MHz lowpass (-3dB) the circuit in the sim at least works fine at 12.288MHz. If there are problems getting a "lock" reduce resistors. But the MV Audio Labs circuit with 680R/47pF for 3.3V and 384k gives an ~ 5MHz lowpass!

So for the KISS principle I guess three resistors per line it is. That's it really. No need for anything more complex.

I think that wraps up everything we can do around the TDA1541.

Power supplies, DEM decoupling, DEM Clocking and I'/U conversion.

Thor

If we use a John Brown style resistor attenuator scaled to match Cin of TDA1541 vs nothing we get the results above (6.144MHz - BCK).

I model the substrate as 32 Ohm resistor, as this is my best guess, but we really do not know what it is. Same for values in the input circuit and values, all (well) educated guesses.

Anyway, with full 3.3V CMOS drive we see capacitive saturation effects in the differential pair and nearly 800mV PP spikes on the substrate.

Just the resistive attenuator and the (simulated) slow transistors large input capacitance create sufficient slower edges that we get a clean (if delayed - hence this is needed on all inputs) that our PP noise is reduced to ~47mV PP with slower edges - so an at least 24dB lower noise level and possibly less coupling through slow edges.

I tried a lot of of alternatives, non really perform significantly different or better at least in the sim.

Despite being set as 10MHz lowpass (-3dB) the circuit in the sim at least works fine at 12.288MHz. If there are problems getting a "lock" reduce resistors. But the MV Audio Labs circuit with 680R/47pF for 3.3V and 384k gives an ~ 5MHz lowpass!

So for the KISS principle I guess three resistors per line it is. That's it really. No need for anything more complex.

I think that wraps up everything we can do around the TDA1541.

Power supplies, DEM decoupling, DEM Clocking and I'/U conversion.

Thor

Di d You said Sine wave ?My sims suggest we get nearly a sinewave at the input anyway

👽

Ok, conclusion of the Digital input attenuation investigation . . . .

Thor

As always - very informative. Excellent simulation👍

I recall reducing the digital input voltage swing to the lowly 180mVpp + 1.4 Vdc bias (two series-coupled SMD diodes glued on top of TDA) with no drama, at least with the cpl of TDA chips I had on hand 'a la HSH.

I also reduced the digital input tr=20ns, with no conversion issues.

SR reduction modification, along with Mclk-derived, DEM clock-injection gave very positive sonic results, further relaxing the already relaxed & effortless sound of TDA1541a.

Last edited:

I used the same FF with Q-Q outputs (176.4KHz) and pins 16 and 17 input circuit.You need a fairly complete circuit for the oscillator sim to make sense.

Di d You said Sine wave ?

👽

Nearly. I redid some sim's triangular...

I used the same FF with Q-Q outputs (176.4KHz) and pins 16 and 17 input circuit.

Pin 16/17 are the emitters of a pair of cross coupled NPN transistors. They sit on current sinks. This is not in any traditional sense an input circuit. Here the whole circuit of the DEM oscillator and shift registers, oscillator highlighted:

My simulation uses a pretty much verbatim copy of the oscillator with 2N3904 transistors as model.

T4/T6 in the real IC are not loaded by resistors but by differential the spikes are a result of the resistor load, as is to a degree the slow rise time (miller effect) I just added the resistors to have something to see.

You can see that the drive signal (voltage) is pretty rounded. This is at 1.536MHz DEM Clock above. Below 176.4k:

And here 768k:

Input impedance on Pin 16/17 is low, but collector current dependent and forms a dynamic high pass with the coupling capacitors (1nF), but as my chip is non-A I include the 470pf on board capacitor.

The emitter coupled oscillator interacts with the series resistors and they in effect inject current into the collectors of these transistors directly. Excessive drive will saturate the transistor and cause trouble.

It's complex.

But simply speaking, the drive signal should be as low as possible (remember, it's current based) needed to get a stable clock. You need a scope but you will know when the clock is not locked. The trace at 16/17 will be unstable.

Thor

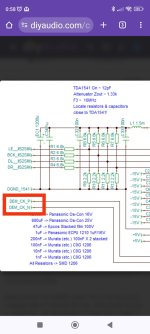

Ok, so here my take on a "TDA1541(A)" Core (module) incorporating all my conclusion on what is the best course of action:

Remember, most parts are SMD and will be placed below the TDA1541 (underside of PCB).

There should be 4 - layers and planes under the PCB.

DEM Clock should be synchronised and 4 X WCK to use the lowest possible frequency that uses a 4 DEM system cycles.

Bottom layers with AGND and -15V & +5V planes that are linked under the TDA1541 by C25 - C28 (located between Pin 1 - 3 and Pin 26 - 28 pointing in line with the IC body - linking Pin 15 - Pin 28).

Top layers with DGND and +5V planes.

Thor

Remember, most parts are SMD and will be placed below the TDA1541 (underside of PCB).

There should be 4 - layers and planes under the PCB.

DEM Clock should be synchronised and 4 X WCK to use the lowest possible frequency that uses a 4 DEM system cycles.

Bottom layers with AGND and -15V & +5V planes that are linked under the TDA1541 by C25 - C28 (located between Pin 1 - 3 and Pin 26 - 28 pointing in line with the IC body - linking Pin 15 - Pin 28).

Top layers with DGND and +5V planes.

Thor

Hi

I think that these 2 x resistors from DEM pins 16 and 17 R14, R15 connected to -15V. Are very useful to be on PCB. Anyway i will planned to put them. Once on on some experimental TDA1540 and 1541A bards I put the same way connected resistors in the TDA1540 external Cdem it was i the standard datasheet value. After connected 2 x 20K resistors to -18V Frequency of the sawtooth rised up to almost exact 176.4KHz. these 2 x 20K was for about 190uA to 200uA current trough each, connected to -18V from dem pins.

Before connection of these 2 resistors Fdem was about 140KHz if i am remember well?

.

(And it is so small to imposiposibile probability that the tollerance of Cdm between the pins are for 176.4KHz, actually it is most likely that it was for F without 2 x R... But these added R to -18V somehow made a "correction"...)

.

I thin that I posted this befeore-after photo on the topic few pages ago?

.

After that i tried the same with TDA1541A but the values for the about the same current in [uA] was significantly lower about 12K each, I think, and unfortunatley I didnt measure the pins on TDA1541A 🙁

.

I tried it based on Johns idea and it was called it free running dem. But he used it without external oscilator. I think that it will give good results even with external osc, and it is a must parts to be on PCB. At least it could be conn./disconn. with jumpers, (i did that way for listening tests) and it was obvious better sound with the presence of these Rs.

But I think that for the TDA1541A the values should be higher about 10-12K. With 6.8K of Johns values the current is high for my opinion...

.

If I found some wroted notes about this live test i will post... Cheers

.

I think that these 2 x resistors from DEM pins 16 and 17 R14, R15 connected to -15V. Are very useful to be on PCB. Anyway i will planned to put them. Once on on some experimental TDA1540 and 1541A bards I put the same way connected resistors in the TDA1540 external Cdem it was i the standard datasheet value. After connected 2 x 20K resistors to -18V Frequency of the sawtooth rised up to almost exact 176.4KHz. these 2 x 20K was for about 190uA to 200uA current trough each, connected to -18V from dem pins.

Before connection of these 2 resistors Fdem was about 140KHz if i am remember well?

.

(And it is so small to imposiposibile probability that the tollerance of Cdm between the pins are for 176.4KHz, actually it is most likely that it was for F without 2 x R... But these added R to -18V somehow made a "correction"...)

.

I thin that I posted this befeore-after photo on the topic few pages ago?

.

After that i tried the same with TDA1541A but the values for the about the same current in [uA] was significantly lower about 12K each, I think, and unfortunatley I didnt measure the pins on TDA1541A 🙁

.

I tried it based on Johns idea and it was called it free running dem. But he used it without external oscilator. I think that it will give good results even with external osc, and it is a must parts to be on PCB. At least it could be conn./disconn. with jumpers, (i did that way for listening tests) and it was obvious better sound with the presence of these Rs.

But I think that for the TDA1541A the values should be higher about 10-12K. With 6.8K of Johns values the current is high for my opinion...

.

If I found some wroted notes about this live test i will post... Cheers

.

Last edited:

One Q about the different F

I think that used the same BJT Q model for the same circuit wit "bridged T balanced " netMy simulation uses a pretty much verbatim copy of the oscillator with 2N3904 transistors as model.

Hi Thor, please can you explane were we have to connect the two PIN in red square showed in picture?

Differential DEM clock. As now all other inputs are high level, I guess we should include the DEM circuit.

Some small corrections for consistency...

DEM Clocking & IIS2SIM conversion (using ALIExpress Module):

Here the matching power supply (off mains AC), based around using supercapacitors. It can be replaced with others shown previously or whatever you like.

And the intended analogue stage circuit (one channel):

Note all this theoretical/simulator and may need adjustment in reality, but the principles are "sound" (pun intended).

R13 is 330R (or 330K R?)

It is what I call a Placeholder. The real circuit will likely need experimentation to get right, simulations only get you so far.

So in the end there may not be a resistor there at all.

VEE1 to AGND: no 0.1 uF // to C16 1uF ?

In my case the highest frequency for DEM is ~ 1.5MHz, so I think the film capacitor will do ok by itself. The VHF glitches only affect the DEM Pin's,

AGND to VEE1 : is C24 should be added as C16 is there at pin -15 ? No 0.1 uF at AGND pin to VEE1 layer ?

The idea is to have two capacitors and the two coupled planes. It is possible to locate one 1206/1210 capacitor per pin, paralleling 1210 especisally becomes dicey.

You can see the same on the pin's 14/28 for DGND & +5V.

So

+5V -> DGND = 2 X 100nF C0G, 2X 1uF Film, 4 X 1,200uF Os-Con

+5V -> 15V = 4 X 100nF C0G, 2X 1uF Film, 2 X 47uF Film, 1 X 680uF Os-Con

-15V -> AGND = 2 X 1uF Film, 4 X 1,200uF Os-Con

Plus the Supercapacitors in my case.

Thor

Excellent! Including the AC DEM coupling.Ok, so here my take on a "TDA1541(A)" Core (module) incorporating all my conclusion on what is the best course of action:

View attachment 1351839

Remember, most parts are SMD and will be placed below the TDA1541 (underside of PCB).

There should be 4 - layers and planes under the PCB.

DEM Clock should be synchronised and 4 X WCK to use the lowest possible frequency that uses a 4 DEM system cycles.

Bottom layers with AGND and -15V & +5V planes that are linked under the TDA1541 by C25 - C28 (located between Pin 1 - 3 and Pin 26 - 28 pointing in line with the IC body - linking Pin 15 - Pin 28).

Top layers with DGND and +5V planes.

Thor

Very nice!

@ThorstenL , @Zoran and all, thank you very much for the enormous work you do for the community! Are you already thinking of something for IC chip receiver + PSU + input selector? For this purpose, a balanced LVDS i2s input will also be provided (for the pin in, can the PS Audio standard be taken as a reference?) just to name one at random. It would also be interesting to have the input signal format information displayed on the front panel display (but maybe it's better to take foot off the accelerator now)🤟😛

Antonio

@ThorstenL , @Zoran and all, thank you very much for the enormous work you do for the community! Are you already thinking of something for IC chip receiver + PSU + input selector? For this purpose, a balanced LVDS i2s input will also be provided (for the pin in, can the PS Audio standard be taken as a reference?) just to name one at random. It would also be interesting to have the input signal format information displayed on the front panel display (but maybe it's better to take foot off the accelerator now)🤟😛

Antonio

Hi, what is the Bck speed of the I2toSim device at input, please ?

Is it Philips : Bit depth x Fs x2 ? And when going out is itBit depth x Fs x 1 (because sim mode) ?

Is it cleaner to make the Sim mode with shift registers ? Or we do not care, rise time being perhaps high enough (jitter not a big problem with async ?

Is it Philips : Bit depth x Fs x2 ? And when going out is itBit depth x Fs x 1 (because sim mode) ?

Is it cleaner to make the Sim mode with shift registers ? Or we do not care, rise time being perhaps high enough (jitter not a big problem with async ?

Very nice!

@ThorstenL , @Zoran and all, thank you very much for the enormous work you do for the community! Are you already thinking of something for IC chip receiver + PSU + input selector?

If you ask me, 74F125 Tristate buffers for BCK, LRCK and DATA and RF relays (e.g. Omron G6K-2F-RF or Omron G6K-2F wrapped in copper foil) for MCK.

Simply parallel as many tri-state output buffers as needed, 74F125 contains 4 buffers with individual enables.

Or just relays all the way.

For this purpose, a balanced LVDS i2s input will also be provided (for the pin in, can the PS Audio standard be taken as a reference?) just to name one at random.

China AliExpress now has many "Input" modules (output too) on Amanero footprint, readymade. I know of USB, SPDIF (usually AKM Chip), BT (with USB) and I2SonHDMI off hand. Others exist.

So I would just put multiple Amanero footprints (say 3) and suitable multiplexing.

And one could of course make Amanero footprint compatible designs for many input options DIY, if one is so inclinced.

It would also be interesting to have the input signal format information displayed on the front panel display

Well, for TDA1541 the signal format will be PCM - no DSD, MQA et al.

Sample rate - you can get an OLED from China that run's of LRCK. Give it it's own power transformer with shield, OLED's are noisy as hell, they really don't have a place in quality audio gear otherwise.

Thor

Hi, what is the Bck speed of the I2toSim device at input, please ?

IIS standard.

That is commonly 64 X WCK for USB modules and most SPDIF receivers, as we now pretty much have 24 Bit everything and doing 48 X WCK is a bit involved, so usually it's either 32 X WCK (source in 16 Bit mode) or 64 X WCK (source in > 16 Bit mode, unused bits are zero stuffed).

And when going out is itBit depth x Fs x 1 (because sim mode) ?

I have received the modules but not fired them up. No idea what the output is.

Is it cleaner to make the Sim mode with shift registers ?

Well, you have 100% control over what goes on. And there is no software/firmware to be buggy.

Thor

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A