Yes off course - but that is what is somehow unclear...

The 7.5V is from measured results.

And beautifully, it's halfway between AGND and -15V, so the voltage is the same, no matter where we return this capacitor (others vary).

The way the TDA1541 works, there is a cascode Darlington transistor, with an emitter resistor in the kOhm range, after this a capacitor to somewhere and a current input from the DEM switching (see internal schematics posted multiple times).

This combination of transistor, resistor and capacitor is the actual current sink, not the DEM system.

The DEM system forces a current into this circuit, which is averaged by the capacitor. The capacitor voltage depends on the Darlington transistor Vbe and the emitter resistor.

The DEM part makes dll of this self adjusting and compensatedvaganist (slow) environmental temperature drift.

It's utter genius and finally understanding how the TDA1541 really works gave me a new appreciation of what BJT's can do.

Thor

I persume that Iref from the picture abowe

is the same = 4mA

No, Iref is the current the DEM circuit injects into the pin.

So it depends on the pin and is 2mA for MSB.

As we have a geometric progression after the MSB, we only really need to calculate the MSB Capacitor.

As said, the +/-5% are based on RJvdP's writings about the 4-way bipolar current splitter

For TDA1541 we have three of these 4-way current splitters cascaded. Each collector output from the splitter is 1/4 Iin +/-5%.

The first current splitter receives nominally 4mA and outputs 4 x 1mA +/-5% but the sum of all currents must be equal to Iin.

Obviously 5% tolerance is useless fir a precision DAC, so a switching matrix is present, which switches the 4 currents to 3 outputs so that on output averages to Iin/2 and the other two to Iin/4.

So we get 2mA for MSB, 1mA on the NSB and 1mA is passed as Iin to next cell.

So each time the DEM system switches state the absolutely worst case current step is from -5% to +5% or the reverse, so a current step of 10% from the nominal current at this pin.

As mentioned, if make sure to have all four DEM states within one audio sample at least once, any error becomes a DC offset.

Is that more clear?

Thor

Sorry I meant Iref = 4mA dcNo, Iref is the current the DEM circuit injects into the pin.

from the schematic of dem pins part

As common DC current, sourced to -15V (-18V)

.

Somehow I thin from other lined parameters that these +-5% of tol. for TDA1540

are +-15% for TDA1541A ?

.

Are the 7.5Vac p-p "across" the DEM Cmsb is vaid for a other dem pin Cs?

And is there some chance for same 7.5V p-p for TDA1540?

Thanks

.

Last edited:

Sorry I meant Iref = 4mA dc

I did not use Iref in the datasheet sense, but in the sense of the current that enters the specific active divider in question.

Somehow I thin from other lined parameters that these +-5% of tol. for TDA1540

are +-15% for TDA1541A ?

It is a different current and tolerance than I mention.

But if the process for TDA1541(A) required a more relaxed tolerance on everything, who knows. You can re-calculate with 30% ripple instead of 10%... Or just triple the values I mention.

Are the 7.5Vac p-p "across" the DEM Cmsb is vaid for a other dem pin Cs?

It is not 7.5V AC, it is 7.5V DC. And no, other pins vary:

And is there some chance for same 7.5V p-p for TDA1540?

No idea, I do not consider TDA1540 at all in what I do.

Thor

-2 mA offset current compensation

2.5 k resistor to +5 V is a bad idea

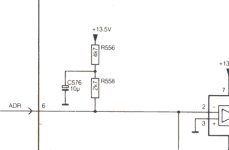

In my test setup I used LM2940T-5 voltage regulator. I found that the noise at the analog output is horrible. It is because the noise voltage of the regulator is 150 uVrms, that means 60 nA on the 2.5 k resistor. This is the amount of the LSB current. Philips CD960 / Marantz CD-94 used a filtering as per the attached picture. I used a CCS made of a 2N3819 jFET.

2.5 k resistor to +5 V is a bad idea

In my test setup I used LM2940T-5 voltage regulator. I found that the noise at the analog output is horrible. It is because the noise voltage of the regulator is 150 uVrms, that means 60 nA on the 2.5 k resistor. This is the amount of the LSB current. Philips CD960 / Marantz CD-94 used a filtering as per the attached picture. I used a CCS made of a 2N3819 jFET.

Attachments

Last edited:

Correct, I measured the same, within a few percent. Note the you can't measure the voltage on the decoupling pins (or on the capacitors) simply by a DMM. It is because the usual 10 Megohm input resistance of the DMM will act as a "leakage" resistor parallel with the capacitor. The voltage that you read on the instrument is not valid.

The correct method is to use a variable auxiliary voltage 0 to -10 V, and connect a null voltage indicator (electrometer, can be a DMM) between this variable voltage and the DEM capacitor pin. Then null out the indicator and measure the variable voltage.

But you don't have to measure it, others have done it 😉 .

Depends how noisy the +5V line is...

https://www.diyaudio.com/community/...ac-using-tda1541a.79452/page-452#post-7763412

In my test setup I used LM2940T-5 voltage regulator. I found that the noise at the analog output is horrible. It is because the noise voltage of the regulator is 150 uVrms, that means 60 nA on the 2.5 k resistor. This is the amount of the LSB current. Philips CD960 / Marantz CD-94 used a filtering as per the attached picture. I used a CCS made of a 2N3819 jFET.

For AMR CD-77 I did this:

1k & 1,000uF give ~0.16Hz turnover and with >100mOhm ESR for the capacitor we expect 80dB maximum noise attenuation for the supply rail noise, above ~ 1Hz - so comparable to the TDA1541 own PSRR. so our 20uV TL431 noise get squashed to ~ 2nV and noise cuerrnt via 1.5kOhm of ~ 1.33pA.

As alternative for the "KISS" crowd.

Could even use 510R & 2,200uF shared between channels. for a total of 3 resistors and one cap.

It is however better to let the I/U converter absorb the current and return it to +5V (together with signal current).

Incidentally, it also reveals the supply decoupling combo I used, 47uF/16V Os-Con, 10uF/50V likely X7R in 1206 or so, 0.1uF X2Y feedthrough capacitor.

Thor

It shoud be some "ac", becuse in formua for F, used AC current p-p and "2pfj" is circular so the variable of voltage shoul aloso be from the same unit pool...It is not 7.5V AC

Zworst case is = Vworst case / Iwors case

whrere Vwc is from [Vdc] and Iwc [Idc] from Iref as dc unit mA...

So it is not "Zwc" as unit persumed as Z(f)wc,

but Rwc and eventual chages in the % even a constant they not from periodical units, and cant be used togather with

w=(2PiFj) as pure periodical or AC if You like?

...

I dont know,

maybe in just one case we can neglect the "miixing" of units when the Rwc=1 (Not less or equal but just equal...)

And from that persumption recalculate all other values. But than % wil be pointless, it will be the result not the input factor parameter?

It is not complicated I will make a new sheet.

Decoding the inputs...

We have talked a lot about the inputs. After some tries of making a working model, I concluded that a PNP differential circuit is not applicable. I cannot get it to work well enough with much better transistors than the PNP's that could have been made on the TDA1541 silicon.

So I looked at how TTL to PECL/CML translation is done. Like this:

The biasing to the right including the first NPN would be shared among the 4 inputs.

Of course it works beautifully to make a differential CML signal from our TTL input. It would suit the really slow PNP too...

So I dropped the input circuit around the PNP only into my sim of the signal conditioning:

First case, driven from a low impedance 3.3V CMOS pin (a TTL pin as on SAA7220 would be similar)

We can see nearly 20mA current spikes in the PNP collector (which if you look closely goes to substrate in the PECL circuit because these PNP's were really b!tchy to make, it would be the same on TDA1541.

And we can see current spikes of 20mA at twice the frequency of the signal!

With the speed limited and diode clipped signal we get a lot less current into the substrate, around 40 X (32dB) improvement:

But I think we now also have a more objective view of this phenomenon as well.

We need to kill the current spikes into the substrate as much as possible...

The attenuation seems actually less important. With just 1.2k/22pF and no clipping diodes we get this:

Still around 26dB improvement.

So I think a combination of resistor attenuation as originally shown by John with the right amount of capacitance will suffice, the thermal tracking etc. is brutal overkill. As are ECL circuits, except for the ~1pS jitter relocking of using ECL latches. It certainly suggests that the PECL outputs may be ok to drive TDA1541 via just RC.

I need to find a really slow transistor model to work more on this. Who off hand knows a common PNP with 10MHz FT and poor beta? I only know the opposite off hand.

Thor

We have talked a lot about the inputs. After some tries of making a working model, I concluded that a PNP differential circuit is not applicable. I cannot get it to work well enough with much better transistors than the PNP's that could have been made on the TDA1541 silicon.

So I looked at how TTL to PECL/CML translation is done. Like this:

The biasing to the right including the first NPN would be shared among the 4 inputs.

Of course it works beautifully to make a differential CML signal from our TTL input. It would suit the really slow PNP too...

So I dropped the input circuit around the PNP only into my sim of the signal conditioning:

First case, driven from a low impedance 3.3V CMOS pin (a TTL pin as on SAA7220 would be similar)

We can see nearly 20mA current spikes in the PNP collector (which if you look closely goes to substrate in the PECL circuit because these PNP's were really b!tchy to make, it would be the same on TDA1541.

And we can see current spikes of 20mA at twice the frequency of the signal!

With the speed limited and diode clipped signal we get a lot less current into the substrate, around 40 X (32dB) improvement:

But I think we now also have a more objective view of this phenomenon as well.

We need to kill the current spikes into the substrate as much as possible...

The attenuation seems actually less important. With just 1.2k/22pF and no clipping diodes we get this:

Still around 26dB improvement.

So I think a combination of resistor attenuation as originally shown by John with the right amount of capacitance will suffice, the thermal tracking etc. is brutal overkill. As are ECL circuits, except for the ~1pS jitter relocking of using ECL latches. It certainly suggests that the PECL outputs may be ok to drive TDA1541 via just RC.

I need to find a really slow transistor model to work more on this. Who off hand knows a common PNP with 10MHz FT and poor beta? I only know the opposite off hand.

Thor

It shoud be some "ac", becuse in formua for F, used AC current p-p and "2pfj" is circular so the variable of voltage shoul aloso be from the same unit pool...

No, I was actually not referring to this at all.

The AC voltage across the capacitor would need to be < 1/2 LSB equivalent of the 7.5V DC voltage.

The 7.5V DC causes the actual output current flow.

If the 7.5V is absolutely stable the DEM current only matters as average.

So the AC across the capacitor must be 7.5V (DC) / 2^17 or less (2^17 = 1/2LSB of 16 bit)

Now this gives 57uV AC and 7.5V DC.

So on the MSB the 2.5% ripple (PP) of 2mA must cause less than 57uV (PP) Voltage to ensure the variations of the actual output current for this specific bit are < 1/2MSB.

Clear?

Thor

I need to find a really slow transistor model to work more on this. Who off hand knows a common PNP with 10MHz FT and poor beta? I only know the opposite off hand.

Found something with ~30MHz Ft. Slower transistors = less spike.

Conclusions:

1) The spikey current into the Substrate from the input PNP transistor is strictly input signal slew rate related, it is not changed by swing.

2) A full CMOS or TTL swing into the input circuit will severely overdrive the CM Logic following the input circuit, which again will cause current into the substrate.

3) A variation of John Browns attenuation circuit with the correct capacitance to limit input slew rate will work fine.

4) It is not necessary to limit the the swing unduly, 230mV PP will cause the differential amplifier to saturate, getting into this window is challenging. ECL/CML uses greater drive levels,

Thor

A lot, now the origin of "AC" component is clear.Clear?

I would ad, with defining a 1/2 of LSB "something" voltage or current (in this case this is a current)

as

LSB=1/(2^n) ; where n=bit length (n=16 in our case)

=>

half value of LSB = [1 / (2^n) ] / 2 = 1 / [2 x (2^n)] = 1 / [ 2^(n+1) ]

so

Half value of LSB = 1 / ( 2^17 )

.

cheers

Maybe 2N2944 / 45 / 46a common PNP with 10MHz FT and poor beta?

Found something with ~30MHz Ft. Slower transistors = less spike.

this circuit a bitt better coping with current spikes? TryIt is not necessary to limit the the swing unduly, 230mV PP will cause the differential amplifier to saturate

bridged T balanced network. Just a few resistors more.

You can use online calc for half unbalanced section then divide the values for balanced. Only "central" values remains the same as it 2 x 1 x 1/2 of single bridged value...

I tried this at the output of F-F for aprox. -24db and Zout = 1K cca.

(I used this net many times for ttl spdif att. and was better than L-pad. Also better behaving and soun even in the crossover net)

But You may need a different values.

.

.

on line calcs

https://www.abex.co.uk/sales/calculators/bridged_tee_attenuator/index.php

Last edited:

this circuit a bitt better coping with current spikes?

No, not at all.

We face two separate phenomenae that so far have been treated "lumped".

Let's look at the schematic again.

The PNP input transistor is a simple emitter follower. So low FT is not a big issue.

What is, is that collector is directly the substrate. In actual semi fab terms this means that P Substrate all the IC is based on is also the collector of the the input PNP transistors, possibly the only PNP on the whole IC.

For more on how transistors on IC's are made look here:

https://www.halbleiter.org/en/funda...olar-transistor/tion-of-a-bipolar-transistor/

The PNP transistors can swing to 0V on the input and the common ~ 2.5...3V logic "High" level without exiting the linear operation.

The diode in the emitter bias's the following NPN Follower, which is much faster and drives the actual NPN differential pair.

That pair is in effect the beginning of our differential current mode logic (AKA PECL).

We have two problems.

The poor lateral PNP transistors need a lot of area to get useful performance. This means high capacitance. The input capacitance I'd actually Cbc (that is the reverse capacitance) and is listed as 12pF which is humongous!

With each edge of the incoming signal this capacitance is charged and discharged directly into the substrate and thus couples into the rest of the IC.

The old trick of pin 4 (I think) to ground instead of BCK in IIS mode disables one of the input stages and cuts this feed through in half!

The correct AND ONLY solution to these current spikes is to slow down the edge. Limiting the peak to peak level does jack (Sh!t) to control this phenomenon.

I now understand the "urban legend" / "folksanomy" modification of cutting pin 4 trace and linking it to ground and to insert "secret value" resistors between SAA7220 and TDA1541 I encountered on the early net in usenet groups (when I had a website - now I don't, because everyone, their dog and CAS has several).

Indeed, in IIS mode grounding pin 4 and adding resistors gives a big improvement. Add Philips/Grundig DEM reclock and sensible DEM capacitors and you are probably getting 85% of what an optimum design can do.

The other problem is overdriving the CML/ECL differential pair. It drives one half of the pair into hard shutoff and thus the other half into saturation.

The problem here is that a saturated transistor is slower to react to change than one in the linear operation range.

BUT the linear range is 230mV PP only and even legit ECL uses larger signal levels than that and clearly overdrives the diff pair.

For Data and BCK I think we have sufficient margin that even a saturated part of a diff pair doesn't upset the apple cart.

The noise dumped into +5V as a result (normally ECL GND as result) we can also manage.

So the main pin that should get attention is LE, it is IMNSHO the only pin that requires attention of signal.

Of course, attenuating the rest does no harm and pleases the eye.

So, add resistors and capacitors in series with MAINLY the BCK pin and to avoid timing contention equally to Data, no attenuator needed I think.

The RC should limit slew rate to ~ 5nS/V. I will try to come up with a better guess.

Take into account the 12pF input capacitance, so either just use a single resistor with 12pF (suggesting a 3.6k "magik" series resistor or 1.8k for > 176k SR) for existing gear modifications, or use a "big C" (say 100pF) and adjust the series resistor (accounting for source impedance - generally ~ 30R for 8mA rated CMOS.

So 150R + 100pF sound about right for a CMOS source on BCK & Data.

For ECL drivers, need to calculate.

Do we "RC" lowpass the WCK / LE signal?

I think so.

Do we attenuate WCK/LE ? Especially if running higher sample rates - I think so.

So 150R in series, 180R to "Ground" 220R to +3V3. Now "Low" is ~ 0.95V and "High" is 2.1V (still a bit more than we like) and we use 3 x 100pF in parallel.

I think this should be adequate to the needs of the TDA1541.

Again, KISS.

Thor

MJD5731T4GFound something with ~30MHz Ft. Slower transistors = less spike.

10Mhz, cherry picking can get us beta of 10 - 30.

This (bridged T bal) is for DEM 16/17.No, not at all.

I compared to the L-pad and this one giving better shape and less spikes on the edges.

With the pins 16 and 17 input circuit.

Last edited:

OK but somehow, based on the housing, seeme to me like near the obsolete part?That's the model I used...

Thor

I domt know the types, really...

MJD5731T4G

10Mhz, cherry picking can get us beta of 10 - 30.

I don't want this for real, just a spice model...

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A