quick check, is there also a GND connection between UFL wiring and the 10 pin header on the mainboard? Or is the "only GND connection through the black power supply wires? I had some instances where not having an extra ground wire between FiFoPi (through UFL shield) and dddac mainboard where this caused issues

your picture is not so clear on this point...

your picture is not so clear on this point...

Attachments

Can I have the schematic of the station board?

Thanks

Ian

I think you mean the DACs mainboard?

On page 3:

http://dddac.com/documents/dddac1794pbt_nos_ver51.pdf

Thanks,

Michael

quick check, is there also a GND connection between UFL wiring and the 10 pin header on the mainboard? Or is the "only GND connection through the black power supply wires? I had some instances where not having an extra ground wire between FiFoPi (through UFL shield) and dddac mainboard where this caused issues

your picture is not so clear on this point...

Thank you for your support.

I have connected the shield of the middle ufl connector to one of the ground pins at the i2s input connector of the mainboard. It is hard to see on the picture.

Accusilicon -338 update !

I am glad to say that theese baby’s are on the same level as Accusilicon- 318b. First impression was bad, but after a few days the sound is very good. If 338 is better sounding than 318b, I cant say for sure. Need more time, but happy for now.

Inspired by Doede, I replaced the stock trafo’s in my psu. 80-vac instead of 25-vac together with choke’s is a nice improvement. Bass is now tighter and stronger.

I am glad to say that theese baby’s are on the same level as Accusilicon- 318b. First impression was bad, but after a few days the sound is very good. If 338 is better sounding than 318b, I cant say for sure. Need more time, but happy for now.

Inspired by Doede, I replaced the stock trafo’s in my psu. 80-vac instead of 25-vac together with choke’s is a nice improvement. Bass is now tighter and stronger.

Attachments

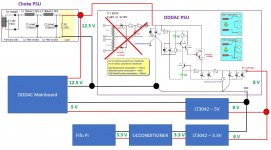

Hello Michael,

Can you make a simple drawing how you did configure the power supply that feeds the 12 volt print?

Greetings, Eduard

P.s i know by now how to do it but yours look a bit strange lol

Can you make a simple drawing how you did configure the power supply that feeds the 12 volt print?

Greetings, Eduard

P.s i know by now how to do it but yours look a bit strange lol

Thanks @JCMcNeil for your efforts to clock-roll no matter the outcome. At least you received those beauty's safely (Most important). Looking forward to your subjective conclusions.

You're welcome!

I'm just a day in but so far, so good. The AS338's sound, as far as I can tell without closer A-B comparisons, about as much better than the AS318B as the AS318b sounded better than the NDK NZ2520SDA.

Once I've got some more time on them, I'll swap in the other clocks so I can A-B as best I can with songs I have in alternate clock families.

Hello,

Thank you.

In the beginning it looked strange but now it makes sense!!.

You could try the diodes in the attachment.

I am using them too for my DDDAC choke input. Less than 1 euro each at mouser.

Greetings, Eduard

Thank you Eduard, I will try these for sure!

You can keep the DC power to the FifoPi clean side always on without shut down, so both of XOs will be powered continuously.

Excellent, that's good news and reinforces my decision to use an always-on LifePo4 (+ Ultracaps) power source that alternates between 2 batteries.

FifoPi Q3 also supports both XOs running at same time. In my system, I use two Pulsar OCXOs. They don't have any OE control. So both of them keep outputting even at time that is not selected as current MCLK. You can see my YouTube video for more information.

The Best Sound Quality Audiophile DIY DAC I Built in 2020 - YouTube

For XOs with the OE control, you can still keep them outputting all the time by disconnecting the OE pin from the XO sockets (they have internal pull-up).

Ian

So, for the FifoPi Q2 with AS338 clocks, would I need to disconnect the OE pins from the XO sockets to keep them outputting all the time? And how?

Sorry if that's a stupid question, it wasn't clear to me if that's only the case with the FifoPi Q3 or if it also applies to the Q2. I attached the datasheet for the AS338 in case it's helpful for anyone.

Attachments

It's nice to hear about the 2 AS338 (positive + neutral) preliminary reports.

Because we are limited to a handful of clock options, I just like seeing a progression of technology on this front even if it doesn't reach Pulsar levels yet.

It helps plan to lock in on the FiFoPi ecosystem and just plan to gradually upgrade clocks / FiFoPi+ReclockPi over time.

If the clock technology was static, I would have to find short-term purchasing option for the MagicXtal to lock it up. But because new clocks are introduced, I can decide in a few years if MagicXtal is still needed at that time. Probably, but it gives me time to build multiple Ian Canada systems over time to justify the MOQ5.

Loving the flexibility of Ian Canada's products not just for clocks, but for power sources and RPi or RPi-less sources. Just massive flexibility.

Because we are limited to a handful of clock options, I just like seeing a progression of technology on this front even if it doesn't reach Pulsar levels yet.

It helps plan to lock in on the FiFoPi ecosystem and just plan to gradually upgrade clocks / FiFoPi+ReclockPi over time.

If the clock technology was static, I would have to find short-term purchasing option for the MagicXtal to lock it up. But because new clocks are introduced, I can decide in a few years if MagicXtal is still needed at that time. Probably, but it gives me time to build multiple Ian Canada systems over time to justify the MOQ5.

Loving the flexibility of Ian Canada's products not just for clocks, but for power sources and RPi or RPi-less sources. Just massive flexibility.

Excellent, that's good news and reinforces my decision to use an always-on LifePo4 (+ Ultracaps) power source that alternates between 2 batteries.

So, for the FifoPi Q2 with AS338 clocks, would I need to disconnect the OE pins from the XO sockets to keep them outputting all the time? And how?

Sorry if that's a stupid question, it wasn't clear to me if that's only the case with the FifoPi Q3 or if it also applies to the Q2. I attached the datasheet for the AS338 in case it's helpful for anyone.

For FifoPi Q2 you will need the OE pins. So both XOs can be powered all the time but only one can output a one time.

For FifoPi Q3, you can use XOs both with and without a OE pin. So, both XOs can output at the same time if you want.

AS338 has the OE pin. If you want to disable the OE control, you can bent that OE pin so the OE pin will not be plugged into the XO socket.

Ian

I think you mean the DACs mainboard?

On page 3:

http://dddac.com/documents/dddac1794pbt_nos_ver51.pdf

Thanks,

Michael

Thanks Michael for the schematics.

According to the DDDAC internal logic design, it seems that when the input I2S clock stopped, the DDDAC analog output may hold at last output level. There will be no problem for the following amplifiers because DDDAC has output capacitors. But it could cause click / pop randomly at the moment of I2S clock restarted (Because the last DAC output level is random).

I have two solutions for you.

1. FifoPi has a dedicated isolated Mute output, normally an external DAC will need this FifoPi output signal to mute the analog output at the time of clock stopped or changed (for RPi GPIO, that's between songs ). Your problem can be fixed if you can make use of this Mute signal for you DDDAC. Many new DACs have logic to generate an internal auto mute in this case, that's why they don't have this kind of issue.

2. Keep the I2S signal running continuously without stopping between songs can also fix this issue.

To get the continuous I2S signal, you will need a USB streamer. You can use a BridgePi to adapt a Amanero Combo384 USB to the stack. GPIO will stop the I2S clock between the songs. That's the problem the Linux core. When connect a USB interface to a RPi, this problem can be solved.

Good luck.

Ian

Ian,

Thanks for looking into this. I actually does this, but not for reasons of clicking and popping. just because I happen to have a WaveIO on board an it is connected to the PI USB output (I did this for comparison purposes). You do not even need a Pi-bridge for that just dongle it at the back of the PI. power is coming from the PI. Probably every cheap Aliexpress usb pcb will do this trick

I have a question for the FiFoPi:

The DDDAC was designed with the WaveIO as source and there the I2S clock never stops (like you suggest with the Amanero)

In terms of muting: In the DDDAC the Zero-Flag (13) is connected to the Mute pin (10). This Mute is a soft mute and should not click or pop

When the PCM1794A detects that the audio input data is continuously zero for 1024 WDCKs in the external filter mode, the PCM1794A sets ZERO (pin 13) to HIGH and forces a soft mute. There should be no clicks or pops when there is no signal for at least 23 msec in 44.1 tracks

So when the FiFoPi stops the I2S signal at full breaks, the DAC would not mute

Or can you program FiFoPi so, that the WCK runs runs for another 2k or so?

May be another solution could be (just wildly thinking) to have the audio player have a short mute between tracks if that is possible?

Thanks for looking into this. I actually does this, but not for reasons of clicking and popping. just because I happen to have a WaveIO on board an it is connected to the PI USB output (I did this for comparison purposes). You do not even need a Pi-bridge for that just dongle it at the back of the PI. power is coming from the PI. Probably every cheap Aliexpress usb pcb will do this trick

I have a question for the FiFoPi:

The DDDAC was designed with the WaveIO as source and there the I2S clock never stops (like you suggest with the Amanero)

In terms of muting: In the DDDAC the Zero-Flag (13) is connected to the Mute pin (10). This Mute is a soft mute and should not click or pop

When the PCM1794A detects that the audio input data is continuously zero for 1024 WDCKs in the external filter mode, the PCM1794A sets ZERO (pin 13) to HIGH and forces a soft mute. There should be no clicks or pops when there is no signal for at least 23 msec in 44.1 tracks

So when the FiFoPi stops the I2S signal at full breaks, the DAC would not mute

Or can you program FiFoPi so, that the WCK runs runs for another 2k or so?

May be another solution could be (just wildly thinking) to have the audio player have a short mute between tracks if that is possible?

Hello Michael,

Because you are still a bit in the trial and error fase can you try connecting the input choke as suggested at the bottom of the Lundahl LL1694 pdf. So one coil in the LL 1694 will start at the center tap of the transformer and end at the first capacitor.

The GND coming from the circuit/caps will not end anymore at the center tap BUT at the first cap terminal.

The number of mH will remain the same but the filtering should improve. Of course you take care of the termination numbers.

Greetings, eduard

Because you are still a bit in the trial and error fase can you try connecting the input choke as suggested at the bottom of the Lundahl LL1694 pdf. So one coil in the LL 1694 will start at the center tap of the transformer and end at the first capacitor.

The GND coming from the circuit/caps will not end anymore at the center tap BUT at the first cap terminal.

The number of mH will remain the same but the filtering should improve. Of course you take care of the termination numbers.

Greetings, eduard

For FifoPi Q2 you will need the OE pins. So both XOs can be powered all the time but only one can output a one time.

For FifoPi Q3, you can use XOs both with and without a OE pin. So, both XOs can output at the same time if you want.

AS338 has the OE pin. If you want to disable the OE control, you can bent that OE pin so the OE pin will not be plugged into the XO socket.

Ian

Thanks, Ian, good to know I don't need to make any further changes and the clocks both stay powered.

I'm really enjoying the sound of the

Raspberry Pi 4>ConditionerPi>ReceiverPi>FifoPi Q2 Ultimate>TransportPi>HDMIPi Receiver>i2s to PCM board

combination with my "Studer 900" + Ultracaps powered AD1865 DAC and, now, AS338 clocks.

I think the StationPi and, when available, ReclockPi, will be the next steps in this system. (Or?)

Reports coming soon on AS338 clocks...once they have more time on them, I'll A-B them with the NDK and AS318b clocks on hand.

Last edited:

Yes,

ReclockPi really makes more improvements.

Ian

I'm looking forward to it.

And if you ever want one more set of ears to test out new devices before an official release, I'm happy to help ... and have done substantial ear training as a musician so feel confident in my ability to notice nuances.

@JCMcNeil

Please get back to me in 10 days to see if there is anything available for test.

Regards,

Ian

Please get back to me in 10 days to see if there is anything available for test.

Regards,

Ian

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter