Notes:

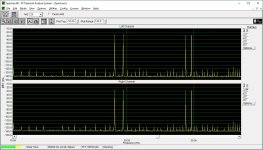

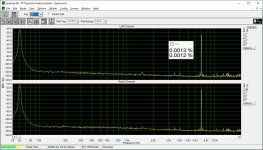

The distortion at 1KHz will be lower than what I posted (I simulated high frequencies).

Cascode jfets should be the appropriate type such as J310 or the ones used in the Calvin buffer.

The inputs can be bjt instead of jfet, but that will need degeneration resistors.

As usual with simple circuits, it needs good regulators. The simple regulator I showed will benefit from a RC filter before the mirror:

The distortion at 1KHz will be lower than what I posted (I simulated high frequencies).

Cascode jfets should be the appropriate type such as J310 or the ones used in the Calvin buffer.

The inputs can be bjt instead of jfet, but that will need degeneration resistors.

As usual with simple circuits, it needs good regulators. The simple regulator I showed will benefit from a RC filter before the mirror:

Attachments

How is your work progressing with the 4-layer pcb? Do you have any gerber files to share?I putted the 4 layers core pcb proto in production yesterday.

Folks,

Before I expressed my dissatisfaction with the IIS2SIM converters that use stopped clock and commented that I was not fond of CPLD/FPGA solutions.

I happen to feel that driving the Digital Inputs with lowest frequencies possible, with slew rate limited edges causes the least digital noise breakthrough into the output.

So to me the "ideal" IIS2SIM converter (TDA1541 specific) takes in IIS at BCK = 64 X FS and generates a BCK with 16 X FS, a narrow LE pulse and two 16 Bit Data streams with MSB inverted.

The raptorlightnighting FPGA in principle does that, has source code available and all that. Nice. But I still prefer something with more discrete logic.

I was looking at the jitter killer system in the Marantz DA-12 / Marantz PM-75 / Philips LHH-1000.

It's a quite involved way to make a 16 Bit FIFO:

A pair of 16 Bit shift registers is used to create a series to parallel conversion, then parallel to serial and clock out via "slow PLL Clock".

I remembered before using the 74HC40105 FIFO in a circuit to delay IIS data to allow 3-wire EIAJ to 4-wire EIAJ format conversion.

We can use stopped clock to bang the right serial bit's into the pipeline and then use our original BCK divided by 4 to clock out our data. We need one IC per Channel and would only use one of the 4 Lanes.

I checked availability and it remains at Mouser from TI. Only. ~ 3,700 in stock, 12 weeks leadtime. HC & HCT versions. Under 1 USD.

It would be neat to build an IIS2SIM converter using 74HC(T)40105, but I expect NRND or EOL some time soon. I could not find any second source with production. Shame that.

The 74ACT2226 would be even better. Two completely separate 64 Bit FIFO's. But nobody I can find stocks it. Direct order from TI only.

With 64 Bit we can "assemble" two full 16 Bit words before we clock out the first word and have always +/- 1 word margin. Two independent FIFO's mean we just need this IC. On the input we select which FIFO receives BCK based on FSYNC/WCK +

With the goal of only ever driving TDA1541, nothing else and integrating everything on Board. Attenuators, DEEM reclocking. I'd even throw on a CS8416 (aka DP7416 - Chinese copy in TSSOP) on board, multiplexing to an Amanero footprint. Add a basic TDA1541 Board (even vero board) or onboard it, for the core of a "Killa DAC".

We would divide BCK by 4 with low jitter parts (74S74?) and use that to clock the FIFO and a final set of 74S74 Latches with flying attenuators to drive TDA1541.

Logic on the input side would need a "clock stopper" that masks off unwanted bits, an XOR that allows MSB Inversion on either input or output. Need to think on that one.

Is anyone interested in a "discrete logic" IIS2SIM design using 70HC(T)40105 or 74ACT2226 despite the caveats, the sketchy ideas and all that anyway?

Instead of the raptorlightning FPGA. I have been unable to get hold of him.

Let me know, if so we open a new thread.

Thor

Before I expressed my dissatisfaction with the IIS2SIM converters that use stopped clock and commented that I was not fond of CPLD/FPGA solutions.

I happen to feel that driving the Digital Inputs with lowest frequencies possible, with slew rate limited edges causes the least digital noise breakthrough into the output.

So to me the "ideal" IIS2SIM converter (TDA1541 specific) takes in IIS at BCK = 64 X FS and generates a BCK with 16 X FS, a narrow LE pulse and two 16 Bit Data streams with MSB inverted.

The raptorlightnighting FPGA in principle does that, has source code available and all that. Nice. But I still prefer something with more discrete logic.

I was looking at the jitter killer system in the Marantz DA-12 / Marantz PM-75 / Philips LHH-1000.

It's a quite involved way to make a 16 Bit FIFO:

A pair of 16 Bit shift registers is used to create a series to parallel conversion, then parallel to serial and clock out via "slow PLL Clock".

I remembered before using the 74HC40105 FIFO in a circuit to delay IIS data to allow 3-wire EIAJ to 4-wire EIAJ format conversion.

We can use stopped clock to bang the right serial bit's into the pipeline and then use our original BCK divided by 4 to clock out our data. We need one IC per Channel and would only use one of the 4 Lanes.

I checked availability and it remains at Mouser from TI. Only. ~ 3,700 in stock, 12 weeks leadtime. HC & HCT versions. Under 1 USD.

It would be neat to build an IIS2SIM converter using 74HC(T)40105, but I expect NRND or EOL some time soon. I could not find any second source with production. Shame that.

The 74ACT2226 would be even better. Two completely separate 64 Bit FIFO's. But nobody I can find stocks it. Direct order from TI only.

With 64 Bit we can "assemble" two full 16 Bit words before we clock out the first word and have always +/- 1 word margin. Two independent FIFO's mean we just need this IC. On the input we select which FIFO receives BCK based on FSYNC/WCK +

With the goal of only ever driving TDA1541, nothing else and integrating everything on Board. Attenuators, DEEM reclocking. I'd even throw on a CS8416 (aka DP7416 - Chinese copy in TSSOP) on board, multiplexing to an Amanero footprint. Add a basic TDA1541 Board (even vero board) or onboard it, for the core of a "Killa DAC".

We would divide BCK by 4 with low jitter parts (74S74?) and use that to clock the FIFO and a final set of 74S74 Latches with flying attenuators to drive TDA1541.

Logic on the input side would need a "clock stopper" that masks off unwanted bits, an XOR that allows MSB Inversion on either input or output. Need to think on that one.

Is anyone interested in a "discrete logic" IIS2SIM design using 70HC(T)40105 or 74ACT2226 despite the caveats, the sketchy ideas and all that anyway?

Instead of the raptorlightning FPGA. I have been unable to get hold of him.

Let me know, if so we open a new thread.

Thor

Yes. Me too. Before some years in other topic, I asked about more infos on non-programmabile FIFOsBut I still prefer something with more discrete logic.

but i got back answer to look in the datasheets... 🙁

I am interested.Is anyone interested in a "discrete logic" IIS2SIM design using 70HC(T)40105 or 74ACT2226 despite the caveats, the sketchy ideas and all that anyway?

But It deserves special knowledge for these FiFOs. I cant help in this area 🙁 somehow i have a feeling that is a good way?

Compared to the proposed offerings it is supremely elegant and only a CPLD would be more compact. Replicating the functionality of the '673 alone should prove quite interesting.It's a quite involved way to make a 16 Bit FIFO:

But It deserves special knowledge for these FiFOs. I cant help in this area 🙁 somehow i have a feeling that is a good way?

Depends on the goals.

The key thing about an asynchronous fifo is that we have one clock to put data bits into the pipeline and a second clock to take data out of the pipeline.

So for our problem of having on the input side 64 clock cycles but only 16 bit's of data out of 64 actual Bits possible and on the output side and 16 clock cycles, a FIFO is an ideal construct.

We bang our 16 bit's from our IIS source into the pipeline by stopping the input clock when we have "unwanted" bits.

Now our 16 bit wanted data is in the pipeline. On the output we steadily clock out these 16 Bit at a much lower clock rate.

The FIFO absorbs the differences in clock speed. As long as we always have 16 bit into the pipeline in the time we take 16 bit's out, the FIFO fill level grows and contracts depending on incoming data.

But as long as there is at least 1 bit left in the pipeline to clock out, the data out flows, to use a cheap pun like clock work...

One more simple FIFO logic IC. Can build these more complex ICs multiplying this one? 74HC_HCT7403

The hc7403 looks interesting, but it seems essentially unavailable from any substantial source.

The hc40105 remain in long supply at 60 cent each. It can be cascaded to 32 bit.

I think a logic can be made that passes LE + DATAL + DATAR through a 32 Bit FIFO.

If we use a third FIFO, we can make it a 64 bit delay (that's how I used it) so we get L/R data simultaneously with one sample delay.

Yes, 3 pcs 40105. But little else is then needed.

The hc7403 FIFO or the hc2226 FIFO's make for a more elegant design.

Compared to the proposed offerings it is supremely elegant and only a CPLD would be more compact. Replicating the functionality of the '673 alone should prove quite interesting.

Not really. A HC40105 would be able to decouple all IIS lines between clock domains with a lot less circuitry.

BUT I happen to know the reason why Marantz was so complex.

It was planned at one point yo use 16 x opto coupler. At a maximum of 96kHz this was well feasible in the mid 80's. It was however eventually cancelled. Had the optoisolation never entered the picture, the circuit might very well have used a hc40105.

Thor

https://eu.mouser.com/ProductDetail...EpiMZZMutXGli8Ay4kCvShdToPR/dn9CH3xt%2Bl%2Bo=

Quite cheap, in good quantity, and even it gets eol soonish (smd goes into eol usually a while longer after TH does), not going to present an issue since tda1541a is obsolete for so long 🙂

On eol, obsolete topic, i'm still rooting for wm8804 for spdif, can be found in sufficient quantities still. Or a universal socket and separate adapter with preffered spdif chip.

Quite cheap, in good quantity, and even it gets eol soonish (smd goes into eol usually a while longer after TH does), not going to present an issue since tda1541a is obsolete for so long 🙂

On eol, obsolete topic, i'm still rooting for wm8804 for spdif, can be found in sufficient quantities still. Or a universal socket and separate adapter with preffered spdif chip.

In order to replace the '673 in that particular circuit you would need 4 '40105 and, assuming 4 bit versions, 4 serial in parallel out shift registers. However they arrived at it they arrived at an elegant solution.Not really. A HC40105 would be able to decouple all IIS lines between clock domains with a lot less circuitry.

In order to replace the '673 in that particular circuit you would need 4 '40105 and, assuming 4 bit versions, 4 serial in parallel out shift registers. However they arrived at it they arrived at an elegant solution.

Not at all. 1 x 40105 will be overkill actually.

The 673 & 674 form a simple 16 bit long FIFO for IIS Data. Nothing more. The circuit only stores a 1 bit x 16 data words. That is data is delayed by 16 bit.

A single 40105 can do that 4 times.

All the rest is not needed.

Thor

Yup. I think needs 3pcs for IIS2SIM.

Reclock BCK with MCK, then divide by 4 using 74F74 logic. Some lowest added jitter logic.

On eol, obsolete topic, i'm still rooting for wm8804 for spdif, can be found in sufficient quantities still. Or a universal socket and separate adapter with preffered spdif chip.

Ok, so a CS8412 socket, as a lot comes gor this, plus an adapter PCB with CS8416/DP7416 in either hardware or software mode to break off.

Second PCB for WM8804 if can be found.

Maybe some enterprising Schenese Kopy Kat will Kopy the WM8804. The CS8416 already has been.

Thor

I give up.The 673 & 674 form a simple 16 bit long FIFO for IIS Data. Nothing more. The circuit only stores a 1 bit x 16 data words. That is data is delayed by 16 bit.

I give up.

I can send you the full service manual.

The 673/674 form a 16 bit long 1 bit FIFO, output data to SAA7220.

The output clock (BCK2) comes from PLL that locks on the Preamble and uses a very nice LC oscillator. The input comes from the SPDIF receiver.

Yes, there is 16 bit serial input parallel output shift register. And it connects into a 16 Bit parallel input serial output shift register.

1 input and 1 output for IIS Data that is delayed 16 BCK periods and that then is send to the SAA7220.

It's functionally a simple asynchronous fifo, 1 bit wide, 16 bit long. The 74HC40105 is 4 x 1 bit wide and 16 bit long FIFO.

Is that so hard to grasp? Don't look at the precise circuit. Look at the result.

Thor

There can be no meeting of minds on this so I bid you adieu.

Surely we can both look at full schematic and agree on what it does? No meeting of minds, no opinions. Simple facts only?

There is no room for opinion or debate here. Either 16 bit's go in, serially, using one clock.

And then 16 bit go out, serially, using another non-synchronous clock (as you will find in the notes in the service manual I am still happy to send you), or not.

In which case (not) I and the people at Marantz who wrote the service manual are simply wrong.

Me being wrong happens all the time. Ask the Cat's.

Thor

Last edited:

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A