sound difference between all-mos and Lu iteration is, well, in domain of personal preferences

certainly both are good enough

certainly both are good enough

Today it was a busy day, I shuffled a big part of my digital library.

What I can say is that with the lu is does sound different but not by much.

It’s a bit more relaxed with more low level details, the bottom end seems a bit more precise. I get this sound with the settings from now but changing the vds of the lu can easily change all of that.

To mention also that I managed to get more than 100w at the output without noticing signs of bad sound which is not bad at all.

What I can say is that with the lu is does sound different but not by much.

It’s a bit more relaxed with more low level details, the bottom end seems a bit more precise. I get this sound with the settings from now but changing the vds of the lu can easily change all of that.

To mention also that I managed to get more than 100w at the output without noticing signs of bad sound which is not bad at all.

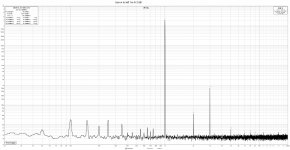

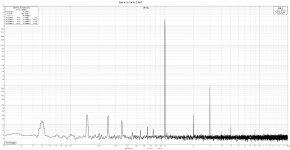

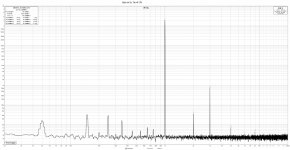

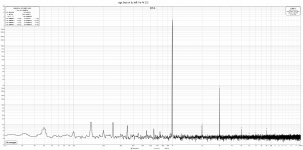

As you can see in the 2 attachments the Vds of the LUs is a bit different from one channel to the other to get same levels of 2nd hd, the jfets were matched.

I didn't set for the lowest 2nd.

One thing that it`s obvious is the 3rd hd that is close to 6x higher than the mosfet version. What can be done about this?

One more thing to mention is that I get 40+ watts and not 100+ like I said yesterday, I biased at 1a the fets like it was before.

I didn't set for the lowest 2nd.

One thing that it`s obvious is the 3rd hd that is close to 6x higher than the mosfet version. What can be done about this?

One more thing to mention is that I get 40+ watts and not 100+ like I said yesterday, I biased at 1a the fets like it was before.

Attachments

simple as ....... Lu is having much lesser THD, because of so much higher xconductance

so, resulting symmetry of entire shebang is so much higher

thus nulling of even harmonics is so much higher

as seen from previous iteration, sole way to get evens is to decrease level of symmetry ....

so, resulting symmetry of entire shebang is so much higher

thus nulling of even harmonics is so much higher

as seen from previous iteration, sole way to get evens is to decrease level of symmetry ....

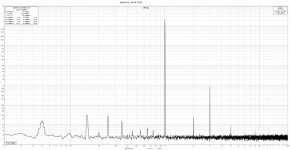

I wondered how could I decrease the 3rd hd. Is there any way?

Yes, I tried that already but can't increase 2nd more than 3rd.sole way to get evens is to decrease level of symmetry ....

Attachments

you can't do nothing, everything you have is pretty much as given

symmetry between OS parts is what dictates odds and THD level in general

symmetry between phases is what dictates evens and THD level in general

what you can try is varying drive to one of phases

though, remember, from very moment of choosing bridged OS configuration, you did chose dominating THD Spectra

how much you can alter that, as always, is dictated by several factors and finding right measure of compromises is entirely up to your taste

symmetry between OS parts is what dictates odds and THD level in general

symmetry between phases is what dictates evens and THD level in general

what you can try is varying drive to one of phases

though, remember, from very moment of choosing bridged OS configuration, you did chose dominating THD Spectra

how much you can alter that, as always, is dictated by several factors and finding right measure of compromises is entirely up to your taste

When I decrease the ccs current of only one half the 3rd hd decreases by close to 0.7x . One ccs is set for only 6ma.

If I set the ccs on both phases to only 6ma the 3rd goes 3x lower.

If I increase the ccs current the 3rd gets higher.

What would be the minimum current at which the jfet can be driven without frequency penalties?

If I set the ccs on both phases to only 6ma the 3rd goes 3x lower.

If I increase the ccs current the 3rd gets higher.

What would be the minimum current at which the jfet can be driven without frequency penalties?

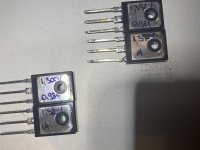

Lowering the drive current to 10-15ma and replacing irf510 with k2013 seems a good improvement. Simulating I got a 10x reduction.

Seems a nice thing to try.

Seems a nice thing to try.

if you have K2013, yes

regarding small mosfet Iq, do not trust too much in sims, check in vivo

while developing, I tried everything from 10 to 50mA, ended with what you see in schm

regarding small mosfet Iq, do not trust too much in sims, check in vivo

while developing, I tried everything from 10 to 50mA, ended with what you see in schm

I have to correct what I said above about 10x lower 3rd because of lower drive and k2013.

That modification increased the bias and this lowered the 3rd.

That modification increased the bias and this lowered the 3rd.

yes, you must take care of few things

to maintain symmetry of Ugs voltages (lower mosfet and upper mosfet level shifter), if you vary level shifter Iq, then you must accordingly vary value of level shifting resistor, to maintain OS Iq

in short, keeping said Ugs-es in ballpark, keeping OS Iq in ballpark, only then you can compare overall performance

with CMirrors in biasing mechanism, symmetry of Ugs-es isn't anymore important to ensure minimal sliding of DC OFfset (as it was with resistors to rails and opto between gates, previous biasing arrangement) but it is important to ensure symmetrical clipping

that being of academic importance for me, never needing that sort of power, but it is matter of principle

to maintain symmetry of Ugs voltages (lower mosfet and upper mosfet level shifter), if you vary level shifter Iq, then you must accordingly vary value of level shifting resistor, to maintain OS Iq

in short, keeping said Ugs-es in ballpark, keeping OS Iq in ballpark, only then you can compare overall performance

with CMirrors in biasing mechanism, symmetry of Ugs-es isn't anymore important to ensure minimal sliding of DC OFfset (as it was with resistors to rails and opto between gates, previous biasing arrangement) but it is important to ensure symmetrical clipping

that being of academic importance for me, never needing that sort of power, but it is matter of principle

I rushed with the post and noticed after about the bias being responsible.

So if I keep the OS bias the same and the said Ugs-es in ballpark seems that the only thing to lower the 3rd is increasing the bias.

So if I keep the OS bias the same and the said Ugs-es in ballpark seems that the only thing to lower the 3rd is increasing the bias.

Now I am convinced.you can't do nothing, everything you have is pretty much as given

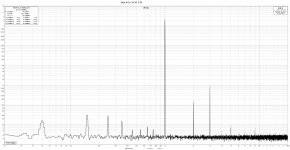

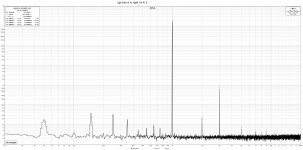

Today I increased the bias which lowered the 3rd like in the sim and at this point I could set for 2nd predominant which I also did but to be honest I like the 3rd too so I set for maximum symmetry between the phases of each amp and put the top covers on.

Now I can compare the type of sound that I have now with what I had for many years in the past which was exactly the opposite.

What I noticed was also that certain tracks go well with 2nd and others with 3rd.

After all the drilling and soldering now I have to enjoy a bit the sound because they sound so good 😎

Now I can compare the type of sound that I have now with what I had for many years in the past which was exactly the opposite.

What I noticed was also that certain tracks go well with 2nd and others with 3rd.

After all the drilling and soldering now I have to enjoy a bit the sound because they sound so good 😎

Attachments

well, there is one good thing after all of this

even if you're disappointed with sound of amps, at least you overcome your unease with threads tapping

even if you're disappointed with sound of amps, at least you overcome your unease with threads tapping

- Home

- Amplifiers

- Pass Labs

- The marriage