How to Play TIDAL/local MQA music on a Raspberry Pi via Volumio?

I made a new YouTube Video

https://www.diyaudio.com/forums/dig...adding-adapter-board-mqa-dac.html#post6595881

How to Play MQA music on a Raspberry Pi via Volumio - YouTube

Ian

I made a new YouTube Video

https://www.diyaudio.com/forums/dig...adding-adapter-board-mqa-dac.html#post6595881

How to Play MQA music on a Raspberry Pi via Volumio - YouTube

Ian

Last edited:

That's great. What 3D printer do you have?

Can I use a 3D printer to print a bigger case?

Good weekend.

Ian

Can I use a 3D printer to print a bigger case?

Good weekend.

Ian

I have a far from stock Anycubic Predator 3D Delta printer.

That's great. What 3D printer do you have?

Can I use a 3D printer to print a bigger case?

Good weekend.

Ian

@Ian,

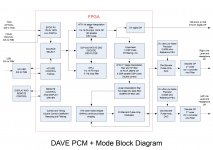

Have you ever considered the development of FPGA-based DAC? Chord develops a series of FPGA-based DAC, especially Chord DAVE is the pinnacle of work, surpassing many dac based on ess9038pro. I certainly understand that it is very difficult for the sound quality of FPGA-based DAC to surpass ess9038pro DAC, and the required investment cost is very high. However, if Ian can approach the level of Chord DAC through the evolution of several versions, you will also become one of the DAC brand developers. That will be the glory of sponsoring Diyaudio members. In addition, your reclock technology is already very mature. If you can further integrate the DAC function, you can even surpass Chord DAVE.

Have you ever considered the development of FPGA-based DAC? Chord develops a series of FPGA-based DAC, especially Chord DAVE is the pinnacle of work, surpassing many dac based on ess9038pro. I certainly understand that it is very difficult for the sound quality of FPGA-based DAC to surpass ess9038pro DAC, and the required investment cost is very high. However, if Ian can approach the level of Chord DAC through the evolution of several versions, you will also become one of the DAC brand developers. That will be the glory of sponsoring Diyaudio members. In addition, your reclock technology is already very mature. If you can further integrate the DAC function, you can even surpass Chord DAVE.

Have you ever considered the development of FPGA-based DAC?

What advantage would FPGA bring?

What advantage would FPGA bring?

In general use, additional jitter will be generated in the path between the RECLOCK and the dac chip. Assuming that the functions of RECLOCK and dac are implemented in the same FPGA, the jitter generated by the path between them can be so small that they can be ignored. The only premise is that FPGA-based DAC and ess9038pro are at a comparable level.

This is the reason why chord DAVE has such an excellent level.

ummm....

Let's be clear: there is no such thing as an "FPGA DAC". FPGAs are digital chips, and only have a digital output. Commercial DACs which use FPGAs use the FPGA for the DSP/oversampling section of the DAC, and not for the actual digital to analog conversion.

For example, in Chord DACs, the FPGA runs the oversampling operations, and then outputs a very high rate digital signal, which is then converted to analog via the "Pulse Array DAC", which consists of discrete parts (flip flops and resistors in Chords case, I believe).

I cringe every time I hear "FPGA DAC", because it is misleading way to characterize how those DACs actually work.

These types of DACs generally use the FPGA to create a very high rate digital signal, which can then be converted to analog fairly simply by a discrete conversion circuit.

Let's be clear: there is no such thing as an "FPGA DAC". FPGAs are digital chips, and only have a digital output. Commercial DACs which use FPGAs use the FPGA for the DSP/oversampling section of the DAC, and not for the actual digital to analog conversion.

For example, in Chord DACs, the FPGA runs the oversampling operations, and then outputs a very high rate digital signal, which is then converted to analog via the "Pulse Array DAC", which consists of discrete parts (flip flops and resistors in Chords case, I believe).

I cringe every time I hear "FPGA DAC", because it is misleading way to characterize how those DACs actually work.

These types of DACs generally use the FPGA to create a very high rate digital signal, which can then be converted to analog fairly simply by a discrete conversion circuit.

In general use, additional jitter will be generated in the path between the RECLOCK and the dac chip.

You should stop with nonsense claims.

Have you ever measured the additive jitter between the reclocker and the DAC?

Why do you think there will be additive jitter?

The path between the reclocker and the DAC is usually a coaxial cable, so you think jitter will be added?

If you think so please post your jitter measurements.

The master clock is close to the DAC and clocks the USB receiver I2S section or the I2S peripheral of the ARM SoC (e.g. in RPi). Why jitter, why reclocker?

You should stop with nonsense claims.

Have you ever measured the additive jitter between the reclocker and the DAC?

Why do you think there will be additive jitter?

The path between the reclocker and the DAC is usually a coaxial cable, so you think jitter will be added?

If you think so please post your jitter measurements.

You should stop with nonsense claims.

Things that can be understood purely theoretically, do not need to be measured, unless you are not familiar with the relevant theories. If you are not familiar with the relevant theories, this makes me wonder how your modules are made?

The main source of Jitter is that the transmission time of electrical signals is different. We know that any wire will have capacitance. Maybe only you don’t know it. 😀 Capacitance is an obstacle that affects high potential to low potential/low potential to high potential, 0 to 1 and 1 to 0 of the charging and discharging time, but not only the capacitance of the wire itself, but also the crosstalk effect between the wire and the wire will also cause the wire's charging time to be hindered. Such signal delay causes sampling and restoration errors in the analog-to-digital converter and the digital-to-analog converter. In addition to capacitance, electromagnetic interference (EMI) can also cause Jitter. Then you should understand that jitter between the reclocker and the DAC through wires, circuits and electronic components, etc?

Let's be clear: there is no such thing as an "FPGA DAC". FPGAs are digital chips, and only have a digital output. Commercial DACs which use FPGAs use the FPGA for the DSP/oversampling section of the DAC, and not for the actual digital to analog conversion.

For example, in Chord DACs, the FPGA runs the oversampling operations, and then outputs a very high rate digital signal, which is then converted to analog via the "Pulse Array DAC", which consists of discrete parts (flip flops and resistors in Chords case, I believe).

I cringe every time I hear "FPGA DAC", because it is misleading way to characterize how those DACs actually work.

These types of DACs generally use the FPGA to create a very high rate digital signal, which can then be converted to analog fairly simply by a discrete conversion circuit.

Have you noticed that the word I used is DAC function? Did I mention that FPGA DAC is the so-called DAC chip?

If you are interested in chord DAVE, you can take a closer look at the explanation of Rob Watts below.

Chord DAVE, Part 2: The Interview With Rob Watts - Positive Feedback

You should stop with nonsense claims.

Things that can be understood purely theoretically, do not need to be measured, unless you are not familiar with the relevant theories. If you are not familiar with the relevant theories, this makes me wonder how your modules are made?

The main source of Jitter is that the transmission time of electrical signals is different. We know that any wire will have capacitance. Maybe only you don’t know it. 😀 Capacitance is an obstacle that affects high potential to low potential/low potential to high potential, 0 to 1 and 1 to 0 of the charging and discharging time, but not only the capacitance of the wire itself, but also the crosstalk effect between the wire and the wire will also cause the wire's charging time to be hindered. Such signal delay causes sampling and restoration errors in the analog-to-digital converter and the digital-to-analog converter. In addition to capacitance, electromagnetic interference (EMI) can also cause Jitter. Then you should understand that jitter between the reclocker and the DAC through wires, circuits and electronic components, etc?

You keep talking about jitter without the minimal knowledge.

We have already undrstood you don't know what is jitter (in time domain) or phase noise (in frequency domain).

Indeed you are pointing to the capacitance of the coaxial cable because you don't understand what is its impedance.

And just to correct your nonsense claiming, our 5.6448 MHz oscillator performs -155dBc dBc at 10 Hz from the carrier (or 43fs if you want) including the phase noise (or jitter) of the coaxial cable.

Because yes, we have used a coaxial cable SMA terminated to connect the oscillator to the instrument in order to make the measurement, 1 meter long.

And despite the jitter of the coaxial cable (which does not exist) it keep performing as a state of the art oscillator, almost 50 dB better than the poor Accusilicon you are advising in most of the diyaudio threads.

And the most curious thing is you are suggesting to drive the DAC directly from the FPGA (the FPGA is the DAC itself in your suggestion) to reduce the jitter.

So, not only you don't know what you are talking about, but you are pointing out a solution that clearly increase the jitter.

I have to assume you are not able to read a phase noise (jitter) plot

The Well synchronized asynchronous FIFO buffer - Slaved I2S reclocker

Please give it a cut.

You can use 5V for the clean side of FIFOPi, (I use 4.1v) but FIFOPi has an onboard LT3042 reg that takes that down to 3.3V for the clock power pin. You can supply your own power to the clock by removing the power pin from the clock PCB and installing your own power supply.

Indeed you are pointing to the capacitance of the coaxial cable because you don't understand what is its impedance.

I explained it so clearly, but you still can’t learn it, I can only say that it’s a pity. but Please give it a cut.

And just to correct your nonsense claiming, our 5.6448 MHz oscillator performs -155dBc dBc at 10 Hz from the carrier (or 43fs if you want) including the phase noise (or jitter) of the coaxial cable.

Because yes, we have used a coaxial cable SMA terminated to connect the oscillator to the instrument in order to make the measurement, 1 meter long.

And despite the jitter of the coaxial cable (which does not exist) it keep performing as a state of the art oscillator, almost 50 dB better than the poor

Any transmission line will be affected by capacitance or EMI and produce jitter, which is inevitable.

You spent a lot of time writing a bunch of nonsense, just to hide something?

Accusilicon you are advising in most of the diyaudio threads.

Ian also recommended AS318.

AS318 is indeed better than Crystek CCHD-957. This is a comment often seen on diyaudio, and AS318 is cheaper, and it is packaged in DIP14, which is convenient to use. , What is your question?

Since you love arguing with me so much, I will tell you clearly all at once, please stop arguing in the future. Your clock module must use leads, which is not convenient to use, so you are particularly dissatisfied with me? You just think of a way to change your clock module to DIP14 package, will that solve your problem? Or, when you If the clock is changed to DIP14 package, the performance will be greatly degraded, even not as good as AS318?

We all know that for a clock module with a huge volume, of course, you can choose to use components of a good level to obtain better clock performance. In contrast, when it is limited to the DIP14 package, the components that can be selected are limited, and the performance is difficult to improve. When you compare your clock with the AS318, it is actually meaningless. This is like comparing your clock with the pulsar clock belonging to OCXO, which is meaningless.

And the most curious thing is you are suggesting to drive the DAC directly from the FPGA (the FPGA is the DAC itself in your suggestion) to reduce the jitter.

The strangest thing is that I have never written before, but come out of your brain.

It is suggested that Ian develop FPGA-based DAC and integrate Ian's reclock, which is to see the success of chord DAVE. How chord DAVE achieves beyond ES9038PRO, I have already pointed out the source of information. However, it seems that Ian has limited knowledge of DAC and cannot develop FPGA-based DAC. Then I won't wait for Ian's response anymore. I will never come back to watch other people's meaningless responses. Of course include yours.

The strangest thing is that I have never written before, but come out of your brain.So, not only you don't know what you are talking about, but you are pointing out a solution that clearly increase the jitter.

I have to assume you are not able to read a phase noise (jitter) plot

The Well synchronized asynchronous FIFO buffer - Slaved I2S reclocker

Before you continue to write more jokes, I suggest you take a closer look at what exactly Chord DAVE did to make it surpass ES9038PRO.

Please give it a cut.

Last edited:

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter