There is an RC filter to feed the VCXO: with some skills you could replace the R with a header..... just a jumper would activate/desactivate the oscillator. But I believe the filter is needed 🙂 when jou need the oscillator. A tweak is the feed the oscillator from an external supply or with a direct line from the LDO (and not use a feed-line of the FPGA)

The problem is that I need to disconnect even the micro and the FPGA so removing the LDO is the simplest way.

You can always stick some shielding in between, the 'flying connection wires' should be as short as possible.

I believe there will not problem of shielding, however I will measure the RFI/EMI with a sniffer.

Been thinking about how to connect the PCB: plated half holes (catellated holes) well aligned with the connection points below. For mounting you could use a single strand from a wire of which you solder on end to the right connection point on the dam1021. You pull it gently up like little antennas. You mount the new controllerboard ( with some shielding stuck at the bottom, grounded). Finally you solder (quickly) with a tiny drop (or some solder paste), the antennas in the corresponding half-holes that should be positionned just above. Cut of the remainder of the antenna, next...

To dismount, you can cut with a tiny cutter wire by wire without the mechanical stress a solid pin would create. I found out you can easily lift a solder island / tiny capacitor from the DAM1021.

To dismount, you can cut with a tiny cutter wire by wire without the mechanical stress a solid pin would create. I found out you can easily lift a solder island / tiny capacitor from the DAM1021.

Andrea, must say I'm impressed by the speed and determination this is moving forward!

Contrary to what some supporters claim I well know how a R2R DAC works, in fact I'm designing my own R2R DAC.

However, the development could be even faster if the designer helped.

Hi all, Happy New Year.

Off topic, I apologize. Fast question for a fast answer please to Berny : do your Dam dac is sounding better than the Aya dac with the TDA1541 ???

For me the Dam dac (first iteration) was a big catastroph about the sound and frankly if I understood I could improve it with a better supply and decoupling what I did and I comunicate here fastly and at least what people understood and followed since the beginning, I found at the end the front end and power supply stage were so loosed than nothing could improve it this dac.. . at least first iteration, I duno for the latest.

Imo Andrea but for the exercice or if maybe you have the last versions I'm not aware about, you're loosing your time. But maybe you know already that 😀... If I had this dac yet I will just keep the RéR section, do apply some surgeon to cut the pcb to through out all the front end and power supply... which frankly could be problematic due to the fast needed about the clock for such a dac...

Off topic, I apologize. Fast question for a fast answer please to Berny : do your Dam dac is sounding better than the Aya dac with the TDA1541 ???

For me the Dam dac (first iteration) was a big catastroph about the sound and frankly if I understood I could improve it with a better supply and decoupling what I did and I comunicate here fastly and at least what people understood and followed since the beginning, I found at the end the front end and power supply stage were so loosed than nothing could improve it this dac.. . at least first iteration, I duno for the latest.

Imo Andrea but for the exercice or if maybe you have the last versions I'm not aware about, you're loosing your time. But maybe you know already that 😀... If I had this dac yet I will just keep the RéR section, do apply some surgeon to cut the pcb to through out all the front end and power supply... which frankly could be problematic due to the fast needed about the clock for such a dac...

Last edited:

My version is 5D, however regardless of the version the architecture of the front end is still the same.

I believe that the DAC section of the DAM1021 is more than fine, while I fully disagree with the architecture of the front end.

This is the reason why I'm developing the interface board.

With the interface board there will be no longer clock problems since the LRCK will come from the FIFO Lite master clock, where one can install the best oscillators available.

I believe that the DAC section of the DAM1021 is more than fine, while I fully disagree with the architecture of the front end.

This is the reason why I'm developing the interface board.

With the interface board there will be no longer clock problems since the LRCK will come from the FIFO Lite master clock, where one can install the best oscillators available.

I have V3, almost unmodded (for now) and using Li-Ion supply (2×8V) without using the opamps at the output. My Aya (with DS and audial USB interface, almost fully tweaked) is still better and my day to day dac. On a regular base, I can hear Danny's Dam which is a fully tweaked V1. Some serious tweaking time was spend on that dac too and it clearly has the edge in 3D positionning / accuracy in two different systems (mine and his ;-) ). I believe I'm at the limit of my dac chip in my Aya, very unfortunately... and when for the price of another chip / with to much risks involved, I could have a 2nd hand V3 Dam almost untouched... I had to jump the dark side ;-) But I believe it will take some time before it will be able to replace my beloved Aya...

Yes, it's always mandatory to dive in the dark side whatever the Dac board 😉 be it Aya or any else. Thanks for the precision and I will end with this : have you a crowned tda1541a or a late south Asia of the 90s Singapore or Taiwan chip ?

But I believe it will take some time before it will be able to replace my beloved Aya...

Hello Berny, can the DAC also play 24 bit / 96 Khz? ?

No, the tda1541 is 16bits as you probably know... but higher sample rates is no problem at all.

99% of my music is 16bit anyway, so I dont care about these numbers.

99% of my music is 16bit anyway, so I dont care about these numbers.

Here's a list of the mods that I did on my v1.

After all those mods it betters Berny's Aya DAC 🙂

but definitely not before the mods

- removed output opamps, use output of resistor networks

- added external shunt PS

- Cut the USB +5V power to the Amanero and add its own Lt3045 PS.

- Added lots of extra capacitance to the vrefs and clock

- lowresmod (only necessary for my v1)

- replaced the four onboard regulators with muzgdiy regulators v3.1

- BC550/560 transistor mod for the vrefs

After all those mods it betters Berny's Aya DAC 🙂

but definitely not before the mods

- removed output opamps, use output of resistor networks

- added external shunt PS

- Cut the USB +5V power to the Amanero and add its own Lt3045 PS.

- Added lots of extra capacitance to the vrefs and clock

- lowresmod (only necessary for my v1)

- replaced the four onboard regulators with muzgdiy regulators v3.1

- BC550/560 transistor mod for the vrefs

Last edited:

The upgrade is definitive as the DAM1021 will also work in the original mode without any need for further hardware changes.

The I/O pins of the SPARTAN6 are high-impedance before and throughout the power-up and configuration processes.

Indeed the SPARTAN6 holds the POR state (Power on Reset) until all the supplies reach their respective thresholds.

Only after these tresholds have been reached the FPGA begins its configuration process.

Therefore a small board replacing the on-board 3V3 LDO is sufficient to switch between the original from the factory and the upgraded DAM1021.

This way when the LDO is disconnected the VCXO, the FPGA and the micro are disabled.

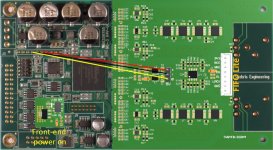

In order activate the upgrade the power supply has to be connected from the DAM1021 to the Interface board (black, red and yellow lines in the picture) and the switch installed on the new little board has to be shifted in "LDO OFF" position.

While to return to the original configuration from the factory the above power supply has to be disconnected and the switch has to be shifted in "LDO ON" position.

The I/O pins of the SPARTAN6 are high-impedance before and throughout the power-up and configuration processes.

Indeed the SPARTAN6 holds the POR state (Power on Reset) until all the supplies reach their respective thresholds.

Only after these tresholds have been reached the FPGA begins its configuration process.

Therefore a small board replacing the on-board 3V3 LDO is sufficient to switch between the original from the factory and the upgraded DAM1021.

This way when the LDO is disconnected the VCXO, the FPGA and the micro are disabled.

In order activate the upgrade the power supply has to be connected from the DAM1021 to the Interface board (black, red and yellow lines in the picture) and the switch installed on the new little board has to be shifted in "LDO OFF" position.

While to return to the original configuration from the factory the above power supply has to be disconnected and the switch has to be shifted in "LDO ON" position.

Attachments

It is unfortunate the board can't be used with I2S directly, with MClk. It would make the whole thing more universal and people could easily insert or remove a FIFO with I2S in and out...

I could add a converter from I2S to the custom DAM segmented sign magnitude protocol but I should use a FPGA and the FPGA is already in the FIFO Lite that accepts just I2S and can implement state of the art master clocks.

Moreover if I would provide I2S input in the interface board you should install anyway a FIFO.

I'm pretty sure that for the DACs like the DAM (and all other DACs latching on LRCK) the FIFO Lite will perform much better than any other FIFO buffer available.

It's simply a question of design approach: the best as possible for us, the greater business as possible for the others.

Moreover if I would provide I2S input in the interface board you should install anyway a FIFO.

I'm pretty sure that for the DACs like the DAM (and all other DACs latching on LRCK) the FIFO Lite will perform much better than any other FIFO buffer available.

It's simply a question of design approach: the best as possible for us, the greater business as possible for the others.

At what frequency is the R2R ladder of the DAM1021 clocked? Sampling frequency or higher?

From your explanation one might infer that if you divide down low enough the phase noise hardly matters. Which is not possible for a massively oversampled S-D DAC, but fine with many R2R DACs...

Can you tolerate 30-40 ms delay in your application?

A simple CPLD should do the trick, you could/should include all shift registers in there too and keep the small DFF to reclock the critical signals. It will simplify your layout and PCB size. But you know all that and with the smaller PCB and optimized MC-count it might be a more flexible design at similar cost.

New life for the DAM - DAC calibration to 24 bit

We are implementing a linearity digital correction in our FIFO Lite to be used with our new DAC Lite and virtually even with any other DACs.

As you know the tolerance of the resistors used in the DAM1021 (0.01% or 0.02%) limits its ladder accuracy (or linearity) to about 14 bit.

The implementation of the upgrade allows to feed the DAM with the FIFO Lite and so the DAC calibration feature will be available even for the DAM1021.

This way the ladder network of the DAM will be calibrated to real 24 bit even using the resistors supplied from the factory, without any hardware mods.

We are implementing a linearity digital correction in our FIFO Lite to be used with our new DAC Lite and virtually even with any other DACs.

As you know the tolerance of the resistors used in the DAM1021 (0.01% or 0.02%) limits its ladder accuracy (or linearity) to about 14 bit.

The implementation of the upgrade allows to feed the DAM with the FIFO Lite and so the DAC calibration feature will be available even for the DAM1021.

This way the ladder network of the DAM will be calibrated to real 24 bit even using the resistors supplied from the factory, without any hardware mods.

Hello,

How the digital correction senses the physical ladder resistors according the temperature variation in the cabinet that may affect those very high % precision levels, as the resistor drifts by ageing at this level, as dust, humidity level... ?

sealing then in a resine or thick varnish could help ? Are chips not better due to their compact size and their casing ? Rephrasing it, where is the advantage of discrete ladder dacs ? Precision of the resistors array, the material in it (e.g. : TotalDac and naked Vishays ?) ???

14 bits... that's a Damn TDA1540 😀 !

How the digital correction senses the physical ladder resistors according the temperature variation in the cabinet that may affect those very high % precision levels, as the resistor drifts by ageing at this level, as dust, humidity level... ?

sealing then in a resine or thick varnish could help ? Are chips not better due to their compact size and their casing ? Rephrasing it, where is the advantage of discrete ladder dacs ? Precision of the resistors array, the material in it (e.g. : TotalDac and naked Vishays ?) ???

14 bits... that's a Damn TDA1540 😀 !

Last edited:

- Home

- Source & Line

- Digital Line Level

- Implementing a true FIFO buffer with low phase noise clock on the Soekris DAM1021 DAC