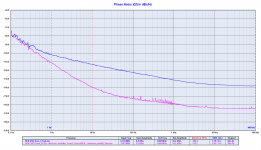

I attach some phase noise plots of the FIFO Lite:

- MCLK output

- BCK output (FIFO Lite + Reclocker)

- LRCK output

- Comparison (including the base DRIXO 24.576 MHz oscillator)

this is the "sound" of dedication.

hats off, as always

Hello,

Much to technical for me.

But this will allow DDDAC users to get a nice improvement?

Greetings, eduard

Much to technical for me.

But this will allow DDDAC users to get a nice improvement?

Greetings, eduard

Theoretically yes, the DDDAC use the BCK as the crucial signal and if you look at the BCK phase noise plot you see -140dBc at 10 Hz and less than -110 dBc at 1 Hz from the carrier.

These are very good results, the best we have mesured until now.

These are very good results, the best we have mesured until now.

Just a comparison between the BCK coming from the FPGA and the BCK after the reclocker.

The phase noise of the BCK signal directly from the FPGA is very poor, while after the recloker it's fine.

It looks like the FIFO Lite with good oscillators will be able to feed at best the DACs which switch on the BCK like the PCM1704, PCM1794 and so on.

The phase noise of the BCK signal directly from the FPGA is very poor, while after the recloker it's fine.

It looks like the FIFO Lite with good oscillators will be able to feed at best the DACs which switch on the BCK like the PCM1704, PCM1794 and so on.

Attachments

Just a comparison between the BCK coming from the FPGA and the BCK after the reclocker.

The phase noise of the BCK signal directly from the FPGA is very poor, while after the recloker it's fine.

It looks like the FIFO Lite with good oscillators will be able to feed at best the DACs which switch on the BCK like the PCM1704, PCM1794 and so on.

YES Andrea,My dac waits for your FIFO🙂

Someone must learn from this data [emoji28]Just a comparison between the BCK coming from the FPGA and the BCK after the reclocker.

The phase noise of the BCK signal directly from the FPGA is very poor, while after the recloker it's fine.

It looks like the FIFO Lite with good oscillators will be able to feed at best the DACs which switch on the BCK like the PCM1704, PCM1794 and so on.

Is there a group buy set up for this project yet? A link to a sign up or interested to buy list? Thanks.

regards,

Steve

regards,

Steve

Not yet, we are still testing the firmware and the software of the FIFO.

I think a new GB will be started within a couple of months.

I think a new GB will be started within a couple of months.

We have already tested the FIFO Lite with the Sabre DAC in async mode and soon we will test the same DAC in true sync mode.

I have already got Ian's dual mono ESS DAC and the Buffalo 3se.

We believe the best implementation is using the DAC in true sync mode stopping the DPLL inside the DAC, so the most important signal is the master clock.

The reclocker board is not needed.

I have already got Ian's dual mono ESS DAC and the Buffalo 3se.

We believe the best implementation is using the DAC in true sync mode stopping the DPLL inside the DAC, so the most important signal is the master clock.

The reclocker board is not needed.

Thanks Andrea.

Im using my Buffalo IIISE in sync mode with Ian's FIFO/DUALXOII as it is vastly better than async to my ears..

Im using my Buffalo IIISE in sync mode with Ian's FIFO/DUALXOII as it is vastly better than async to my ears..

Will this be compatible with ryanj D3 dac, 2 x TDA1541A I2S simultaneous. I believe iancanada fifo/dual xo has been implemented with this dac so I am thinking yes, but with your implementation of clock strategy vs fifopi.

best regards,

Steve

best regards,

Steve

Yes, I believe it will be compatible with ryanj D3 dac in simultaneous mode.

The advantage is that the LRCK signal (the most crucial for the TDA1541A) comes directly from the clean master clock rather than from the FPGA.

The advantage is that the LRCK signal (the most crucial for the TDA1541A) comes directly from the clean master clock rather than from the FPGA.

If I may add, I think beyond the clean LRCK another key value proposition is that your device outputs the synchronous PCM signal required by TDA1541A. This eliminates the stand alone pcb from Iancanada or Ryanj. One less component to screw up the data stream. With Ian's solution, you have one FPGA in Fifo creating the signal, then another FPGA in the I2StoPCM that translates it into the signal preferred for the 1541a. In both cases there are power supplies and connectors all points of failure or sound degradation.

Latest revision, from left to right:

- TWSAFB-LT Fifo buffer Lite

- TWSAFB-OI optical output interface

- TWSAFB-OIR optical output interface & reclocker

We are testing the software, then we will test several DAC.

- TWSAFB-LT Fifo buffer Lite

- TWSAFB-OI optical output interface

- TWSAFB-OIR optical output interface & reclocker

We are testing the software, then we will test several DAC.

Attachments

Great. TWSAFB-OIR is what I'm looking for. That is independent flip-flop for each signal. Did you add ferrite beads for each flip-flops? I wish they are at the bottom side.

There are no ferrite beads, only resistors at the input and at the output of the flip-flops to avoid reflection.

Hi Andrea,

Really, an optical output (TWSAFB-OIR optical output interface & reclocker)?

So no worries optical out to a Chord DAC (optical in)?

I delayed my Ian project 6-12 months as I decided on a 12V Intel i9 low latency PC build. I'm looking at what the Taiko Extreme is doing and trying to somewhat emulate, but it has to run on battery. The Extreme uses a dual Xeon WS motherboard, but that's too much of a rabbit hole and I don't want to run on mains.

SGM Extreme Music Server – Taiko Audio

I'm skipping the low power, low CPU endpoint and trying to jump straight into a high CPU build.

Since I have time and flexibility to re-architect my build, if you're doing optical out then I can plan ahead and adjust as I need time to complete my PC build anyways this year.

Cheers

Really, an optical output (TWSAFB-OIR optical output interface & reclocker)?

So no worries optical out to a Chord DAC (optical in)?

I delayed my Ian project 6-12 months as I decided on a 12V Intel i9 low latency PC build. I'm looking at what the Taiko Extreme is doing and trying to somewhat emulate, but it has to run on battery. The Extreme uses a dual Xeon WS motherboard, but that's too much of a rabbit hole and I don't want to run on mains.

SGM Extreme Music Server – Taiko Audio

I'm skipping the low power, low CPU endpoint and trying to jump straight into a high CPU build.

Since I have time and flexibility to re-architect my build, if you're doing optical out then I can plan ahead and adjust as I need time to complete my PC build anyways this year.

Cheers

Last edited:

The TWSAFB-OIR is not not really an optical output, it's an optical isolation interface.

All the signals from the FIFO Lite come via copper and also the output connectors provided by the OIR have to be connected to coaxial cables.

Optical interface is very jittery.

The optical isolator are used to isolate the clean part which comes directly from the master clock from the dirty signals coming from the FPGA, to avoid any interference between the two domains.

Finally, the dirty signals are reclocked by the master clock after the isolators.

The TWSAFB-OIR has to be used only with DAC switching on the BCK, like the PCM1704 and the PCM1794.

The other DAC, where the most crucial signals are the LRCK or the MCK, don't need the OIR.

In these case you can use the TWSAFB-OI which isolates from the FPGA but it does not perform the reclock (not needed since the MCK and the LRCK come directly from the clean clock domain).

The DAC Lite does not need any isolation interface.

All the signals from the FIFO Lite come via copper and also the output connectors provided by the OIR have to be connected to coaxial cables.

Optical interface is very jittery.

The optical isolator are used to isolate the clean part which comes directly from the master clock from the dirty signals coming from the FPGA, to avoid any interference between the two domains.

Finally, the dirty signals are reclocked by the master clock after the isolators.

The TWSAFB-OIR has to be used only with DAC switching on the BCK, like the PCM1704 and the PCM1794.

The other DAC, where the most crucial signals are the LRCK or the MCK, don't need the OIR.

In these case you can use the TWSAFB-OI which isolates from the FPGA but it does not perform the reclock (not needed since the MCK and the LRCK come directly from the clean clock domain).

The DAC Lite does not need any isolation interface.

- Home

- Source & Line

- Digital Line Level

- The Well synchronized asynchronous FIFO buffer - Slaved I2S reclocker