I got this covered already, RPI with Kali FiFo buffer to the DAM1021.

I believe you are wrong.

This way you are trying to solve the source-dependence of the DAM improving the source.

But unfortunately you cannot solve the issue because after your FIFO the DAM continues to track the input with its PLL and its 5 EUR oscillator suitable for telecommunication but not for digital to analog conversion.

It's almost a paradox: you could use state of the art clocks in your FIFO buffer and then you will vanish all the benefits with the SI514 installed in the front end of the DAM.

Again, you are the customers so you should ask the designer to improve the front end of the DAM.

The DAM1021 uses the Si570, not the best, but not a bad clock either. I’d love to hear your technical line of reasoning why you feel this is too much of a compromise as Soren (Soekris) is intimately familiar with the need for a low-jitter clock and used the Si570 for a reason.

https://www.silabs.com/documents/public/data-sheets/si570.pdf

https://www.silabs.com/documents/public/data-sheets/si570.pdf

P.s. Soekris specifies clock jitter to be <1ps, good luck with beating that, as that’s an excellent specification.

The DAM1021 uses the Si570, not the best, but not a bad clock either. I’d love to hear your technical line of reasoning why you feel this is too much of a compromise as Soren (Soekris) is intimately familiar with the need for a low-jitter clock and used the Si570 for a reason.

https://www.silabs.com/documents/public/data-sheets/si570.pdf

It looks like my DAM1021 has the SI514 and not the SI570.

However, as I said several times (I'm getting tired) both SI514 and SI570 are very high phase noise oscillators.

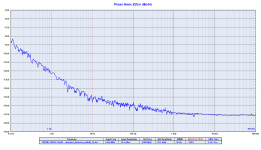

It's clear from their datasheet and more clear from the measurements

Reference DAC Module - Discrete R-2R Sign Magnitude 24 bit 384 Khz

About the jitter calculation and the useless of that such measurements for digital ausio I'm very tired to repeat the same things, please take a look at this link where you can find plenty of informations

The Well Tempered Master Clock - Building a low phase noise/jitter crystal oscillator

Last edited:

P.s. Soekris specifies clock jitter to be <1ps, good luck with beating that, as that’s an excellent specification.

Not so difficult as you think, please take a look at the following plot: the jitter is 43fs and it's calculated with a suitable integration bandwidth, not starting at 100 Hz from the carrier like in the SI570 datasheet, that's a bandwidth suitable for telecommunication but not for digital audio.

Attachments

About the jitter calculation and the useless of that such measurements for digital ausio I'm very tired to repeat the same things

Forget about crystal jitter in R2R application. You can't clock ladder switches at any acceptable fundamental freq, so divider circuit phase noise will dominate anyway.

@andrea,

As I’ve been a long time friend of Pat (Jocko Homo), I know the impact a good clock can have. Unfortunately it is all application specific, at some point a good clock is good enough as other things are more important. Trying to gain that last 20 or even 30dB of jitter reduction quickly brings you into the realm of diminishing returns and the subjectionivist approach of only being able to hear the differences.

As I’ve been a long time friend of Pat (Jocko Homo), I know the impact a good clock can have. Unfortunately it is all application specific, at some point a good clock is good enough as other things are more important. Trying to gain that last 20 or even 30dB of jitter reduction quickly brings you into the realm of diminishing returns and the subjectionivist approach of only being able to hear the differences.

@andrea,

As much as I appreciate your undoubtedly hard work, it is crucial that you’re able to accurately describe and illustrate with measurements the validity of your approach. If you’re too ‘tired’ to do that it takes away a lot of (all?) of the appeal your project has. If you want to advance the fine art of audio engineering it helps to offer a clear, concise and well researched primer so the prospective customer knows there’s some solid engineering behind it. Suggesting people should cobble together bits and pieces of the information they seek by reading through monster threads is a disservice to those same customers. Please make the effort to present your project, document it well, point out the benefits of your approach and illustrate them with measurements.

As much as I appreciate your undoubtedly hard work, it is crucial that you’re able to accurately describe and illustrate with measurements the validity of your approach. If you’re too ‘tired’ to do that it takes away a lot of (all?) of the appeal your project has. If you want to advance the fine art of audio engineering it helps to offer a clear, concise and well researched primer so the prospective customer knows there’s some solid engineering behind it. Suggesting people should cobble together bits and pieces of the information they seek by reading through monster threads is a disservice to those same customers. Please make the effort to present your project, document it well, point out the benefits of your approach and illustrate them with measurements.

Forget about crystal jitter in R2R application. You can't clock ladder switches at any acceptable fundamental freq, so divider circuit phase noise will dominate anyway.

It looks like your RF skills are limited.

When you divide down the phase noise improves, theoretically by 6dB for each division.

In the real world we have measured at least the same phase noise of the base oscillator, simply because the oscillator has itself a phase noise of -155dBc at 10 Hz from the carrier that's very difficult to improve since this performance is almost the limit for the best oscillator on the market.

In R2R applicatione the crucial signal is just the LRCK so you can drive the DAC with a phase noise of -155dBc at 10 Hz from the carrier (or with a jitter - useless- of 43 fs if you prefere).

@andrea,

As I’ve been a long time friend of Pat (Jocko Homo), I know the impact a good clock can have. Unfortunately it is all application specific, at some point a good clock is good enough as other things are more important. Trying to gain that last 20 or even 30dB of jitter reduction quickly brings you into the realm of diminishing returns and the subjectionivist approach of only being able to hear the differences.

Wow! you are so pleased with the performance of the Silabs oscillator (or with the performance of the DAM front end if you prefer) that you have installed a FIFO buffer before it.

I believe you are a little confused.

@andrea,

As much as I appreciate your undoubtedly hard work, it is crucial that you’re able to accurately describe and illustrate with measurements the validity of your approach. If you’re too ‘tired’ to do that it takes away a lot of (all?) of the appeal your project has. If you want to advance the fine art of audio engineering it helps to offer a clear, concise and well researched primer so the prospective customer knows there’s some solid engineering behind it. Suggesting people should cobble together bits and pieces of the information they seek by reading through monster threads is a disservice to those same customers. Please make the effort to present your project, document it well, point out the benefits of your approach and illustrate them with measurements.

The measurements have been already presented in the dedicated thread so I cannot publish again them in this thread because they are off topic, since this thread is about the DAM tweaking.

And so I will publish all the detailed informations about the topic of the thread limited to the DAM update.

For other topics, please refere the dedicated threads.

There are specific threads on oscillators, FIFO buffer, power supply and so on.

And soon on discrete DAC.

Really looking forward to it.And soon on discrete DAC.

I suppose the top DAC will use foil resistors?

Cant find any other 0.001% resistors other than foil type

Wow! you are so pleased with the performance of the Silabs oscillator (or with the performance of the DAM front end if you prefer) that you have installed a FIFO buffer before it.

I believe you are a little confused.

No, not confused, just pragmatic. I wanted to use a RPI for streaming audio, but the I2S outputs on the RPI are horrible in terms of jitter, hence a FiFo+reclocker was needed, which is exactly what the Allo Kali offers.

Going forward, as these ad hominem attacks really amount to nothing, I would love to read your well written explanation illustrated by measurements what’s bad about this approach, or the stock DAM1021 for that matter, and why your solution is a verifiably better solution. I know you’ve been a close friend of Pat as well, and you know very well he would’ve told you to put up or shut up, rightfully so I might add.

"Going forward, as these ad hominem attacks really amount to nothing," - still you happily continue to express them a few words later in your post 🙂

//

//

Wow! you are so pleased with the performance of the Silabs oscillator (or with the performance of the DAM front end if you prefer) that you have installed a FIFO buffer before it.

I believe you are a little confused.

"Going forward, as these ad hominem attacks really amount to nothing," - still you happily continue to express them a few words later in your post 🙂

//

So you consider numerous requests for further information ad hominem attacks? Now I am confused ...

When you divide down the phase noise improves, theoretically by 6dB for each division.

Yes, and the more "clear" crystal you'll use, the more divider noise will dominate, give it a try!

😉

In R2R applicatione the crucial signal is just the LRCK so you can drive the DAC with a phase noise of -155dBc at 10 Hz from the carrier (or with a jitter - useless- of 43 fs if you prefere).

Yes, and even Crystec CCHD allow something more or less like this being properly choosen and divided.

By the way - why you riding a spiral around DAM? Design yours PCB and forget about.

No, but "shut up" do.

//

Allow me to illustrate where I am coming from and feel free to poke holes in my line of reasoning rather than acting like a child with the above comment.

The Soekris DACs are a very well respected commercial product, designed and supported by Soren, a very capable engineer. Yet we have andrea making claims that their design is fundamentally flawed. In that case the age old saying applies:

Extraordinary claims require extraordinary evidence

So if you could please point me towards that evidence which factually (i.e. measurements) prove there's a flaw in the Soekris DACs and andrea's solution fixes this. And no, the subjective 'it just sounds better' does not qualify as extraordinary evidence.

Really looking forward to it.

I suppose the top DAC will use foil resistors?

Cant find any other 0.001% resistors other than foil type

The 0.001% tolerance resistors will be used on the Top version of the DAC only, not in the DAC Lite.

They are very expensive so they are not suitable for the DAC Lite.

However the resistors I have already got are wirewound although maybe I will also try the foil type.

The problem is that the Top version of the DAC uses a segmented architecture with the first 5 MSBs thermometer decoded (5 to 31) and also it's sign magnitude notation, so it needs a bunch of resistors and the cost increases a lot with such that resistors.

My only remark was re: "ad hominem".

//

//

Allow me to illustrate where I am coming from and feel free to poke holes in my line of reasoning rather than acting like a child with the above comment.

The Soekris DACs are a very well respected commercial product, designed and supported by Soren, a very capable engineer. Yet we have andrea making claims that their design is fundamentally flawed. In that case the age old saying applies:

Extraordinary claims require extraordinary evidence

So if you could please point me towards that evidence which factually (i.e. measurements) prove there's a flaw in the Soekris DACs and andrea's solution fixes this. And no, the subjective 'it just sounds better' does not qualify as extraordinary evidence.

- Home

- Source & Line

- Digital Line Level

- Implementing a true FIFO buffer with low phase noise clock on the Soekris DAM1021 DAC