Would like to ask again, why BCK and not MCK divided down to sync to DEM (16,17).

MCK is usually fixed, BCK is a multiple of FS.

By using BCK we can satisfy Fdem = 4 X WCK reliably and use the lowest Fdem possible.

Otherwise, with fixed Fdem, you either always run Fdem at 4 X 8 X 44/48 to ensure you get Fdem = 4 X WCK for the highest sample rate, or you accept that there is as low as Fdem = 0.5 WCK for higher sample rates.

At 44.1/48k & 176.4/192khz Fdem using (I2S) BCK or MCK makes zero difference.

Thor

Last edited:

Hi Thenks 🙂

This one:

#6,315

Did You mod something or ot is as it is on the sch? And didYou use same types of ICs for all ICs?

Do You have some signal Measurements?

Thanks 🙂

Here is the logic capture of the output with 1Khz signal :

.

Any builds so far of the latest iteration? Particularly curious about the decoupling to -15V.

MCK is usually fixed, BCK is a multiple of FS.

By using BCK we can satisfy Fdem = 4 X WCK reliably and use the lowest Fdem possible.

Otherwise, with fixed Fdem, you either always run Fdem at 4 X 8 X 44/48 to ensure you get Fdem = 4 X WCK for the highest sample rate, or you accept that there is as low as Fdem = 0.5 WCK for higher sample rates.

At 44.1/48k & 176.4/192khz Fdem using (I2S) BCK or MCK makes zero difference.

Thor

Thanks Thorsten (and Zoran too from the previous post).

Thorsten,

with the two , two stages flip fllops, of your FDEM from Bck pin shematic, it is proof up to 388 K he Fs because the sim mode, correct ? It is Bck divided by 16 ?

I have worked on that layout-wise yesterday nigth. Because all the decoupling caps and all the things from/towards the -15V pin 15, there are a lot of cars (currents) and literrally an autobahn node there... not easy : the Fdem resistors and caps are litterally one one side of current roads from pin 1 to 14 and cross them... it is so-so from a layout point of view to laout FDEM 100% on the bottom side. I am trying to see what I can do with a little more inductance putting them on the top layer where btw it is easier for the decoupling cause it is less roady for DGND/+5V decoupling !

with the two , two stages flip fllops, of your FDEM from Bck pin shematic, it is proof up to 388 K he Fs because the sim mode, correct ? It is Bck divided by 16 ?

I have worked on that layout-wise yesterday nigth. Because all the decoupling caps and all the things from/towards the -15V pin 15, there are a lot of cars (currents) and literrally an autobahn node there... not easy : the Fdem resistors and caps are litterally one one side of current roads from pin 1 to 14 and cross them... it is so-so from a layout point of view to laout FDEM 100% on the bottom side. I am trying to see what I can do with a little more inductance putting them on the top layer where btw it is easier for the decoupling cause it is less roady for DGND/+5V decoupling !

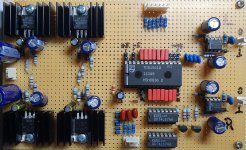

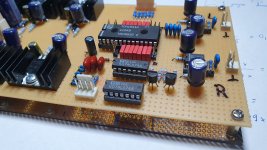

New test setup. Measurements will come.Any builds so far of the latest iteration? Particularly curious about the decoupling to -15V.

Attachments

with the two , two stages flip fllops, of your FDEM from Bck pin shematic, it is proof up to 388 K he Fs because the sim mode, correct ? It is Bck divided by 16 ?

It uses IIS BCK, not SIM BCH and yes, it reliably delivers 4 X Fs IF IIS-BCK = 32+32 X FS.

I have worked on that layout-wise yesterday nigth. Because all the decoupling caps and all the things from/towards the -15V pin 15, there are a lot of cars (currents) and literrally an autobahn node there... not easy :

FDEM is not linked to anything in my design. I tried to be as clear as I can in my schematics.

Anything directly next toTDA1541 goes BELOW THE IC.

Yes, components on both sides. ANYTHING ELSE IS A LOAD OF OLD BOLLOX.

the Fdem resistors and caps are litterally one one side of current roads from pin 1 to 14 and cross them...

Resistors mostly bias. The distance to Pin 16/17 is not crucial. Disatnce is ok.

Fdem is the least problem.

The worst imaginable jitter is 5% of 1/2 LSB by design. So it's a fairly easy node to deal with.

The Cdem pin's to -15V are probably most critical. +5V to -15V second.

Thor

Chunky stuff.I2S attenuator, DEM frequency from BCK/16, shield under the board.

Any builds so far of the latest iteration? Particularly curious about the decoupling to -15V.

Do not expect marvels.

All it does is to avoid first AGND fat trace star ground (works best on testing before) to -15V and sends noise directly to -15V bypassing AGND.

If the TDA1541 was QFN or VSSOP I'd not worry too much. But it ain't.

Thor

Thorsten,

Yes, I meant the parts , resistors and caps that are linked to pin 15/16 to make the Fdem with flip/flop were on the path (crossing) of too much -15V current (when putted on the bottom layer) from the others TDA1541A pins that goes to the -15V pin (bottom layer). I layout the best I can from currents return paths points of view... That's pinball wizard around pin 15, but I try not to draw it the Tommy way !

So I just placed the active FDEM passive parts on the top layer (the caps and resistors but of course the two resistors going to the -15V), anyway as this is also closer to dgnd layer and decoupling, and idem for dcoupling of the flip-flop.

14xDEM are of course at the bottom as the others decoupled pins going to the -15V. The rest that goes to AGND uses vias.

It will be clearer with the layers views.

View the distance between the bck input pin of the FDEM first flip-flop and the front end Bck which is before the sim circuit and attenuation, I use LVDS differential routing so.

So no possibility to take the active DEM source directly at the TDA1541A Bck pin 2 ? (in other words MUST be took before the Sim and attenuation circuit from the outputinf of the Chineese/JLSOUNDS board (I2S output mode) ?

Despite some testimonials in another thread about the JLSounds board being better from his FGPA for the glue logic VS several bulkier flip-flops, I wanted to go the flip-flop simultaneous embeded board path, because it allows more I2S sources choice (SDA Trans, AMARENO, WAVEI/O, JLSOUNDS in I2S mode, etc).

Yes, I meant the parts , resistors and caps that are linked to pin 15/16 to make the Fdem with flip/flop were on the path (crossing) of too much -15V current (when putted on the bottom layer) from the others TDA1541A pins that goes to the -15V pin (bottom layer). I layout the best I can from currents return paths points of view... That's pinball wizard around pin 15, but I try not to draw it the Tommy way !

So I just placed the active FDEM passive parts on the top layer (the caps and resistors but of course the two resistors going to the -15V), anyway as this is also closer to dgnd layer and decoupling, and idem for dcoupling of the flip-flop.

14xDEM are of course at the bottom as the others decoupled pins going to the -15V. The rest that goes to AGND uses vias.

It will be clearer with the layers views.

View the distance between the bck input pin of the FDEM first flip-flop and the front end Bck which is before the sim circuit and attenuation, I use LVDS differential routing so.

So no possibility to take the active DEM source directly at the TDA1541A Bck pin 2 ? (in other words MUST be took before the Sim and attenuation circuit from the outputinf of the Chineese/JLSOUNDS board (I2S output mode) ?

Despite some testimonials in another thread about the JLSounds board being better from his FGPA for the glue logic VS several bulkier flip-flops, I wanted to go the flip-flop simultaneous embeded board path, because it allows more I2S sources choice (SDA Trans, AMARENO, WAVEI/O, JLSOUNDS in I2S mode, etc).

Last edited:

... because at TDA1541A pin 2 the Bck when in feeded Sim mode is 32 inspite of 64 ? Is this the reason to take the Bck for the active DEM before it is proceeded in Sim mode ?

Sorry to re-ask, that glue logic is the not confortable part as far I'm concerned... Well I know, draw the pcb KISS as I have already the shematic (yes you was clear 🙂 )

Sorry to re-ask, that glue logic is the not confortable part as far I'm concerned... Well I know, draw the pcb KISS as I have already the shematic (yes you was clear 🙂 )

Hello Thorsten,

May I ask if in the attenuation circuitry, the caps plugged between the +5V and + Dgnd, should stay very close to the 2.2k resistors linked to the +5V rails ?

Could those caps (the 0.1 uF x 6 , the 1200 uF + 1Uf) be close of the resistors of the attenuation decoupled to the DGND instead being close to the 2k2 R decoupled to +5V ? (Yet a problem of current flowing through the signal traces of the I2S/sim towards the TDA pin 1 to 4 ... Literraly, a DGND layer more just for that could be usefull but it is overkilll ! There is already 6 layers ! with the top and second layer both DGND !

May I ask if in the attenuation circuitry, the caps plugged between the +5V and + Dgnd, should stay very close to the 2.2k resistors linked to the +5V rails ?

Could those caps (the 0.1 uF x 6 , the 1200 uF + 1Uf) be close of the resistors of the attenuation decoupled to the DGND instead being close to the 2k2 R decoupled to +5V ? (Yet a problem of current flowing through the signal traces of the I2S/sim towards the TDA pin 1 to 4 ... Literraly, a DGND layer more just for that could be usefull but it is overkilll ! There is already 6 layers ! with the top and second layer both DGND !

... because at TDA1541A pin 2 the Bck when in feeded Sim mode is 32 inspite of 64 ? Is this the reason to take the Bck for the active DEM before it is proceeded in Sim mode ?

Sorry to re-ask, that glue logic is the not confortable part as far I'm concerned... Well I know, draw the pcb KISS as I have already the shematic (yes you was clear 🙂 )

I thought if the (post SIM conversion) BCK ran continuously (is not stopped), you can use it to synch DEM without problem ??

Hello, thanks !

Is is the speed of the Bck the same before or after the sim mode ? Do I wrongly understood what Thorsten written few posts above and the shematic here where the bck for the active Fdem is took before the "chineese sim board" in spite of its Bck output ?

see the third shematic : https://www.diyaudio.com/community/...ate-nos-dac-using-tda1541a.79452/post-7789873

Maybe also a problem of signal voltage level for the flip flops ? too weak if took after the attenuation circuitry, i.e. at pin 2 of TDA1541A ?

It is not clear to me with sim mode : Bck the same than I2S, no multiplexing in time of the datas (because two datas lines), the pin 1 gives the latch.

If the Bck was the same in sim mode, we could not read 354 and 388 sampling rate materials ? So is the Bck slower in sim mode cause the word length is 32 in spite of 64 ? I'm lost...

Sorry for re-asking the basics, I never was interrested by this before !

Anyway if it is far : LVDS driver as said Thor, to drive the Bck on several inches... Sure it will be easier if the Sim mode was handled bt a Xmos, a FGPA board instead all the flip flops needed for the embeded sim mode conversion ...

Is is the speed of the Bck the same before or after the sim mode ? Do I wrongly understood what Thorsten written few posts above and the shematic here where the bck for the active Fdem is took before the "chineese sim board" in spite of its Bck output ?

see the third shematic : https://www.diyaudio.com/community/...ate-nos-dac-using-tda1541a.79452/post-7789873

Maybe also a problem of signal voltage level for the flip flops ? too weak if took after the attenuation circuitry, i.e. at pin 2 of TDA1541A ?

It is not clear to me with sim mode : Bck the same than I2S, no multiplexing in time of the datas (because two datas lines), the pin 1 gives the latch.

If the Bck was the same in sim mode, we could not read 354 and 388 sampling rate materials ? So is the Bck slower in sim mode cause the word length is 32 in spite of 64 ? I'm lost...

Sorry for re-asking the basics, I never was interrested by this before !

Anyway if it is far : LVDS driver as said Thor, to drive the Bck on several inches... Sure it will be easier if the Sim mode was handled bt a Xmos, a FGPA board instead all the flip flops needed for the embeded sim mode conversion ...

Last edited:

Thanks, clearer, and why it is took before the sim in order it works for the Fdem.

Makes not the thing easier for the layout VS a simplier I2S where the distance between TDA pin 2 and FDEM first flip flop is close...

Makes not the thing easier for the layout VS a simplier I2S where the distance between TDA pin 2 and FDEM first flip flop is close...

This is just for measuring this and that, not for listening. Well, the TDA is clunky in itself, isn't it?Chunky stuff.

I think you can synch to either BCK (pre/post I2StoSIM) so long as it’s continuous (not stopped).Thanks, clearer, and why it is took before the sim in order it works for the Fdem.

It just means you divide by a different number to get fDEM = 4x Fs.

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A