their PCB layout is awfully designed in my opinion, just like a schoolboy made.

I agree. It looks like they started out with a test socket, removed the socket later, but kept the components at their original place, far from the IC. Not ideal in terms of decoupling.

The ES982x takes very little power compared to the ES9038PRO. Well under 100mA in total, no need for a HS.

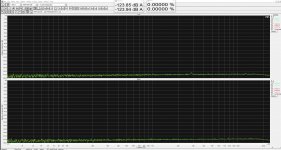

My baseline from an analog loop (digital in/digital out) with two ES9038PRO in mono mode and two ADS127L01 is:

THD @1KHz and @48KHz sampling: -122dB

THD+N @1KHz and @48KHz sampling: -113dB

As others have noted, the ADS127L01 is a little noisy for instrumentation, target is, for the ES9822PRO in mono mode, to bring the THD+N of the analog loop to under -120dB. That's where optimization starts, final target is hopefully under -126dB for both THD and THD+N.

BTW, from my experience with the TI ADS127L01 ADCs these chips also have some inconsistency in the distortion performance. By swapping a few ICs on the same PCB, I got a THD anywhere between -117dB and -123dB. 6dB dispersion is quite a lot, could be related to the effect of process variations on the sigma-delta modulator, but I am speculating...

THD @1KHz and @48KHz sampling: -122dB

THD+N @1KHz and @48KHz sampling: -113dB

As others have noted, the ADS127L01 is a little noisy for instrumentation, target is, for the ES9822PRO in mono mode, to bring the THD+N of the analog loop to under -120dB. That's where optimization starts, final target is hopefully under -126dB for both THD and THD+N.

BTW, from my experience with the TI ADS127L01 ADCs these chips also have some inconsistency in the distortion performance. By swapping a few ICs on the same PCB, I got a THD anywhere between -117dB and -123dB. 6dB dispersion is quite a lot, could be related to the effect of process variations on the sigma-delta modulator, but I am speculating...

Warmer mask the noise spurs? I'm at a loss of a noise process that gets *better* with heat. Certainly something like popcorn noise will be more apparent when the rest of the background is lower.

From what I gathered from IVX post was that the performance improved with a slight increase in operating temperature. And the noise he's speaking of is not broadband its small spikes in the FFT. Certainly the good old AK5394A had significant performance changes when hot vs cold.

I agree. It looks like they started out with a test socket, removed the socket later, but kept the components at their original place, far from the IC. Not ideal in terms of decoupling.

I did ask the EU representative about this. Wondering if their engineers had some input/reason for mounting all the decoupling hardware so far away from the chip. Maybe it was to get the injected rubbish from the de-couplers away from the ground plane right next to the chip or something. Just asking for some sort of logical reasoning behind it but didn't get a reply...Go figure.

Really, has anybody seen a non copyrighted schematic of this ES982x EVM board? I would be interested, and I thought I'd ask here first, before running again in circles with ESS.

I'm not sure what a non-copyrighted version of the schematic would be? Which one are you working from? The one I've got is about 20 pages long.

It's possible that the EVM PDFs aren't under the NDA but I'm not sure. The NDA datasheets have to be personally watermarked for each individual. So when a new, revised, datasheet comes out someone at ESS has to go through the process of watermarking it and then sending it to you.

Now I would have thought, that if you'd signed an NDA, that whenever an update to the documentation was released that they'd automatically send you that update. No such luck. Unless you have been in frequent contact with them, when the updates were released, they assume your project isn't ongoing any more and don't bother to send you anything any more. It's ridiculous.

It's possible that the EVM PDFs aren't under the NDA but I'm not sure. The NDA datasheets have to be personally watermarked for each individual. So when a new, revised, datasheet comes out someone at ESS has to go through the process of watermarking it and then sending it to you.

Now I would have thought, that if you'd signed an NDA, that whenever an update to the documentation was released that they'd automatically send you that update. No such luck. Unless you have been in frequent contact with them, when the updates were released, they assume your project isn't ongoing any more and don't bother to send you anything any more. It's ridiculous.

Something to play with in the ES98X2 QFN EVB 1v2v1.pdf, a small dc offset at adc input might be worth a look. See r97/r18(nf).

register 97 is about GPIOs, register 18 about PCM mapping, how it would be connected to the DC offset? 😱

Warmer mask the noise spurs? I'm at a loss of a noise process that gets *better* with heat. Certainly something like popcorn noise will be more apparent when the rest of the background is lower.

noise-floor getting lower with a hotter chip(didn't try >60C I guess, 40-50C is optimal), and spurs also move over 20kHz.

I agree. It looks like they started out with a test socket, removed the socket later, but kept the components at their original place, far from the IC. Not ideal in terms of decoupling.

yes, it could be a socket, this is reasonable, but still a stupid layout. I was punishing my Chinese when they showed something like that))

register 97 is about GPIOs, register 18 about PCM mapping, how it would be connected to the DC offset? 😱

I think he was talking about resistors in the input stage of the evaluation board.

I found the reason for the noise burst, it is PCB related issue. My earlier PCB has no such problem with any particular 9822 chips. I'll check where exactly I made the difference and modify a critical PCB area back.

In your implementation, is the ES982x in Master or Slave mode? I wonder if it makes any difference in performance.

Interesting, any particular reason why? For my USB instrumentation application I would think the natural/simple approach (from an XMOS perspective) would be to use it in Slave mode. I wonder if there's a performance penalty for that, what you got in Master mode is already at the limit of what I am hoping to achieve. For the ADS127L01 ADC I had no option but Slave mode, since the chip Frame Mode is not supported in Master mode.

I know the XMOS chip can act as an I2S Slave, only that I'm trying to avoid going too deep into that XMOS abomination.

I know the XMOS chip can act as an I2S Slave, only that I'm trying to avoid going too deep into that XMOS abomination.

Last edited:

If it's like ES9102 it has two slave modes: with the onboard jitter eliminator ASRC/DPLL (in which case it will resample the signal) and without it (synchronous mode). I think there's an obscure register setting about this hidden somewhere in the documentation.

If you want to use it for measurement purposes both DAC and ADC should be synchronized...

If you want to use it for measurement purposes both DAC and ADC should be synchronized...

I think there's an obscure register setting about this hidden somewhere in the documentation.

At the first glance, the ES9822 data sheet doesn't mention anything about such a register. But then there are so many "Reserved" bits and registers, who knows?

At least DAC - ES9038Q2M has the 128xFs synchronous mode by default, no switching required.

The ES9822 ADC has no ASRC documented, only the I2S outputs can be in slave mode (with the external clocks synchronous to the master clock to allow reading the data out in time). ASRC from clean master clock to jittery I2S clock would be unusual.

The ES9822 ADC has no ASRC documented, only the I2S outputs can be in slave mode (with the external clocks synchronous to the master clock to allow reading the data out in time). ASRC from clean master clock to jittery I2S clock would be unusual.

Last edited:

- Home

- Design & Build

- Equipment & Tools

- ADCs and DACs for audio instrumentation applications