Thanks Subsoniks .... very informative link.

Wonder how much the extra LDOs will benefit performance in real life.

The beads might be more effective at the frequencies where the fast clock/data signals can have influence on the supply voltage.

Some very good points on the pop reduction circuit. Will look into this a bit more.

Wonder how much the extra LDOs will benefit performance in real life.

The beads might be more effective at the frequencies where the fast clock/data signals can have influence on the supply voltage.

Some very good points on the pop reduction circuit. Will look into this a bit more.

Member

Joined 2018

Hi Baldin-San, I guess you can finish designing the rev2 board.

CyberPit

Well, In the point view of noise, some noise level differences might be exists. I'm not sure on this point, because it's around -130dB world and it's not averaged capture. But I can say in the point of view Jitter, the spread of 12kHz spectrum was slightly to be narrowed and surround noise was flattened with (33nF//100nF) case remarkably.The last 2 pictures of the distortion + noise, there also it seems that that normal filter walues are the best .... noise raises quite some with the 100nF.

I used a spec of probe 250Mz 10pF 1M ohms for connecting. Especially Crystal oscillation is very sensitive part, because the impedance of probe @12.288MHz is around 1.3k ohms. It seems a heavy load for ADAU1701integrated crystal oscillator circuit. My FreeDSP Classic SMD A/B board design has a 74LV541A buffer for driving external DACs already, so I decided to measure the buffered output in this experiment. Logic gate fan-in is not a heavy than probe as you mentioned before.😀One question: you mention using a 74LV541A in the first example ... is this just for buffering and better measurements?

As I mentioned in a previous post, I don´t get a very sharp square on OSCO on a scope ....

In version 2 I'll have 2 x PCM5102A and both connected to OSCO with each a 100 ohm resistor.

Was wondering if a high speed buffer would be better .... on the other hand a PCM5102A only draws 10uA at the logic input (at 3.3V that is 330k ohm impedance), so with 2 DACs is a load on OSCO of 165k ohm.

CyberPit

It's usually the capacitance, both driven input and parasitic, that justifies a buffer on a CLK line. Especially now that you're in the world of 4-layer PCBs, even just a couple centimeters of trace can have appreciable capacitance.

The 74LVC1G series are awfully handy for such tasks.

I try to avoid X7Rs and other high capacitance types in loop filters -- the value change with temperature would worry me enough, but there are usually leakage changes over temp, too.

Cheers

The 74LVC1G series are awfully handy for such tasks.

I try to avoid X7Rs and other high capacitance types in loop filters -- the value change with temperature would worry me enough, but there are usually leakage changes over temp, too.

Cheers

Last edited:

Hmmm, can't really find any specification of the OSCO drive capability.

Not so sure the 100 ohm resistors between OSCO and MCLK on the PCM5102As are a dood idea ... if looking into any capacity, it will result in a low pass filter. Good for "taking" the edge of very high speed signals, but maybe not such a good idea for the clock.

Well I can try to short them out when finished to see any difference.

Anyway I think the probe and scope I'm using is not fast enough to capture the clock well enough, and at least is causing the waveform degradation to some extent.

@CyberPit, I was thinking about your test of the different PLL LPF configurations ..... if it it the setup, where you send it to a PCM5102A running in PLL mode, and then measuring the distortion + noise at the output, I'm thinking that the PLL in the DAC will correct most of the jitter if any from the DSP ..... but probably you where measuring on the internal DAC output of the ADAU1701, right?

Not so sure the 100 ohm resistors between OSCO and MCLK on the PCM5102As are a dood idea ... if looking into any capacity, it will result in a low pass filter. Good for "taking" the edge of very high speed signals, but maybe not such a good idea for the clock.

Well I can try to short them out when finished to see any difference.

Anyway I think the probe and scope I'm using is not fast enough to capture the clock well enough, and at least is causing the waveform degradation to some extent.

@CyberPit, I was thinking about your test of the different PLL LPF configurations ..... if it it the setup, where you send it to a PCM5102A running in PLL mode, and then measuring the distortion + noise at the output, I'm thinking that the PLL in the DAC will correct most of the jitter if any from the DSP ..... but probably you where measuring on the internal DAC output of the ADAU1701, right?

Member

Joined 2018

Hi Baldin-San,

If I use FreeDSP Classic SMD A/B plus-II board CH4/5. It will cascaded PLL inside of PCM5102A also. So, it will be a different one and hard to know the actual ADAU1701 internal PLL loop filter cut-off depended characteristics. That's why I used ADAU1701 embedded DAC for this experiment. Maybe someone has I2S to PCM5102A Jittter reduction (or amplify?) performance test result information.

Further investigation requires I2S read-out/write equipment to know the separate ADC/DAC Jitter characteristic...

CyberPit

The last two zoom-up audio spectrum are an ADAU1701 on the FreeDSP Classic SMD A/B's ADC->DSP(200 Samples Delay Buffer)->DAC overall audio jitter performance. So it contains ADC side jitter afftect + DAC side one also.@CyberPit, I was thinking about your test of the different PLL LPF configurations ..... if it it the setup, where you send it to a PCM5102A running in PLL mode, and then measuring the distortion + noise at the output, I'm thinking that the PLL in the DAC will correct most of the jitter if any from the DSP ..... but probably you where measuring on the internal DAC output of the ADAU1701, right?

If I use FreeDSP Classic SMD A/B plus-II board CH4/5. It will cascaded PLL inside of PCM5102A also. So, it will be a different one and hard to know the actual ADAU1701 internal PLL loop filter cut-off depended characteristics. That's why I used ADAU1701 embedded DAC for this experiment. Maybe someone has I2S to PCM5102A Jittter reduction (or amplify?) performance test result information.

Further investigation requires I2S read-out/write equipment to know the separate ADC/DAC Jitter characteristic...

CyberPit

Hi CyberPit-San

Thanks. That's perfect 🙂

No need for further investigations 🙂

I'll be running the PCM5102A in clocked mode and will only run 48kHz

On another note:

I'll insert a few more beads to the analog supply of the DSP, it's only two more 0805 😉

Thanks. That's perfect 🙂

No need for further investigations 🙂

I'll be running the PCM5102A in clocked mode and will only run 48kHz

On another note:

I'll insert a few more beads to the analog supply of the DSP, it's only two more 0805 😉

Hi everybody, thanks for this wonderful and full of information thread!

Baldin - did you get better S/N or audible improvement using the 5102 over the inbuilt DACs?

I have a Powersoft amp that uses the 1701 with both the integrated DACs and some CS4398. I could personally not hear a difference when A/B testing.

Baldin - did you get better S/N or audible improvement using the 5102 over the inbuilt DACs?

I have a Powersoft amp that uses the 1701 with both the integrated DACs and some CS4398. I could personally not hear a difference when A/B testing.

Hey aragorus

Have not had the possibility or time to do any measurements yet.

For me the most important feature with the 5102 is the anti pop function ... size and cost for this way of solving it is small and efficient.

So will continue with this solution for now.

Have just gotten some new PCBs home with 2 x 5102 for a 2 channel solution.

Have also dropped the output pot, as using a single pot cobbled to the general IO and using a vol function, works well

Have not had the possibility or time to do any measurements yet.

For me the most important feature with the 5102 is the anti pop function ... size and cost for this way of solving it is small and efficient.

So will continue with this solution for now.

Have just gotten some new PCBs home with 2 x 5102 for a 2 channel solution.

Have also dropped the output pot, as using a single pot cobbled to the general IO and using a vol function, works well

That sounds good!

I feel like it can very fast become a very complicated PCB.

I'm using some of the adau1401/1701 boards.

Doing a digitally ballanced input and output.

Sometimes the noise floor on the HF channel is a bit too high. In those cases I use a 64 ohm resistor between output 1 and 2 to bring the output level down, while maintaining a fairly high digital level.

This is probably not the most elegant solution to reduce the noise floor, but it works like a charm for me.

I feel like it can very fast become a very complicated PCB.

I'm using some of the adau1401/1701 boards.

Doing a digitally ballanced input and output.

Sometimes the noise floor on the HF channel is a bit too high. In those cases I use a 64 ohm resistor between output 1 and 2 to bring the output level down, while maintaining a fairly high digital level.

This is probably not the most elegant solution to reduce the noise floor, but it works like a charm for me.

Hello everyone.

I would like to be able to load data from the ADAU1701 and save it into it. I would like to build my own program for managing the DSP but I don't know how to communicate with the device (obviously I can already send and receive data from the USB).

Thank you all.

I would like to be able to load data from the ADAU1701 and save it into it. I would like to build my own program for managing the DSP but I don't know how to communicate with the device (obviously I can already send and receive data from the USB).

Thank you all.

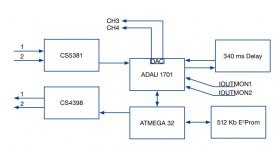

The Audiodevelopers.com site has a number of articles on how to interface to the ADAU1701 and provide real-time control. There are a couple of libraries on the web that would help with the low-level communications, but there isn't much posted yet about high-level interactions. Eventually I'll be posting some code that will make the high-level interactions a lot easier. There are some previews of some high-level libraries in this article: http://www.audiodevelopers.com/12-arduino-code-overview/

The biggest challenge in working with these SigmaStudio devices is that they use a compiler (SigmaStudio) to define the DSP architecture. As a result, you need to process the output of the compiler to figure out the addresses for the DSP cells. So, there is some extra code needed to derive that info--I'll be posting details about that code in an upcoming article.

The biggest challenge in working with these SigmaStudio devices is that they use a compiler (SigmaStudio) to define the DSP architecture. As a result, you need to process the output of the compiler to figure out the addresses for the DSP cells. So, there is some extra code needed to derive that info--I'll be posting details about that code in an upcoming article.

- Home

- Source & Line

- Digital Line Level

- ADAU1701 based DSP for sub or 2 way