Thanks.

Im no technician, but i listen. So in my case: Rpi with replaced onboard regulators and supplied 1.8, 3.3 and 5v clean linear power, has Ian's IsolatorPi to output "clean I2s", then i2s signal to Ian's Fifo then to Ian's isolator again, then to Ian's dualxo board (with your old driscoll xo), then to my dac - i still felt obvious sound changes after ufl connection between Rpi and Fifo and also after ufl connection from Fifo to isolator to Dualxo board. All devices are powered with very high quality lineqr power supplies.

So my subjective opinion, that his isolators are still prone to let source and also airborn picked noise through.. and therefore both sides ufl connections carry big benefits.

Hope to try your fifo and finally hope to get proper isolation of the source.

There is a great difference between our FIFO Lite and Ian's FIFO: the FIFO buffer is slaved to the master clock that resides in a different time and electrical domain.

In our FIFO the LRCK comes directly from the master clock, it does not cross the FPGA, so it's well isolated from the source.

Hi Andrea,

Any direct DSD support?

-Raja

No direct DSD, at least in this version.

To clarify better, let examin a 3 bit ladder DAC as example.

Thermometer/Dec/Switch at 1 time

0000000 0 -

0000001 1 1

0000011 2 1

0000111 3 1

0001111 4 1

0011111 5 1

0111111 6 1

1111111 7 1

always 1 resistor at 1 time

R2R/Dec/Switch at 1 time

000 0 -

001 1 1

010 2 2

011 3 1

100 4 3

101 5 1

110 6 2

111 7 1

4 times 1 resistor at 1 time

2 times 2 resistors at 1 time

1 time 3 resistors at 1 time

Just curious, wouldn't gray code do the trick, or at least improve on pure R2R?

No direct DSD, at least in this version.

That’s a shame. Will wait.

Just curious, wouldn't gray code do the trick, or at least improve on pure R2R?

We have no transiction on the first MSBs since we use sign magnitude notation, so the glitch should be already less than in a classical 2's complement notation DAC.

OT but in your (lovely) streamer project would you mind sharing the source of those round hdmi and ethernet sockets please. Beats cutting square holes!

OT but in your (lovely) streamer project would you mind sharing the source of those round hdmi and ethernet sockets please. Beats cutting square holes!

AliExpress

Yueqing Elewind Electric Co., Ltd. - Negozio per Piccoli Ordini Online, I piu Venduti e altro su AliExpress

Hi,

Could you include a mode which outputs an SPI format for the new TI R2R DAC11001 ? Im working on a MCU based solution at the moment, but of course it would be much better to have this capability in the FIFO, so no further conversion would be needed.

Could you include a mode which outputs an SPI format for the new TI R2R DAC11001 ? Im working on a MCU based solution at the moment, but of course it would be much better to have this capability in the FIFO, so no further conversion would be needed.

Thankyou

Andrea I just noticed my information isn't in the spreadsheet however I did receive and invoice and is paid. I shall update spreadsheet

Andrea I just noticed my information isn't in the spreadsheet however I did receive and invoice and is paid. I shall update spreadsheet

Hi,

Could you include a mode which outputs an SPI format for the new TI R2R DAC11001 ? Im working on a MCU based solution at the moment, but of course it would be much better to have this capability in the FIFO, so no further conversion would be needed.

Not in this version, maybe in a future update.

RMAF11: Digital Jitter and Volume Controls, Martin Mallison, CTO, ESS Technology - YouTube

Found this old video. Watch from 15:55 onward on jitter. It does explain in the video that PLL does not isolate the source clock, and PLL has weaknesses.

It'll be very interesting to see the performance of your FIFO front end, vs. Soekris' front end.

Found this old video. Watch from 15:55 onward on jitter. It does explain in the video that PLL does not isolate the source clock, and PLL has weaknesses.

It'll be very interesting to see the performance of your FIFO front end, vs. Soekris' front end.

Last edited:

RMAF11: Digital Jitter and Volume Controls, Martin Mallison, CTO, ESS Technology - YouTube

Found this old video. Watch from 15:55 onward on jitter. It does explain in the video that PLL does not isolate the source clock, and PLL has weaknesses.

It'll be very interesting to see the performance of your FIFO front end, vs. Soekris' front end.

I believe it was enough obvious, a true buffer is needed to isolate the DAC from the source.

I'm curious too.

@Andrea

Did you receive my PN?

Yes, and I replied the same day.

Plese, let me know if you have received the answer.

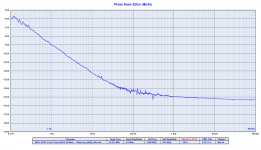

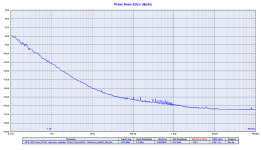

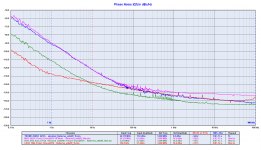

Preliminary measurements

I attach some phase noise plots of the FIFO Lite:

- MCLK output

- BCK output (FIFO Lite + Reclocker)

- LRCK output

- Comparison (including the base DRIXO 24.576 MHz oscillator)

I attach some phase noise plots of the FIFO Lite:

- MCLK output

- BCK output (FIFO Lite + Reclocker)

- LRCK output

- Comparison (including the base DRIXO 24.576 MHz oscillator)

Attachments

- Home

- Source & Line

- Digital Line Level

- The Well synchronized asynchronous FIFO buffer - Slaved I2S reclocker