Thanks luchoh! Ray informed me by PM that he has contacted the designer of the reclocking board, who almost certainly knows the answer. If not or if he doesn't reply, then I would appreciate it very much if you could measure it.

To explain the issue:

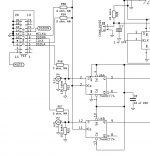

Somehow Ray manages to get a BeagleBone to produce raw DSD bit streams. I don't know the details, only that it involves a powerful computer running HQPlayer. Those DSD bit streams get reclocked by PPY's ReClocker as described on this website: https://puredsd.ru/ in the schematic https://puredsd.ru/BBBreclk.pdf

If on the reclocking board, the rising edge of BCK2 gets clocked into U8 at the same master clock edge as the transitions of the LRCK2 into U9 and those of DATA2 into U10, then the hold time that is available for the input flip-flops of the raw DSD valve DAC can be negative when they run on the bit clock. That's because due to exemplaric spread, U8 could have a slightly longer delay than U9 and U10. The input flip-flops of the raw DSD valve DAC require 0 ns of hold time, so a negative value is a violation.

If, however, the transitions of LRCK2 and DATA2 are clocked in at the same master clock edge as the falling edge of BCK2, then there is no problem.

In raw DSD mode, LRCK2 is a level shifted version of the DATA_DSD1 signal coming from pin 30 of the BeagleBone connector J1, DATA2 is a level shifted version of the DSD2 signal from pin 41 of J1 and BCK2 is a level shifted version of the BCK signal coming from pin 31 of J1.

So all in all, the question is whether the transitions of the data signals DATA_DSD1 and DSD2 at pins 30 and 41 of the BeagleBone connector happen near the rising or near the falling edge of the bit clock BCK on pin 31. When you connect the bit clock and a data signal to a dual channel oscilloscope and trigger it on the bit clock, it should be easy to see that.

To explain the issue:

Somehow Ray manages to get a BeagleBone to produce raw DSD bit streams. I don't know the details, only that it involves a powerful computer running HQPlayer. Those DSD bit streams get reclocked by PPY's ReClocker as described on this website: https://puredsd.ru/ in the schematic https://puredsd.ru/BBBreclk.pdf

If on the reclocking board, the rising edge of BCK2 gets clocked into U8 at the same master clock edge as the transitions of the LRCK2 into U9 and those of DATA2 into U10, then the hold time that is available for the input flip-flops of the raw DSD valve DAC can be negative when they run on the bit clock. That's because due to exemplaric spread, U8 could have a slightly longer delay than U9 and U10. The input flip-flops of the raw DSD valve DAC require 0 ns of hold time, so a negative value is a violation.

If, however, the transitions of LRCK2 and DATA2 are clocked in at the same master clock edge as the falling edge of BCK2, then there is no problem.

In raw DSD mode, LRCK2 is a level shifted version of the DATA_DSD1 signal coming from pin 30 of the BeagleBone connector J1, DATA2 is a level shifted version of the DSD2 signal from pin 41 of J1 and BCK2 is a level shifted version of the BCK signal coming from pin 31 of J1.

So all in all, the question is whether the transitions of the data signals DATA_DSD1 and DSD2 at pins 30 and 41 of the BeagleBone connector happen near the rising or near the falling edge of the bit clock BCK on pin 31. When you connect the bit clock and a data signal to a dual channel oscilloscope and trigger it on the bit clock, it should be easy to see that.

Last edited:

Thank You Marcel

I did not know the CD Replay was not an option and the AK4137 Board would be a solution to produce the CD Replay.

I am not a builder of any electronic devices, much of the tech talk is not comprehended by myself, and I would not be able to contribute to these discussions.

I am intending on discussing this build with a EE who has done builds for me throughout many years, at present the EE is not available, I have to wait a little longer to see if they are able to support me with the build of this one.

What ever the outcome, the Design has my attention, and picking up on the feedback of the builds will prove interesting to follow.

Trying to cut down on the jargon:

The original valve DAC as I have it here can be connected to any CD player with a digital output, in fact I have it connected to one. It contains a lot of digital circuitry that converts the signal from the CD player into something that is easier to process for a simple DAC circuit. The digital circuitry I use is very flexible, so I could do the processing exactly as I wanted to, but it is also expensive and difficult to solder with a normal soldering iron.

Ray does a similar conversion with a computer running a program called HQPlayer, so he asked me if it would be possible to make a variant of the valve DAC without all the digital signal processing stuff. That's the variant he has built and that he has started a group buy for, we call it the raw DSD version or DSD-only version. As it doesn't have the digital processing on board, there is no way to directly connect a CD player to it.

The AK4137 board would be a third way to convert the signal from (for example) a CD player into something that is easier to process for a simple DAC circuit. It should be possible to connect it in between a CD player and the raw DSD valve DAC, although no-one has tried that yet.

Although Ray and I don’t know each other, we crossed paths many times in our DSD journey.Somehow Ray manages to get a BeagleBone to produce raw DSD bit streams. I don't know the details, only that it involves a powerful computer running HQPlayer. Those DSD bit streams get reclocked by PPY's ReClocker as described on this website: https://puredsd.ru/ in the schematic https://puredsd.ru/BBBreclk.pdf

Let me explain a bit better the situation.

1. In order to produce DSD from BBB, one needs a a Linux driver. Unfortunately, the driver may not be sufficient, though don’t quote me on that. The issue is that BBB has only 48x rate clock. Without an external clock, BBB is not a great device for i2s streaming duty.

2. The first successful attempt at DSD (and I2S for that matter) via BBB was a joint effort from Twistedpear Audio and miero. The latter wrote the drive and the former implemented Hermes (isolator) and Cronus (reclocker). The initial implementation was targeted to serve the TPA ESS9018-based DAC - Buffalo.

3. After that, we repurposed the Hermès/Cronus for the DSC2 effort (Pure DSD DAC), which is the predecessor of the initiative this thread is committed to.

4. The main force behind DSC2 was ppp - the links you included are from his site. I cannot tell if he wrote a special driver, but unlike the miero’s (Botic) driver that can be used in Debian, ppp created his own Linux distro and after that - his own version of Hermès/Cronus - the reclocker you mentioned.

Having said all that, the signals after ppp’s reclocker and Hermès/Cronus may be different. I think at least the Botic driver can configure the parameters you’re interested in. I don’t know about ppp’s version.

I’m happy to provide more information.

...BeagleBone to produce raw DSD bit streams...

The how of it appears to be explained in a thread at: Simple DSD SRC for BeagleBone

Last edited:

The how of it appears to be explained in a thread at: Simple DSD SRC for BeagleBone

Not exactly. I was describing the HQPlayer (or any software conversion for that mater) path.

The above post describes the hardware conversion option.

Although Ray and I don’t know each other, we crossed paths many times in our DSD journey.

Indeed. A number of us seem to be on a DSD road of discovery and our paths cross every now and then.

Somehow Ray manages to get a BeagleBone to produce raw DSD bit streams. I don't know the details...

The 'magic' of getting DSD data out of the Beaglebone (BBB) is not something I can take any kudos for and luchoh has given credit where it is due for the software that sits on the BBB. We wouldn't be where we are without Miero (developer of the original 'botic' distribution) and ppy (for his hardware solutions and further development of botic). We also shouldn't forget Jussi (Signalyst), the author of HQP and the related NAA (Network Audio Appliance) software that sits on the BBB.

Just for clarity, all the heavy-lift resampling takes place in HQP on a powerful workstation. The resulting DSD data can be output from the workstation (say via USB) or can be streamed over a network to an NAA computer where it is received and 'handed over' to the botic-based driver or a USB-attached soundcard device (such as Amanero or JLSounds). Apart from several BBB-based NAAs I also have an Intel NUC (small and totally silent) running as an NAA into which I plug USB DACs.

Incidentally, in case it isn't obvious, this upstream infrastructure isn't DSD specific and works exceptionally well for PCM data too.

Last edited:

So if I understand luchoh correctly, everything Ray uses is designed to drive a DSC2 DAC. There appear to be many versions of those, where can one find the schematics of the precise model that the reclocker board was designed for?

There are a couple of details different from the separate reclocker board. Is the separate reclocker board meant to work with https://puredsd.ru/DSC252.pdf ?

This is the version of isolator and reclocker that Mr. nautibuoy is using. His photo was posted on post #407

https://puredsd.ru/BBBreclk.pdf

There is also this article explaining how the entire software and hardware chain works.

Network Audio DAC

https://puredsd.ru/BBBreclk.pdf

There is also this article explaining how the entire software and hardware chain works.

Network Audio DAC

Last edited:

I know, but is it compatible with https://puredsd.ru/DSC252.pdf ? If so, then Ray can use the bit clock without any hold time issues.

The circuit in https://puredsd.ru/DSC252.pdf is positive edge triggered, like the raw DSD valve DAC, but it requires a set-up time of 7.2 ns and a hold time of 5.3 ns. The raw DSD valve DAC only needs 5 ns and 0 ns, so anything that meets the timing requirements of https://puredsd.ru/DSC252.pdf should also work with the raw DSD version of the valve DAC running on the bit clock.

By the way, I put the 0 ohm resistor and jumper changes needed when you use the bit clock in the opening post.

The circuit in https://puredsd.ru/DSC252.pdf is positive edge triggered, like the raw DSD valve DAC, but it requires a set-up time of 7.2 ns and a hold time of 5.3 ns. The raw DSD valve DAC only needs 5 ns and 0 ns, so anything that meets the timing requirements of https://puredsd.ru/DSC252.pdf should also work with the raw DSD version of the valve DAC running on the bit clock.

By the way, I put the 0 ohm resistor and jumper changes needed when you use the bit clock in the opening post.

My guess is that it is a generic reclocking circuit using flip flops. My guess is that it is compatible with the DSC252 dac and others.

An article that I found regarding this is here

Synchronous Reclocking? | H i F i D U I N O

I think we need to measure just to be sure.

This brings up an interesting question: Does the valve dac need reclocking from a BeagleBone Black? We are sending a master clock back to a BBB already.

An article that I found regarding this is here

Synchronous Reclocking? | H i F i D U I N O

I think we need to measure just to be sure.

This brings up an interesting question: Does the valve dac need reclocking from a BeagleBone Black? We are sending a master clock back to a BBB already.

Last edited:

A question about clock: Does the valve dac accept sine wave? If not, I will pass the clock through a schmitt trigger to convert it to square wave.

Why I ask? Apparently the new well tempered clock designs (at Group Buys and Digital Line Level) output sine wave and need additional circuit to convert to square wave.

Why I ask? Apparently the new well tempered clock designs (at Group Buys and Digital Line Level) output sine wave and need additional circuit to convert to square wave.

Last edited:

The raw DSD valve DAC was designed for TTL-compatible square waves, so I'd definitely convert the clock to a square wave.

Last edited:

This brings up an interesting question: Does the valve dac need reclocking from a BeagleBone Black? We are sending a master clock back to a BBB already.

The raw DSD valve DAC definitely needs an external clock source with reasonably low jitter. The data just need to be stable from 5 ns before to 0 ns after the rising clock edge, they are immediately clocked into a 74AHCT74 (U6 in the schematic).

Attachments

I know, but is it compatible with https://puredsd.ru/DSC252.pdf ?

Yes, that is my understanding Marcel.

I have a DSC2 V2.5.2 but I actually use a Twisted Pear Hermes/Cronus isolator/reclocker (because I already owned it) but I've been considering replacing it with ppy's isolator/reclocker.

Great, then using the bit clock should work (reply to post #737). I'm glad your charity ride went OK this time!

This brings up an interesting question: Does the valve dac need reclocking from a BeagleBone Black? We are sending a master clock back to a BBB already.

I don't understand the question. The Valve DAC just takes data/clock signals as presented and it has no 'understanding' of whether said data has been relocked. The isolator/reclocker just provides good quality data and clock signals to the DAC. The reason a clock signal is set back to the BBB is because it only has one, poor quality, oscilllator so can only natively handle 48KHz family data and has to resample 44.1KHz to 48KHz - not ideal - but this is addressed by using the 44.1K and 48K clock signals from the reclocker. The reason the reclocker also has galvanic isolation between the BBB and the recloker is to prevent the 'noise' from the BBB getting to the DAC.

- Home

- Source & Line

- Digital Line Level

- Valve DAC from Linear Audio volume 13