Input cap

Fab

Yes you are right. I think I misread the datasheet for dimensions…The 250V part fits nicely.

Fab

Hi Twocents

Thinking more about it, if you followed the manual (section 20.1.3.1 and 20.1.3,2) then it means that your Jfet current sources values were correct. Thus, please report your steps results (either « ok « or the value) here :

20.1.3 Adjustment differences

20.1.3.1 Section 8.7 Current Source adjustment

Connect V+ and V- and both PGND and GND to power supply (from 15Vdc to 30Vdc).

Connect TP10 and TP11 to Ground terminal.

Adjust P3 for about 29mV (temporary value) between TP9 and TP10.

Adjust P4 for about 29mV (temporary value) between TP11 and TP12.

20.1.3.2 Section 8.8.5 Adjust current in input stage

Connect V+ and V- and Both PGND and GND to power supply (from 15Vdc to 30Vdc).

Adjust P3 to obtain 180mV (temporary value of 900ma) bias between TP1/TP2.

Adjust P4 to obtain 180mV (temporary value of 900ma) bias between TP3/TP4.

-Report voltage between TP9 and TP10. :_________

- Report voltage between TP11 and TP12.:______

20.1.3.3 Section 8.18 Driver transistors bias adjustment

With about 180mV (900ma) bias between TP1/TP2 or TP3/TP4. Positive side:

Measure Vbe between TP5 and TP1: _______

IQ5pre = Vbe/ 20 Ohms = __________

If the IQ5pre value is not within [40-45] ma then R13 = Vbe / 42ma.

Negative side:

Measure Vbe between TP6 and TP3: _______

IQ6pre = Vbe/ 20 Ohms = __________

If the IQ6pre value is not within [40-45] ma then R14 = Vbe / 42ma.

Note: the final bias for output transistor is expected to be in the range of [1 – 1.3]A thus giving about 45mA as driver current.

20.1.3.4 Section 9 Test assembled board (no load)

With no load on amplifier output (or load higher than 10K Ohms):

Output dc offset are adjusted using P1 only;

Install the meter probe leads between TP1 and TP2(or TP3 and TP4);

Install another meter probes set between Output and Ground;

Turn P1 to center DC offset to < 5mV while monitoring voltage between Output and Ground;

Adjust final output bias current to desired value [1 – 1.3]A (200mV to 260mV with 0.2 Ohms) using P3 and

P4;

I have put in bold instructions so you always connect both grounds so no issue can arise from one missing ground.

If you had succeeded at step 20.1.3.2 to obtain 180mv there is no reason why you cannot get 200 or 260mv across R15 or R16 at steps 20.1.3.4….

Also, ensure you really have 0.2 ohms for R15/16 and not 0.02 ohms.

Ensure Q7 and Q8 are in the right position.

Ensure the thermistors are working well because they are absolutely mandatory for the USSA5B! This is preventing thermal runaway.

At step 20.1.3.2. You can set a lower bias with 20mv for example to see how it goes.

Also I cannot see if R4 is installed from your picture since you seem to have 2 xC1 caps installed.

Fab

Last edited:

Thank you Fab and ggetzoff – I have something to work with now, and a little more hope to recover.

Just to confirm:

- R15 and R16 are 0.22 ohm in my case. I could not get 0.2, so I got 0.22 ohm 3W resistors and they actually measured 0.23 ohm on my cheap component tester. My DMM is not accurate enough for such low resistance. I used the component tester also to measure hFE and match Q’s 1 to 4 (BC547 and BC557)

- I will check again, but almost 100% sure that Q7 and Q8 are in the correct positions

- R4 is mounted, but hidden behind the C1 caps. Yes, there are 2 x 110pF caps in parallel. I could not get 220pF mica caps at the time

- Measurements went well with sections 8.7 Current source adjustment and 8.8.5 Adjust current in input stage.

- Up to this point only V+, V- and PGND was supposed to be connected. I did not connect PGND, so only V+ and V-

- My problem (smoking resistors R15 and R16) started when I connected V+, V- and GND to attempt measurements for section 8.17.1 Adjust output Mosfet current close to intended final bias. At this point I should have skipped to Section 20.1.3.3 of Addendum 2.

- Maybe my problem is that I don’t understand the difference between GND and PGND in this case? Maybe I switched them around? I assumed that for a dual polarity PSU one refers to the outputs as V+ / GND / V-, and that PGND is only connected to the earth on the supply and to the wall socket in case of a short circuit?

I will unfortunately not be able to attend to this for the next two or three weeks.

Just to confirm:

- R15 and R16 are 0.22 ohm in my case. I could not get 0.2, so I got 0.22 ohm 3W resistors and they actually measured 0.23 ohm on my cheap component tester. My DMM is not accurate enough for such low resistance. I used the component tester also to measure hFE and match Q’s 1 to 4 (BC547 and BC557)

- I will check again, but almost 100% sure that Q7 and Q8 are in the correct positions

- R4 is mounted, but hidden behind the C1 caps. Yes, there are 2 x 110pF caps in parallel. I could not get 220pF mica caps at the time

- Measurements went well with sections 8.7 Current source adjustment and 8.8.5 Adjust current in input stage.

- Up to this point only V+, V- and PGND was supposed to be connected. I did not connect PGND, so only V+ and V-

- My problem (smoking resistors R15 and R16) started when I connected V+, V- and GND to attempt measurements for section 8.17.1 Adjust output Mosfet current close to intended final bias. At this point I should have skipped to Section 20.1.3.3 of Addendum 2.

- Maybe my problem is that I don’t understand the difference between GND and PGND in this case? Maybe I switched them around? I assumed that for a dual polarity PSU one refers to the outputs as V+ / GND / V-, and that PGND is only connected to the earth on the supply and to the wall socket in case of a short circuit?

I will unfortunately not be able to attend to this for the next two or three weeks.

Maybe my problem is that I don’t understand the difference between GND and PGND in this case?

I was in the same boat. The build guide has all the details, but they were not clear enough for me. I guess you just connect both GND and PGND to ground, and that's it.

Fab may have more details, if necessary.

I think per Fab and the manual, one of the GND or PGND has a floating ground via a resistor. Which means that you should connect both the grounds to the PSU ground for proper measurement and setup. One of my channels blew up after an year of play because the PGND spade cable because of frequent plugging and unplugging had come out loose and the adjacent resistor blew up. Based on Fab's suggestion now I have made sure that I get a slightly higher wattage 2w resistor and also made sure that the ground cables from the PSU board are tight fit.

Best of luck.

Best of luck.

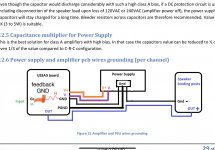

Gnd and PGND

See below extract of manual where I just manually added the isolation R between input/feedback and GND pin. Then you need to connect GND and PGND at the power supply central ground connection. During testing, you can omit PGND in the first steps of the manual but not when you go back. Therefore, I recommend that you always connect both GND and PGND pins to the PSU gnd.

Fab

See below extract of manual where I just manually added the isolation R between input/feedback and GND pin. Then you need to connect GND and PGND at the power supply central ground connection. During testing, you can omit PGND in the first steps of the manual but not when you go back. Therefore, I recommend that you always connect both GND and PGND pins to the PSU gnd.

Fab

Attachments

Hi Harry3Keystone 8191 pcb screw terminals might be better for new boards.

These are good but they take twice the space on the pcb….🙄

It would probably need an increase of USSA5 pcb size….

Fab

It looks like I have good news and bad news. The good news – my second 5B board seems fine and should bias correctly. First want to upgrade the R15 and R16 resistors to 5W. The bad news - on the first board it looks like I blew up the two output transistors (2SA1943, 2SC5200). Waiting for replacements. Time will tell if they are the only damaged components. Will try to replace them without lifting everything off the heatsinks.

I also decided to kick this habit of blowing up amps from now on.

I also decided to kick this habit of blowing up amps from now on.

Hi Twocents

Glad about the good news.🙂

For the bad one, the build manual has been written in steps so you can test and validate after each test step (you will not see that very often, if ever). So you simply remove the failed output bjt and retest the previous steps so when you installed the replaced bjt properly then it will work for sure.

As a precaution, either always use a lightbulb or variac on AC power or small current fuses on each DC rail. I use 2A fuses on each rail during my bench test and never damaged any power transistors even when doing the wrong thing….

Good luck and I support you in your resolution😛

Fab

Glad about the good news.🙂

For the bad one, the build manual has been written in steps so you can test and validate after each test step (you will not see that very often, if ever). So you simply remove the failed output bjt and retest the previous steps so when you installed the replaced bjt properly then it will work for sure.

As a precaution, either always use a lightbulb or variac on AC power or small current fuses on each DC rail. I use 2A fuses on each rail during my bench test and never damaged any power transistors even when doing the wrong thing….

Good luck and I support you in your resolution😛

Fab

Hi AnthonyA

Not yet

I need to finish 5.2 version and then 3.2b. It will be shortly when I have the chance.

Fab

Not yet

I need to finish 5.2 version and then 3.2b. It will be shortly when I have the chance.

Fab

Hi Fab,

I finally continued working on the USSA-3, I'm now testing the input stage.

The manual states:

8.1.2 Adjust voltage in input stage

Connect V+ and V- and PGND (the one close to V-) to power supply (from 15Vdc to 30Vdc).

Adjust P2 for about TBD between TP8 and V-.

Adjust P1 for about TBD between TP7 and V+.

What's the voltage drop (TBD) I should aim for

over the resistors between TP7, TP8 and power supply voltage

or over the input transistors ?

I have a 24vdc PS.

I have the manual "USSA-33 AMPLIFIER BOARD Fab rev06p"

I just see that the manual also states "TBD" in the next testing phases.

Can you give me the voltages/currents the transistors of each stage(input,driver,output) should see ?

I finally continued working on the USSA-3, I'm now testing the input stage.

The manual states:

8.1.2 Adjust voltage in input stage

Connect V+ and V- and PGND (the one close to V-) to power supply (from 15Vdc to 30Vdc).

Adjust P2 for about TBD between TP8 and V-.

Adjust P1 for about TBD between TP7 and V+.

What's the voltage drop (TBD) I should aim for

over the resistors between TP7, TP8 and power supply voltage

or over the input transistors ?

I have a 24vdc PS.

I have the manual "USSA-33 AMPLIFIER BOARD Fab rev06p"

I just see that the manual also states "TBD" in the next testing phases.

Can you give me the voltages/currents the transistors of each stage(input,driver,output) should see ?

Hi DannyHi Fab,

I finally continued working on the USSA-3, I'm now testing the input stage.

The manual states:

8.1.2 Adjust voltage in input stage

Connect V+ and V- and PGND (the one close to V-) to power supply (from 15Vdc to 30Vdc).

Adjust P2 for about TBD between TP8 and V-.

Adjust P1 for about TBD between TP7 and V+.

What's the voltage drop (TBD) I should aim for

over the resistors between TP7, TP8 and power supply voltage

or over the input transistors ?

I have a 24vdc PS.

I have the manual "USSA-33 AMPLIFIER BOARD Fab rev06p"

I just see that the manual also states "TBD" in the next testing phases.

Can you give me the voltages/currents the transistors of each stage(input,driver,output) should see ?

You have the partial manual. I sent you earlier today the full version. You should find your answers there and if not do not hesitate to chime in here.

good luck

fab

Thanks Fab!

Manual received and continued with setting the driver stage.

For my build I would move the output transistors a little further from the PCB, this for better heat distribution.

Will this give a problem, since the gate resistor will be at 5cm ?

Or should I move the gate resistor and the zener closer to the output transistor?

Manual received and continued with setting the driver stage.

For my build I would move the output transistors a little further from the PCB, this for better heat distribution.

Will this give a problem, since the gate resistor will be at 5cm ?

Or should I move the gate resistor and the zener closer to the output transistor?

Just move the gate resistor and Zener to the pins of the transistors and you're good. I did the same, see here: https://www.diyaudio.com/community/threads/ussa-5-build-with-review.323778/post-6451152

Hi Danny

yes, Mbrennwa implementation is quite a nice integrated one👍

In its case for the USSA-5 - with longer wires than 5 cm - I remember that there was no sign of oscillation (with gate resistors and zener on mosfet pins). However, the USSA-5 has a zobel at the output where the USSA-3 had none since not found necessary. But since you plan to have shorter wires and with resistors (and zener) installed on mosfet gate ( and close to transistor body) there should be no issue.

Normally the position of output transistors on a 300mm length heatsink is adequate for proper heat distribution so I suppose you have a different heatsink length or you want to get perfect optimization…

I note that you have long leads for the thermistors which is not necessary and is not best practice. They only need to take heatsink temperature and not instantaneous ones of the mosfet. Half actual lead length was used successfull.

I also note that the pot P1/P2 are installed reversed (screw) so turning right will decrease the output bias current instead of increasing. Just be aware of it while doing the adjustment.

The drivers body is isolated so no need for insulation between them and heatsink.

For input stage can you tell your jfet IDSS current you have used.

fab

yes, Mbrennwa implementation is quite a nice integrated one👍

In its case for the USSA-5 - with longer wires than 5 cm - I remember that there was no sign of oscillation (with gate resistors and zener on mosfet pins). However, the USSA-5 has a zobel at the output where the USSA-3 had none since not found necessary. But since you plan to have shorter wires and with resistors (and zener) installed on mosfet gate ( and close to transistor body) there should be no issue.

Normally the position of output transistors on a 300mm length heatsink is adequate for proper heat distribution so I suppose you have a different heatsink length or you want to get perfect optimization…

I note that you have long leads for the thermistors which is not necessary and is not best practice. They only need to take heatsink temperature and not instantaneous ones of the mosfet. Half actual lead length was used successfull.

I also note that the pot P1/P2 are installed reversed (screw) so turning right will decrease the output bias current instead of increasing. Just be aware of it while doing the adjustment.

The drivers body is isolated so no need for insulation between them and heatsink.

For input stage can you tell your jfet IDSS current you have used.

fab

Last edited:

Yes, it's a 400mm length heatsink, so the transistors are a little further.

OK, some work for my desoldering pump 🙂

I'll put the gate resistors and the zeners close to the transistors and I will shorten the leads of the thermistors.

I even didn't notice that the pots are reversed installed, they can stay like this 🙂

For a 2.5v drop over the 2sk170 resistor/thermistor/pot I measured 650ohm, that's 3.85ma

For the 2sj74 I measured 680ohm, that's 3.68ma

OK, some work for my desoldering pump 🙂

I'll put the gate resistors and the zeners close to the transistors and I will shorten the leads of the thermistors.

I even didn't notice that the pots are reversed installed, they can stay like this 🙂

For a 2.5v drop over the 2sk170 resistor/thermistor/pot I measured 650ohm, that's 3.85ma

For the 2sj74 I measured 680ohm, that's 3.68ma

Hi Danny

you have measured ID and IDSS is measured with source resistor as 0 ohms. Your extrapolated IDSS is on the lowish side so it is fine to get slightly higher damping. Keep on the good work so far!

Fab

you have measured ID and IDSS is measured with source resistor as 0 ohms. Your extrapolated IDSS is on the lowish side so it is fine to get slightly higher damping. Keep on the good work so far!

Fab

- Home

- Amplifiers

- Solid State

- USSA-5 Build with Review