It is quite clear what your board is supposed to do. The only puzzling thing is why do you have pins 2 and 4 connected on TDA1541? That is not needed in any of the 3 TDA1541 modes. But it probably does not hurt either.

Regarding isolators if you want to isolate the FIFO you should have isolator on FIFO output as well. Don't know if either isolator is really needed.

Regarding isolators if you want to isolate the FIFO you should have isolator on FIFO output as well. Don't know if either isolator is really needed.

Hi bohrok. Maybe I am wrong but for non A version, pins 2 and 4 must be tied together (https://www.audialonline.com/community/topic/non-a-tda1541/)

The OIR board provides isolation and reclocking at the output so it is already isolated. But as OIR board will be powered with the same regulator as the clean side of the FIFO I need to power the other isolator with a different sec/reg psu, at least the side touching the TDA.

First approach was the dc-dc but, as Mark correctly pointed out, they seem to be quite noisy so I am thinking about another solution. Been reading about SN6501 + PushPull transformer but not sure it is a good choice....

The OIR board provides isolation and reclocking at the output so it is already isolated. But as OIR board will be powered with the same regulator as the clean side of the FIFO I need to power the other isolator with a different sec/reg psu, at least the side touching the TDA.

First approach was the dc-dc but, as Mark correctly pointed out, they seem to be quite noisy so I am thinking about another solution. Been reading about SN6501 + PushPull transformer but not sure it is a good choice....

jmmbarco,

Could you please post a schematic of the red adapter board? I think with that I will understand the rest of your existing diagram correctly.

Could you please post a schematic of the red adapter board? I think with that I will understand the rest of your existing diagram correctly.

Sorry, I did not realize you were using non-A chip. Actually in non-A pin 4 is the system clock but you can tie it to BCK (pin 2).Maybe I am wrong but for non A version, pins 2 and 4 must be tied together

So we have a couple of views:

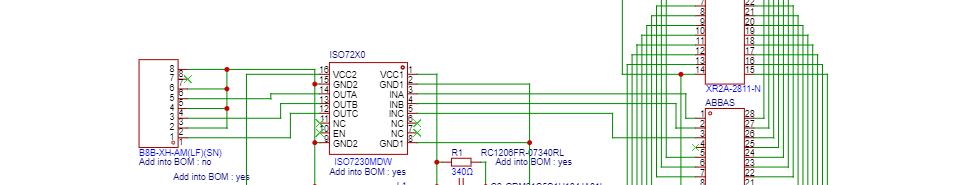

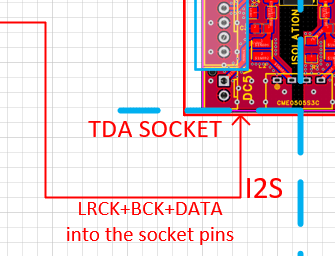

In the top pic above it looks like the connector on the left is an output. However, the lower pic shows some red color I2S signals feeding into an input. Where is that input in the schematic?

In the top pic above it looks like the connector on the left is an output. However, the lower pic shows some red color I2S signals feeding into an input. Where is that input in the schematic?

The schematic does not contain any details of the original PCB (ABBAS). Those I2S signals come from ABBAS board's SPDIF + CS8414 to ABBAS board pins 1-3. So on original PCB with TDA1541 populated those signals would go to TDA1541 pins 1-3.

True! In original PCB, I2S signals (red arrow in diagram) would enter into TDA1541 when IC was populated. When the breakout board is installed, those I2S signals are routed to the XH connector through the isolator)

Mark, so the XH is an output connector and the U.FL are the inputs.

I am been reading the datasheet of high speed optocouplers (50Mbps) and they only need to be powered in one side. What do you think?? Are they good for this purpose. I think Andrea is using them but not sure....

Mark, so the XH is an output connector and the U.FL are the inputs.

I am been reading the datasheet of high speed optocouplers (50Mbps) and they only need to be powered in one side. What do you think?? Are they good for this purpose. I think Andrea is using them but not sure....

Andrea does use TLP2767 or equivalent. However, they require power to light up the LED on the input side, and power for the electronics on the output side.

The power on the output side would be provided by the dedicated psu that previously fed the DC-DC isolated so no problem here. On the input side the I2S signal would power the led right?

I have downloaded the application datasheet where explains how to calculate Ri and Rl

I have downloaded the application datasheet where explains how to calculate Ri and Rl

So long as whatever device is driving the LED can supply enough current. The datasheet specifies 5.5mA-10mA. Some logic devices can sink more current than they can source. If you need to sink then the logic would be inverted, so you would need an inverter somewhere.On the input side the I2S signal would power the led right?

Hi, I'm writing you here cause my account is new and I can't send private messeges.Some delicate soldering 😉 just to get me up and running quickly rather than using the supplied connector, will use a more robust setup later before I

move it to a case. Great to hear another pleased customer discovering the fruits of Andreas work 👍 👍

Would you be able to help me with replacing my AMANERO 384 board with I2SoverUSB for the DAC BIG 7.

I read that you have expirience with it and you did it in the past.

Would you be able to send me a private messege and help me with this? Thanks a lot in advance.

Regarding radiated noise coupling, steel is your friend more than is aluminum. However its best to leave a air gap (maybe at least 2") between a steel shielding chassis and sensitive circuitry.

Exactly what negatives happen?There may be some magnetic coupling We don't want stray magnetic coupling between the steel and the circuitry being shielded.

Last edited:

The d-flip flop stage, after optoisolators (like in dac lite of fifo q7 ii) doesn't re-shape the data and bck following the new clock?Fifo is not reconstructing, but removing jitter. Only timing is reconstructed, not data. So still not sure what you mean ?

Still remarkable you hear all those differences

By giving a new and better square shape we can say the data is reconstructed.

Wouldn't the coupled noise removed thanks to the clean psu, at the optoisolator and/or d-flip flop outputs?

More distortion. Possible loss of HF.Exactly what negatives happen?

@Markw4

Exactly, metal shields due to cavity resonance and parasitic capacitance, attenuates HF, so increase slew rate, deforming the square wave.

Question is, does it matter if we put these shield only on the first dirty stage of a fifo buffer?

Where there are biggest emi offender.

Later in any case the data and bck being optoisolated and reclocked.

As I asked above

Will these square wave being re-shaped or the HF lost are lost (in other words the previous deformed square wave can not recovered)

I guess the second..

Exactly, metal shields due to cavity resonance and parasitic capacitance, attenuates HF, so increase slew rate, deforming the square wave.

Question is, does it matter if we put these shield only on the first dirty stage of a fifo buffer?

Where there are biggest emi offender.

Later in any case the data and bck being optoisolated and reclocked.

As I asked above

Will these square wave being re-shaped or the HF lost are lost (in other words the previous deformed square wave can not recovered)

I guess the second..

Last edited:

- Home

- Source & Line

- Digital Line Level

- The Well synchronized asynchronous FIFO buffer - Slaved I2S reclocker