Is there something about TL431 voltage generators that you do not like? They seem to be quite temperature stable, but I have heard of oscillation problems under certain conditions.

There is some discussion about oscillation here

Sony VFET Amplifier Part 2

post 3658 and following

Not sure if that is what you were looking for

Sony VFET Amplifier Part 2

post 3658 and following

Not sure if that is what you were looking for

I had some trouble with them in my diy sony Vfet.. if I remember well, the tighter spec'ed version is more sensitive to oscillation... Sony VFET Amplifier Part 2

The TL431 isn't bad, though it doesn't have the lowest noise. (I'm used to looking at voltage references for medical Ultrasound.) It is certainly convenient for a low parts count adjustable zener equivalent, and probably sufficient for audio.

My experience with the F6 suggests that a reference with a small negative tempco might be preferable to one with a near-zero tempco. The big SIT and P-type Mosfet will both conduct more current as they get hotter, and I intend to use reasonable size heatsinks instead of forced air cooling. Letting the hockey pucks conduct a little more current during initial warm up would help reduce the time needed to reach thermal equilibrium.

I've been looking at the datasheets for a few alternate references, and found some interesting application notes in TI's data for the LM385. Figure 17 in the attached document shows a simple circuit for a precision reference. Replacing the LM329 in that figure with a string of three or four green LEDs would make it possible to have an adjustable reference with negative temperature compensation. Figure 19 is also interesting in that the P-channel JFet could do a similar thing.

My experience with the F6 suggests that a reference with a small negative tempco might be preferable to one with a near-zero tempco. The big SIT and P-type Mosfet will both conduct more current as they get hotter, and I intend to use reasonable size heatsinks instead of forced air cooling. Letting the hockey pucks conduct a little more current during initial warm up would help reduce the time needed to reach thermal equilibrium.

I've been looking at the datasheets for a few alternate references, and found some interesting application notes in TI's data for the LM385. Figure 17 in the attached document shows a simple circuit for a precision reference. Replacing the LM329 in that figure with a string of three or four green LEDs would make it possible to have an adjustable reference with negative temperature compensation. Figure 19 is also interesting in that the P-channel JFet could do a similar thing.

Attachments

My guess is that the main issue with bias current and tempco would be with the optocoupler LEDs. The TL431 is controlling the (idle) Vds of the SIT, where is little bit of drift isn't a big deal.

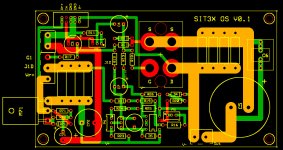

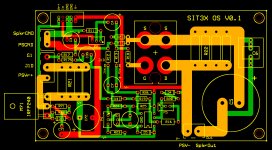

Here is a first cut at a PCB layout for the OS board, including the cap multiplier.

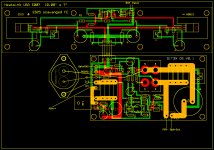

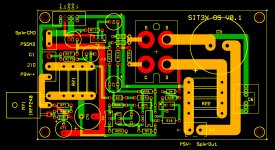

The second image shows how I intend to place the OS, FE, SIT, and PFET on the heatsink. The FE board is a "scavenged" version of the FE that I used in my ZD25 approximation of a XA25. The layout shown hasn't received much polish.

The OS board could probably be cleaned up by making it narrower and taller.

The second image shows how I intend to place the OS, FE, SIT, and PFET on the heatsink. The FE board is a "scavenged" version of the FE that I used in my ZD25 approximation of a XA25. The layout shown hasn't received much polish.

The OS board could probably be cleaned up by making it narrower and taller.

Attachments

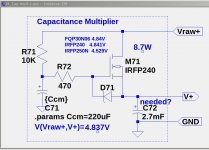

It might be convenient to have some voltage adjustment at the output of the cap multiplier. That would allow different Vds settings for the SIT, independently of the Vgs bias.

Funny that you mention that. Here is a variable voltage cap multiplier circuit I tried, with the intent to eliminate the output OS output caps, and the input cap for J1. The cap multiplier was good, but the V(Out) will be V(FEOut)+ Vgs(J1). In order to make this work would probably require an output offset servo controlling the output offset of the FE, which introduces more complexity and potential problems.

Attachments

Probably best to leave the final output coupling cap in place then. The intent is to allow a little more variation in the SIT parameters to get some harmonic cancellation with a greater range of devices.

Those output caps eat up a lot of real estate on the PCBs. That's ok.

I have been playing with the Shade circuit with an IXYS NFET in place of the 2SK182ES. It only requires adding 1 resistor and 1 cap to the PCB, and reversing 1 zener. I ran simulations and only a couple of minor parameter changes were required to get good results.

I have been playing with the Shade circuit with an IXYS NFET in place of the 2SK182ES. It only requires adding 1 resistor and 1 cap to the PCB, and reversing 1 zener. I ran simulations and only a couple of minor parameter changes were required to get good results.

More refinements to PCB layout, including a Schade feedback option, with components R17S and C3S. The TL431 now has a capacitor across it and a polyester capacitor has been added across the output cap.

Attachments

Last edited:

It looks bad. In a major PCB edit I totally screwed the connections of M1d, V-, and S. The stuff on the right side of the PCB must be redone. She looked so pretty, and then I discovered what she really was. 😱

Haha. Yes, more better. That sort of thing happens sometimes. I wasn’t looking closely at the right side of the board.

What is the max diameter of C5? Looks like snap-in leads, 10mm spacing?

What is the max diameter of C5? Looks like snap-in leads, 10mm spacing?

C5 has D=35mm D, LS=10mm.

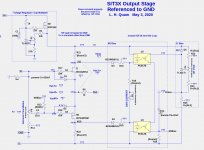

There are some issues about polarities of the input and output electrolytic caps. Originally the polarities were based on the drain of the SIT being at ground, but with

V+/V- power supplies, the nominal DC voltages across them are close to zero. With the loss of V+ headroom because of the capacitor multiplier, the source node should probably be biased negative to maintain equal positive and negative headroom. In which case, all of those cap polarities shown in my schematics and PCB layouts need to be reversed.

There are some issues about polarities of the input and output electrolytic caps. Originally the polarities were based on the drain of the SIT being at ground, but with

V+/V- power supplies, the nominal DC voltages across them are close to zero. With the loss of V+ headroom because of the capacitor multiplier, the source node should probably be biased negative to maintain equal positive and negative headroom. In which case, all of those cap polarities shown in my schematics and PCB layouts need to be reversed.

Capacitance Multiplier

View attachment Cap Multiplier JM.pdf

Here is a Capacitance Multiplier published in Electronics World, June 2001 by Jeff Macaulay.

Output Voltage is variable. Needs 2.50 Volts headroom. I have used this with 10,000uF cap on the output. So I presume even 22,000uF should not be an issue. Power transistor needs to be heatsink mounted.

Perhaps, it can be spruced up with Short Circuit Protection and a Diode for safe discharge. I use between 6k8 and 10k 2 Watt resistor for discharge for capacitors.

View attachment Cap Multiplier JM.pdf

Here is a Capacitance Multiplier published in Electronics World, June 2001 by Jeff Macaulay.

Output Voltage is variable. Needs 2.50 Volts headroom. I have used this with 10,000uF cap on the output. So I presume even 22,000uF should not be an issue. Power transistor needs to be heatsink mounted.

Perhaps, it can be spruced up with Short Circuit Protection and a Diode for safe discharge. I use between 6k8 and 10k 2 Watt resistor for discharge for capacitors.

- Home

- Amplifiers

- Pass Labs

- The SIT-3X Amplifier