it is a very easy job to perform to not cut any trace from the PCB,in case you are reselling it to remain intact

you have to use Q2 and Q8 instead of Q1 and Q7 from schematic

just bend up the 4 pins so you have the 4 empty holes in socket and then with a small wire soldered to Q2 go inside Q1 socket hole (because only Q1 does have a connection on the PCB) - do the same with the other Q8 and Q7.

this is the simpliest way to experiment real NOS and not destroy anything on the PCB.

in this way everything is reversible to original state.

in case you like NOS then you can solder the connections permanently and/or also cut original traces to Q1 and Q7.

Happy moding!

you have to use Q2 and Q8 instead of Q1 and Q7 from schematic

just bend up the 4 pins so you have the 4 empty holes in socket and then with a small wire soldered to Q2 go inside Q1 socket hole (because only Q1 does have a connection on the PCB) - do the same with the other Q8 and Q7.

this is the simpliest way to experiment real NOS and not destroy anything on the PCB.

in this way everything is reversible to original state.

in case you like NOS then you can solder the connections permanently and/or also cut original traces to Q1 and Q7.

Happy moding!

luxury54 said:it is a very easy job to perform to not cut any trace from the PCB,in case you are reselling it to remain intact

you have to use Q2 and Q8 instead of Q1 and Q7 from schematic

just bend up the 4 pins so you have the 4 empty holes in socket and then with a small wire soldered to Q2 go inside Q1 socket hole (because only Q1 does have a connection on the PCB) - do the same with the other Q8 and Q7.

Happy moding!

Hi,

I have got it done. The schematics has multiple typo errors which I have highlighted to the seller.

The Q7 is actually Q8 and Q18 is pin 13. The schematic is correct on pin 13.

I remove 74HC4040 and bend the pin 9. Then connect pin 7 to pin 9 to get Q2 (2.82MHz) to the TDA1541. Now I am in NOS mood. The immediate difference between NOS and the 2x OS is that NOS more liquid smooth or so call analogue. Not so fatigue. 2x OS is more details, more harsh. Guess this 2x OS would be good for speakers which are less sensitive. Overall NOS is the way to go.

next I will be getting some 330, 1k2 and 47 resistor and resistors for the DEM reclocking.

After this, what else am I left to mod ?

After longer listening you can get more fatigued with non-os. I miss depth in soundstage with nonos dacs, pcm56 and 1541. To interpolate small signals you need a high order analog filter after the dac, or simply os. I prefer OS.

When reclocking is done right, proper I/V, good decoupling, separate shunt ps for SAA7220 the sound is allmost non-os, but still very relaxed & detailed. Matter of taste.

I will try a 8X PMD100 digital filter in my CD880 in time.

When reclocking is done right, proper I/V, good decoupling, separate shunt ps for SAA7220 the sound is allmost non-os, but still very relaxed & detailed. Matter of taste.

I will try a 8X PMD100 digital filter in my CD880 in time.

HI Tubee,

I think you are right on the NOS sound character. I to have listened and found immediate liking for the warm and lush mid which is very good for listening. Upon further listening, I found NOS TDA1541a lacks dynamics and details. Bass sounds soft and less attack.

I feel the NOS basically dont reconstruct the wave correctly leaving some details in between the samples. I may be wrong, and to get that missing info/smoothing, a higher order filter will be required, perhaps 4 to 6 order.

For the moment, I am still listening to the 16bit 8times OS while getting the necessary components to do a DEM reclocking to 352kHz.

I think you are right on the NOS sound character. I to have listened and found immediate liking for the warm and lush mid which is very good for listening. Upon further listening, I found NOS TDA1541a lacks dynamics and details. Bass sounds soft and less attack.

I feel the NOS basically dont reconstruct the wave correctly leaving some details in between the samples. I may be wrong, and to get that missing info/smoothing, a higher order filter will be required, perhaps 4 to 6 order.

For the moment, I am still listening to the 16bit 8times OS while getting the necessary components to do a DEM reclocking to 352kHz.

I wonder what would be the connection if I were to use 4X oversampling. There is some advantage of 4x OS which I would like to try.

Since the SAA7220 can run in 4x, I chose to remain and try the DEM Reclocking. So here I set it up and run using pin 3 of 74HCT4040 to the 74HCT04. The 1nF cap I chose RIFA 1nF/100V and the resistor is using 1% as per photo below.

luxury54 said:follow the way it divides the clock with the 11.2896 mhz:

Q1 - 5,64 MHZ

Q2 - 2,82 MHZ (BCK)

Q3 - 1,4 MHZ

Q4 - 0.7 MHZ

Q5 - 350 KHZ (for DEM reclock)

Q6 - 175 KHZ

07 - 87.5 KHZ

Q8 - 44 KHZ (FS)

the 4040 starts with Q0 and not Q1 in the schematic. So Q0=5.6 and Q1=2.8. Which would make sense as a 8414 uses 32 bit frames for an audio sample: 44.1kHz*32*2=2.8Mhz. So no 2x.

It's not in the datasheet, but i don't think the 7220 accepts 2x input. And the general concensus is that the 1541 only accepts 8x in simultaneous mode and this is not (it's i2s)

Did you measure the frequencies?

[/B]

Just a warning: a 7220 failed on me once when repairing a cd80, when i had the pcb upside down. Could be coinsidence, but those 7220 do get hot. Luckily there are plenty around

Success with Philips CD-60

I just installed Tubee's version of DEM into a CD-60. Definite improvement: image seems to become "smaller" or more "distant", but it has actually gotten more focused and tighter. SQ generally more natural, with less glare.

What's strange is that w/the default 470pF cap removed (i.e., pin 16/17 open), the SQ barely changes (in my CD650 -- which incidentally has a TDA1541A-S2 Double Crown -- the sound w/the same cap removed distorts quite heavily). I haven't tried other cap values nor other DEM version.

All in all, a very worthwhile and inexpensive upgrade.

I just installed Tubee's version of DEM into a CD-60. Definite improvement: image seems to become "smaller" or more "distant", but it has actually gotten more focused and tighter. SQ generally more natural, with less glare.

What's strange is that w/the default 470pF cap removed (i.e., pin 16/17 open), the SQ barely changes (in my CD650 -- which incidentally has a TDA1541A-S2 Double Crown -- the sound w/the same cap removed distorts quite heavily). I haven't tried other cap values nor other DEM version.

All in all, a very worthwhile and inexpensive upgrade.

Check ecdesigns non os 1541 dac project for a clue

Nice to hear you have an improvement hollowman

Nice to hear you have an improvement hollowman

Re: Success with Philips CD-60

As a followup, I replaced Tubee DEM with Henk DEM (w/o WS or BCK reclocking, of course); the former was clearly better, Henk's was simply "different" from the orig cap.

My main point is that while I feel Henk was truly onto something with DEM of pin 16/17, WS and/or BCK reclocking should, by themselves (and specifically with 7220), yield improvement.

Comments are appreciated!

Just wanted to clarify that the Tubee DEM I implemented does not involve re-clocking WS or BCK as per Henk's original DEM ckt. On this issue (i.e., DEM of pin 16/17 only), I'm confused about the efficacy of Henk's WS+DEM design: why not DEM in and of itself?hollowman said:I just installed Tubee's version of DEM into a CD-60. Definite improvement....

As a followup, I replaced Tubee DEM with Henk DEM (w/o WS or BCK reclocking, of course); the former was clearly better, Henk's was simply "different" from the orig cap.

My main point is that while I feel Henk was truly onto something with DEM of pin 16/17, WS and/or BCK reclocking should, by themselves (and specifically with 7220), yield improvement.

Comments are appreciated!

I'm confused about the efficacy of Henk's WS+DEM design: why not DEM in and of itself?

The integrated DEM clock oscillator is a free running oscillator with a frequency between 100 and 300 KHz. This creates a second clock source (together with the bit clock) so inter-modulation occurs. This inter-modulation varies as the DEM oscillator drifts / jitters.

When the TDA1541A receives data, the DEM oscillator frequency will vary with the data pattern (very high jitter), due to on-chip crosstalk.

The DEM clock drives an on-chip shift register that controls the active current dividers that are part of the Dynamic Element Matching circuit. If the DEM clock frequency varies dynamically, bit errors will increase due to incorrect time averaging.

DEM clock issues are best tested with -40 ... -70dB recordings (Sheffield A2TB test disk).

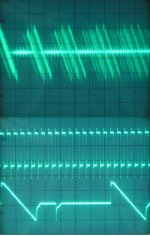

I attached some oscillograms that illustrate this problem. Upper picture shows how the DEM oscillator jitter (frequency modulation) when using the data sheet application. The picture on the bottom shows an externally triggered DEM clock.

One solution for this problem is preventing the DEM oscillator from oscillating:

pin 16 > 2K2 resistor > -15V

pin 17 > 2K2 resistor > -15V

Then injecting a DEM clock that runs fully synchronous with the bit clock (176.4 KHz, 352.8 KHz, 705.6 KHz, 1.4112 MHz or 2.8224 MHz.).

This is done by creating both a non-inverted and an inverted low jitter clock 352.8 KHz for example). Then injecting these two signals as follows:

non-inverting clock > 10K Ohm > pin 16

inverting clock > 10K Ohm > pin 17

DEM clock frequency also depends on active divider decoupling cap properties and placement. It's best to use smallest possible (SMD) film caps, and use shortest possible connections (every mm counts here). It's also possible to solder the active divider decoupling caps directly to the TDA1541A pins, and route the capacitor GND connections straight to pin 5 (analogue ground).

External DEM clock frequencies of up to 2.8224 MHz are possible when active divider decoupling is done correctly.

Now the DEM oscillator circuit is forced to run in sync with the external DEM clock, this eliminates inter-modulation, greatly reduces DEM clock jitter, and improves time averaging, resulting in lower bit errors.

The I2S signals are THE major source for on-chip interference (noise / inter-modulation with the audio signal).

Therefore it's absolutely necessary to attenuate the RF power levels of these signals to lowest possible values while maintaining reliable DAC chip operation.

The signal amplitude can be reduced from 5Vpp to only 400mVpp, but approx. 1.2V DC bias voltage is required. So the 400mVpp has to be super-imposed on this DC bias voltage. The signal of WS and DATA can also be band-limited for minimizing RF energy:

WS and DATA inputs are connected as follows:

input > 3K3 > +5V.

input > 1K > GND.

input > 3K3 > output from I2S source.

For the bit clock (BCK) we can't band limit as this might increase jitter, so different values are used here:

input > 330 > +5V.

input > 100R > GND.

input > 330 > output from I2S source.

It's also possible to use a dynamic jitter attenuator for BCK, this circuit attenuates BCK, and dynamically manipulates the exact moment the TDA1541A triggers. This way, sample jitter amplitude can be slightly reduced.

Attachments

I want to make 1541a NOS with reclock

I will build this design http://pc.watch.impress.co.jp/docs/2004/0428/nitda1541a_1fs_v11.jpg and will parallel another TDA1541a

there Is something I am not sure regarding reclocking

why schematic Is so simple done - only TCXO and 74HC0404 compared to the schematics on this thread - Henk, Ecdesigns, Toobee

would anybody explain

I will build this design http://pc.watch.impress.co.jp/docs/2004/0428/nitda1541a_1fs_v11.jpg and will parallel another TDA1541a

there Is something I am not sure regarding reclocking

why schematic Is so simple done - only TCXO and 74HC0404 compared to the schematics on this thread - Henk, Ecdesigns, Toobee

would anybody explain

why schematic Is so simple done - only TCXO and 74HC0404 compared to the schematics on this thread - Henk, Ecdesigns, Toobee

would anybody explain

The schematic shows CS8412 running in slave mode. When both source clock and clock module feeding CS8412 and TDA1541A aren't running exactly in sync, samples will be dropped or repeated.

Since both clocks run in different time domains, clocks aren't synchronized as required.

This will lead to repeated or dropped samples, resulting in audible clicks during playback. These are clearly audible when using a sine wave test signal.

Apart from sample timing jitter issues, the schematic has many flaws that will prevent optimal performance

so loooong a thread, but how about the TR with 74HC74?

I think the faster 74F74 should work better

I think the faster 74F74 should work better

Latest DEM reclock

Hello ecdesigns,

could you please post the latest (and supposedly best) DEM reclock circuit? In another thread I have read that you have obtained the best results using a clock derived from WS.

Regards.

Paul

Hello ecdesigns,

could you please post the latest (and supposedly best) DEM reclock circuit? In another thread I have read that you have obtained the best results using a clock derived from WS.

Regards.

Paul

would you please tell me how I can Improve that flaws

1) Don't use SPDIF when possible, it degrades sound quality. Try to use direct I2S whenever possible.

2) Use discrete voltage regulators for +5V, -5V, and -15V, LM78xx, LM79xx, LM317, LM337, and TL431-based regulators aren't suitable for this application and cause significant sound quality degradation. I could post some schematics of suitable regulators.

It's best to create high impedance in series with the power supply in order to block mains interference. Minimum requirement is a 9th order LC filter.

3) Slave the transport and put the master clock in the DAC. Use a synchronous reclocker (pico gate SMD part) for synchronously reclocking BCK with the master clock. This isn't always possible (depends on source properties). Best solution could be a concept similar to the SD-player project.

4) Use extreme low jitter master clock with highest possible PSRR and highest possible load immunity. Off the shelf clocks aren't suitable for these demanding applications. The master clock must be fed from a heavily filtered power supply (at least 9th order LC filter). The chokes used for power supply filtering must have lowest possible self capacitance, this means constructing special hybrid chokes.

5) Use I2S attenuators, this greatly reduces ground-bounce at the TDA1541A I2S input circuits. Use dynamic jitter attenuator circuit for BCK. I could post latest version of these circuits.

6) Don't ever use Op-amps in the signal path, these greatly reduce dynamic resolution. Placing two of these dynamic resolution killers in series is pretty fatal for audiophile sound quality. Major reasons for this are many on-chip components in the signal path, global feedback, high open-loop gain, and the use of both current sources and current mirrors. Best solution (for obtaining highest possible dynamic resolution) is using pure passive I/V converter without any semiconductors nor tubes. TDA1541A is capable of producing up to 550mVpp low distortion signal across a 140 Ohm passive I/V resistor, provided a 2.5mA bias current is used. This bias current can be injected using a resistor, or a resistor in series with a suitable hybrid choke. If amplification is required, tubes are the next best solution, followed by FETs.

The passive I/V resistor must provide extreme low noise levels (high-wattage wire-wound type), must be non-inductive and must have lowest possible self capacitance. I now use home made non-inductive wire-wound resistors that are wound using honeycomb winding method for providing extreme low self capacitance and lowest possible Eddy current losses.

7) When using NOS, don't use any form of filtering as this introduces uncorrectable phase shifts. This however requires large bandwidth processing (>80 KHz) up to the speakers. If a NOS DAC produces edge on vocals, this is likely to be caused by timing jitter and poor dynamic resolution of connected audio equipment, speakers included.

8) Use a suitable low jitter external DEM clock instead of the on-chip DEM oscillator that produces very high jitter. The DEM clock signal inter-modulates with BCK, this causes sample timing jitter increase. The latest circuit I have used is a simple diode-resistor injector that is fed with 44.1 KHz WS signal.

9) Pay extra attention to GND routes, use very low impedance wiring (litz wire) and a star ground.

10) Use smallest possible 100nF bypass film caps (SMD) and place these underneath the TDA1541A chip for shortest possible connections, every millimeter counts!

11) Never share decoupling cap (14 x 100nF) ground routes with other signals.

Last edited:

thx John for that tips

since I try to learn about reclocking I would be thankful to point me to some reclocking schematic - some simple and effective

as I see there Is two reclock types used - 1 reclocking I2S - BCK, WS, data;

2 DEM reclocking TDA1541 pin 16 and 17

In order of priority what signals are best to reclock - can all this be done with one XO supplied with good voltage regulator and given 2 or 3 pcs logic chips

can you confirm that this circuit http://www.diyaudio.com/forums/digital-line-level/11949-tda1541-dem-reclocking-12.html#post1723864 will work

since I try to learn about reclocking I would be thankful to point me to some reclocking schematic - some simple and effective

as I see there Is two reclock types used - 1 reclocking I2S - BCK, WS, data;

2 DEM reclocking TDA1541 pin 16 and 17

In order of priority what signals are best to reclock - can all this be done with one XO supplied with good voltage regulator and given 2 or 3 pcs logic chips

can you confirm that this circuit http://www.diyaudio.com/forums/digital-line-level/11949-tda1541-dem-reclocking-12.html#post1723864 will work

- Home

- Source & Line

- Digital Line Level

- TDA1541 DEM reclocking