Both the DF1704 and the PCM1798 will connect to the CXD2500 using the Standard format 16bit setting.

Thanks

just to sum up

You can say that Sony CXD2500 EIAJ format is almost the same as Burr-Brown standard 16bit format-> 2s compliments MSB first?

The dac will not notice the Zeroes between 16bit and 48 or 64bit from the CXD2500?

Then is free to choose 64bit or 48bit from CXD2500?

Kim

just to sum up

You can say that Sony CXD2500 EIAJ format is almost the same as Burr-Brown standard 16bit format-> 2s compliments MSB first?

The dac will not notice the Zeroes between 16bit and 48 or 64bit from the CXD2500?

Then is free to choose 64bit or 48bit from CXD2500?

Kim

I2S for Audio Alchemy

Hi all,

I'm also have difficulty to connect CXD2545 or TDA7220 or whatever to Audio Alchemy DAC via I2S input. In attached file there is 5 pins I2S input, so how do I have to connect devices?

Valery.

Here: http://www.yasmina.ru/aai.jpg

Hi all,

I'm also have difficulty to connect CXD2545 or TDA7220 or whatever to Audio Alchemy DAC via I2S input. In attached file there is 5 pins I2S input, so how do I have to connect devices?

Valery.

Here: http://www.yasmina.ru/aai.jpg

kimschips said:Thanks

just to sum up

You can say that Sony CXD2500 EIAJ format is almost the same as Burr-Brown standard 16bit format-> 2s compliments MSB first?

The dac will not notice the Zeroes between 16bit and 48 or 64bit from the CXD2500?

Then is free to choose 64bit or 48bit from CXD2500?

Kim

So long as the data is LSB justified and there is at least one BCK cycle per bit it will work. When set to Standard fmt 16bit, the last 16bits before a transistion of LRCK will be converted.

You cannot use the 64Fs BCK output directly. It is LSB first.

Re: I2S for Audio Alchemy

If you mean the SAA7220, then the output is 4x oversampled,and you can't send that to the dac.

The CXD2545 requires a little logic to make its ouput compatible with the I2S format.

http://www.diyaudio.com/forums/showthread.php?s=&threadid=25177&perpage=10&pagenumber=1

Valery said:Hi all,

I'm also have difficulty to connect CXD2545 or TDA7220 or whatever to Audio Alchemy DAC via I2S input. In attached file there is 5 pins I2S input, so how do I have to connect devices?

Valery.

Here: http://www.yasmina.ru/aai.jpg

If you mean the SAA7220, then the output is 4x oversampled,and you can't send that to the dac.

The CXD2545 requires a little logic to make its ouput compatible with the I2S format.

http://www.diyaudio.com/forums/showthread.php?s=&threadid=25177&perpage=10&pagenumber=1

Hello😕

PS: in my servicemanual the 48bit output from CXD2500 is used

So the 48bit format from the CXD2500 is also LSB justified and fit perfect to a pcm1798 dac chip in the settings 16bit standard format??

Best regards

Kim

So long as the data is LSB justified and there is at least one BCK cycle per bit it will work. When set to Standard fmt 16bit, the last 16bits before a transistion of LRCK will be converted.

PS: in my servicemanual the 48bit output from CXD2500 is used

So the 48bit format from the CXD2500 is also LSB justified and fit perfect to a pcm1798 dac chip in the settings 16bit standard format??

Best regards

Kim

Hello

I will answer my own and others questens to clear this up, there are a lot off formats to get hold on

Look the link for all the formats😎,

1 format is what I am being talking about

http://www.diyaudio.com/forums/showthread.php?s=&threadid=41079&highlight=

Best regards

Thanks for all your time

Kim

I will answer my own and others questens to clear this up, there are a lot off formats to get hold on

Look the link for all the formats😎,

1 format is what I am being talking about

http://www.diyaudio.com/forums/showthread.php?s=&threadid=41079&highlight=

Best regards

Thanks for all your time

Kim

rfbrw said:

So long as the data is LSB justified and there is at least one BCK cycle per bit it will work. When set to Standard fmt 16bit, the last 16bits before a transistion of LRCK will be converted.

You cannot use the 64Fs BCK output directly. It is LSB first.

I have looked at the 4 format.

I am very confused now why:

Many says that the output format from the sony is (forget 64bit)

48Bit 2s complement MSB first->Leftjustified

or

48bit 2s complement MSB first->Right justified

or

48bit 2S complement MSB first-> LSB justified

If you must use PCM1798 your settings could be:

16bit Standard 2s complent MSB first Leftjustified??

16bit starndard 2s complement MSB first right justified??

Please let´s clear up the formats once and for all

Kim

rfbrw said:All that matters is what is in the datasheet and the datasheet says 2's comp MSB first. The LSB occupies the last bit cell position in the frame therefore it is LSB or Right justified.

Hello rfbrw

Sorry for all my questens I think I understand it now🙄

I overlooked page 16 and 17 in the datasheet for PCM1798 what settings connect to the CXD2500(48bit output):

16bit right justified also called LSB justified standard format, MSB first 2s complement

Yes it´s clear now😱

My next understanding😀

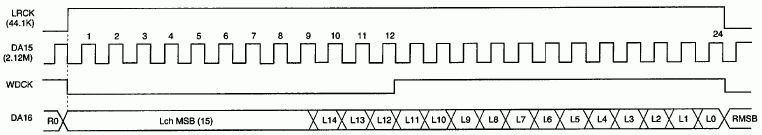

How can you see from the formats curves, that the differents between EIAJ and I2S. that LRCLK is delayed 7 BCLK cycles??

Best regards

Thanks for all

Kim

kimschips said:

My next understanding😀

How can you see from the formats curves, that the differents between EIAJ and I2S. that LRCLK is delayed 7 BCLK cycles??

Best regards

Thanks for all

Kim

It is the difference between where the MSB is and where you want it to be. In the case of the CXD2500, there is a transistion of LRCK and 8 BCK cycles later the MSB appears. In the case of I2S the MSB appears after 1 BCK cycle. Delay the transition for 7 cycles and the MSB appears 1 cycle later. Invert LRCK and you have conformed with the I2S standard.

Hello all.

It´s working rfbrw!!

My setup is CXD2500->PCM1798->Zapfilter2->XO2 clock (16.93Mhz).

Sound is great very clear with a lot off details and no harsch sound.

Just one questen:

What if I try with AD1955:

I can see it can handle 48Khz and 256FS so new clock

->12.288Mhz

Can it work in Hardwaremode like PCM1798??

I think it could be nice to compare som different dac chips like

PCM1798

AD1955

CS4398 Hardwaremode?

Best regards

Kim

It´s working rfbrw!!

My setup is CXD2500->PCM1798->Zapfilter2->XO2 clock (16.93Mhz).

Sound is great very clear with a lot off details and no harsch sound.

Just one questen:

What if I try with AD1955:

I can see it can handle 48Khz and 256FS so new clock

->12.288Mhz

Can it work in Hardwaremode like PCM1798??

I think it could be nice to compare som different dac chips like

PCM1798

AD1955

CS4398 Hardwaremode?

Best regards

Kim

Guys do you think that the higher price for PCM1794 is worth it against PCM1798?

Have you tried the CS4398?

What about AK4395 dac chip?

Kim

Have you tried the CS4398?

What about AK4395 dac chip?

Kim

Hello to all.

I read with interest all the post and would want to make a question. I have an old CDP with chipset Sony (in particulary DSP CX23035 - DAC CX20133).

Is it possible to connect the CX23035 's output at an other circuit with CS8412 and CS4329 chips.

Thanx in advance for replay.

Andrea

I read with interest all the post and would want to make a question. I have an old CDP with chipset Sony (in particulary DSP CX23035 - DAC CX20133).

Is it possible to connect the CX23035 's output at an other circuit with CS8412 and CS4329 chips.

Thanx in advance for replay.

Andrea

ingab said:Hello to all.

I read with interest all the post and would want to make a question. I have an old CDP with chipset Sony (in particulary DSP CX23035 - DAC CX20133).

Is it possible to connect the CX23035 's output at an other circuit with CS8412 and CS4329 chips.

Thanx in advance for replay.

Andrea

Does it also have a CX23034?

No, the only chips of CX..... serie are:

CX23035 (DSP);

CX20109 (RF amplifier);

CX20108 (SERVO SIGNAL PROCESSOR);

CX20133 (16 bit DAC).

Bye

😕

Andrea

CX23035 (DSP);

CX20109 (RF amplifier);

CX20108 (SERVO SIGNAL PROCESSOR);

CX20133 (16 bit DAC).

Bye

😕

Andrea

Without the datasheet for the CX23035, I can't say whether it has a digital output suitable for use with the CS8412 but you can probably add a SPDIF tx if it hasn't. Perhaps someone in the forum with a DCD1500 has an answer. The early version used the CX23035.

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Line Level

- Sony to Philips I2S Format Conversion