What do you think the operating point would be for most applications for 2SK2013/2SJ313 ?

Hi, Patrick!

First of all - thank you for your investigation at complementary pairs matching.

About OP of 2013/313 - we can start from datasheet SOA:

Using this devices at output stage with up to +-25 V supply rails we can choose biasing up to 0,5 A idle current. Id/Vgs curve have a good linearity from 0,1 A.

Based on predicted load current (placing attention on its resistance and current phase angle) we can estimate number of paralleled devices.

Based on paralleled devices quantity we can estimate total input capacitance and idle heat dissipation.

The next - taking attention to heatsink temperature at a given dissipation, let's stay below 65-70*C.

Suppose, that paralleling more than 4 devices is not a good idea. There must be a more attractive OPS devices from (input capacitance)/(allowable power).

> Current could be 50mA to 200mA for most amp

Then perhaps you would care to show the NNNNPPPP match over that region ?

Patrick

Then perhaps you would care to show the NNNNPPPP match over that region ?

Patrick

Sure, I will post some curves later. So I pass your exam? 😀 I am guessing you think my previous NNNNPPPP should match Vgs at lower current near 150mA instead of near 500mA? That can be done.

Anyway, for those who ordered from me, you may tell me which current you would operate your fets, I will try to give the most suitable sets🙂

Anyway, for those who ordered from me, you may tell me which current you would operate your fets, I will try to give the most suitable sets🙂

Hi Patrick,

You are a true expert on this and know much more than I do🙂 this is a test rather than question, lol? Anyway, the operation point depends what ppl build. Current could be 50mA to 200mA for most amp, I think. However, if you want to operate it at higher current of 500mA with heat sink, I don't see there is any issue on this.

> Current could be 50mA to 200mA for most amp

Then perhaps you would care to show the NNNNPPPP match over that region ?

Patrick

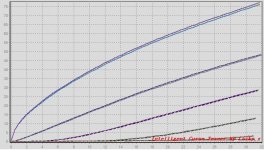

tyical matching sets at low current

An externally hosted image should be here but it was not working when we last tested it.

those who ordered matched octal 2SJ313/2SK2013, pls choose your sets from this link and PM me~~~

https://drive.google.com/file/d/0B7I-t5z7GgxRc05xYi1YQy1wckk/view?usp=sharing

https://drive.google.com/file/d/0B7I-t5z7GgxRc05xYi1YQy1wckk/view?usp=sharing

Hi

We exchanged some PM, several times I wet over the thread and still did not found the price of the unmatched (only would interested out of the box, never measured or selected otherwise better to get matched pairs at least P to P & N to N)

Would you please name the post where I found the price list. I only found 3 or 4Pc matched etc..

Greetings gabor

You can send me a PM.. if that is better

We exchanged some PM, several times I wet over the thread and still did not found the price of the unmatched (only would interested out of the box, never measured or selected otherwise better to get matched pairs at least P to P & N to N)

Would you please name the post where I found the price list. I only found 3 or 4Pc matched etc..

Greetings gabor

You can send me a PM.. if that is better

Hi Gabor,

Sorry for the confusion. Looks like I need to make my post clearer😀 will work on it when I have time.

You are referring to 1530/201, if I recall correctly ? Unmatched pair price is at the end of that item, "Unmatched: $15".

? Unmatched pair price is at the end of that item, "Unmatched: $15".

For out of the box FETs, I found PFETs you would have better chance to get good matching, but nFETs are not likely unless u are super lucky 😀 basically, nfets variations are terriable...

Thx~!

Sorry for the confusion. Looks like I need to make my post clearer😀 will work on it when I have time.

You are referring to 1530/201, if I recall correctly

? Unmatched pair price is at the end of that item, "Unmatched: $15".

? Unmatched pair price is at the end of that item, "Unmatched: $15". For out of the box FETs, I found PFETs you would have better chance to get good matching, but nFETs are not likely unless u are super lucky 😀 basically, nfets variations are terriable...

Thx~!

Hi

We exchanged some PM, several times I wet over the thread and still did not found the price of the unmatched (only would interested out of the box, never measured or selected otherwise better to get matched pairs at least P to P & N to N)

Would you please name the post where I found the price list. I only found 3 or 4Pc matched etc..

Greetings gabor

You can send me a PM.. if that is better

2SK117

2SJ75G and 2SJ75BL

well matched 2SJ74 in a metal can😱😀

refer to the first post for prices

An externally hosted image should be here but it was not working when we last tested it.

2SJ75G and 2SJ75BL

well matched 2SJ74 in a metal can😱😀

refer to the first post for prices

An externally hosted image should be here but it was not working when we last tested it.

An externally hosted image should be here but it was not working when we last tested it.

I have two 2SJ109BL to let go @ 55USD with free shipping. Grab it beore they are gone~!

An externally hosted image should be here but it was not working when we last tested it.

An externally hosted image should be here but it was not working when we last tested it.

An externally hosted image should be here but it was not working when we last tested it.

genuine 2sj74BL, waiting to be matched with K170

An externally hosted image should be here but it was not working when we last tested it.

IRFP240 and IRFP9240 1000 piences each to be matched

An externally hosted image should be here but it was not working when we last tested it.

holiday is over...will start to offer various amp kits, F5, F6, V etc, once IRFP fets matchings are done🙂

There are some wrong data sheet of 2sk79 circulating. For those who are interested in this fet, here is the corrected version.

Last two 2sj109GR to clear. 33$ for two.

2sj109BL all sold out. New stock of j109BL arrive in a few weeks time @ 25$ each. No more GR already.

2sj109BL all sold out. New stock of j109BL arrive in a few weeks time @ 25$ each. No more GR already.

Last edited:

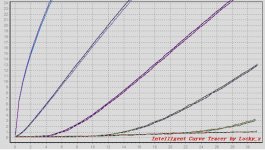

For a long time, I have been wondering whether NN matching or PP matching would be different at room temp and 65C, i.e. would the devices still be well matched at room temp if they were measured and grouped based on 65C measurement results? Finally got time to do a quick experiment on this today, when qualifying an order before shipping it out for a forumer.

It turns out FETs are still very well matched at room temp even they were originally matched using a hot plate at 65C, as shown below. Devices with the same polarity (NMOS or PMOS) have quite similar temperature behaviors. Therefore, it looks like matching temp does not really matter much in this case (at least for these two kinds of MOSFETs, esp when it comes to matching within the same type). Even matching is done at room temp, most likely these MOSFETs are also very matched at 65C. Looks like my efforts of matching those fets at 65C may not be that useful T.T...

For PMOS, Gm appears to be slightly degraded at 65C than room temp, while NMOS seems not that obvious.

Hope these data would be helpful to some of you who want to do matching at higher temp ^.^

Figures below are for four P type and four n type matched quad

It turns out FETs are still very well matched at room temp even they were originally matched using a hot plate at 65C, as shown below. Devices with the same polarity (NMOS or PMOS) have quite similar temperature behaviors. Therefore, it looks like matching temp does not really matter much in this case (at least for these two kinds of MOSFETs, esp when it comes to matching within the same type). Even matching is done at room temp, most likely these MOSFETs are also very matched at 65C. Looks like my efforts of matching those fets at 65C may not be that useful T.T...

For PMOS, Gm appears to be slightly degraded at 65C than room temp, while NMOS seems not that obvious.

Hope these data would be helpful to some of you who want to do matching at higher temp ^.^

Figures below are for four P type and four n type matched quad

An externally hosted image should be here but it was not working when we last tested it.

An externally hosted image should be here but it was not working when we last tested it.

Last edited:

Devices with the same polarity (NMOS or PMOS) have quite similar temperature behaviors. Therefore, it looks like matching temp does not really matter much in this case

Hi, Liubin!

Try to do this with BJTs like BC550/BC560, 2SC3503/2SA1381, 2SC4793/2SA1837 or MJL3281/MJL1302.

Hi pavel,

thx. will try on BJT when I have time😀

thx. will try on BJT when I have time😀

Hi, Liubin!

Try to do this with BJTs like BC550/BC560, 2SC3503/2SA1381, 2SC4793/2SA1837 or MJL3281/MJL1302.

- Home

- Vendor's Bazaar

- Selling Zhou Fang’s remaining stocks including some very rare Toshiba transistors