Bloody hell, 40 chips!

I hope they come at an affordable group price, LOL

I guess that when looking into such high numbers, you have definitely to consider the layout carefully as varying signal path induced by large distances can become a serious problem

Yep, the underside sounds like a good idea, thinking 3D gets crucious, I hope they don't suffer from heat or interferences with each other.

On the other hand I never thought about this, so I ma not the best person to give any hints... and I am not sure I want to give you some, as WHERE would you stop then GLOL!

Great adventures, keep us posted

Claude

I hope they come at an affordable group price, LOL

I guess that when looking into such high numbers, you have definitely to consider the layout carefully as varying signal path induced by large distances can become a serious problem

Yep, the underside sounds like a good idea, thinking 3D gets crucious, I hope they don't suffer from heat or interferences with each other.

On the other hand I never thought about this, so I ma not the best person to give any hints... and I am not sure I want to give you some, as WHERE would you stop then GLOL!

Great adventures, keep us posted

Claude

At such low supply voltage, heat is very far from being a problem. At lowest supply these chips are pulling less than 10mW each. So >100 per Watt. The classA analog circuits though are rather toasty, dealing with all that current.

In that case, if they are not radiating waves of some disturbing form (in which case a ground layer in between could also help), then with my limited knowledge I would see no reason to not try to stack them indeed both sides of a board...

piggiebacking

Hi Richard!

Years ago I had built a DDDac 1543 (Doede Douma).

This dac existed of numerous TDA1543 chips, packed together forming a tower with the use of cooling profiles to get rid of the heat.

As I understand: heat is no problem in your design, so piggiebacking five or ten chips should be no problem.

Though this way of building ,in an easy doable way, asks for a chip with legs.

I am not aware of availability of your dac chips in a legged form though!

But I am sure you know!

https://www.diyaudio.com/forums/attachment.php?attachmentid=989887&stc=1&d=1634070857

Hi Richard!

Years ago I had built a DDDac 1543 (Doede Douma).

This dac existed of numerous TDA1543 chips, packed together forming a tower with the use of cooling profiles to get rid of the heat.

As I understand: heat is no problem in your design, so piggiebacking five or ten chips should be no problem.

Though this way of building ,in an easy doable way, asks for a chip with legs.

I am not aware of availability of your dac chips in a legged form though!

But I am sure you know!

https://www.diyaudio.com/forums/attachment.php?attachmentid=989887&stc=1&d=1634070857

Attachments

Last edited:

I don't know how badly it can affect performance, but in that tower it seems to me that there are massive path length differences when considering the bottom and the top chips of the pile...

Though this way of building ,in an easy doable way, asks for a chip with legs.

I am not aware of availability of your dac chips in a legged form though!

But I am sure you know!

Hi Ed - thanks for the inspiration. I'm not aware of any TDA1387 in DIL packages either. The closest is TDA1545 which I've played with before and not had the best results. But might be worth another look with a bigger form-factor PCB than I'm currently using - I might still have some of those chips in my closet.

In the meantime, these 40 chips are sounding awesome 😀

So 40 is the way forward 🙂

Oh, hold on, unless... did you try... 100????

Because if not, you may well already consider your new board and layout accordingly for compatibility... just saying LOL

Have a nice day

Claude

Oh, hold on, unless... did you try... 100????

Because if not, you may well already consider your new board and layout accordingly for compatibility... just saying LOL

Have a nice day

Claude

More than 40 chips would need a more heavy-duty analog stage using SOT-223 transistors for output. Quite do-able but probably won't fit on the existing PCB. I will consider it an option for a 10*10cm PCB in the future. I plan to have a try running two 40-chip DACs in balanced mode (giving 80 chips effective) to see if there's any more juice to be squeezed from this particular lemon.

OK!

Somewhere ther should be diminishing returns, I am not sure than over 40 chips make really sense vs other bits that could possibly be implemented (read DSP to convert files down to 16bits and enbale digital volume control, better power regulation at the boards, better output stages ?)

Anyway, the end result sounds promising!

Thanks for all that

Claude

Somewhere ther should be diminishing returns, I am not sure than over 40 chips make really sense vs other bits that could possibly be implemented (read DSP to convert files down to 16bits and enbale digital volume control, better power regulation at the boards, better output stages ?)

Anyway, the end result sounds promising!

Thanks for all that

Claude

There has been diminishing returns all along. With just 1 chip, you only need to add one extra chip to cut the noise in half. With 20 chips, for the same improvement you need to add 20 more chips.

I'm thinking more in terms of understanding where the bottlenecks are. At present it seems the bottleneck is LF noise coming from the DAC chip. But at some point, another bottleneck takes over. Which makes me think of Goldratt's 'Theory of constraints'. Ever come across his books?

I'm thinking more in terms of understanding where the bottlenecks are. At present it seems the bottleneck is LF noise coming from the DAC chip. But at some point, another bottleneck takes over. Which makes me think of Goldratt's 'Theory of constraints'. Ever come across his books?

Books (the goal & Co), nope I didn't read them

His theory of constraints, yep

I agree on this for your project, by multiplying the DAC chip you will focus on addressing a given parameter that you find limiting, but at some points once this is good enough something else will arise that might (or not) set a limit to the performance you want to achieve.

The limit of this theory is the lack of overall view and redistibuting cards (by thinking mainly only subprocesses), the beauty is it is quick and quite efficient when dealing with quite mature processes suffering from (say quite obvious) limitations. Quite useless though, or misleading, when designing from scratch IMHO.

Hence me pointing in the direction 'once you have enough performance adding chips might not be the way forward', but in fact I wasn't exactly thinking constraints, more VFM regarding sound quality (eg even if the constraint LF distorsion is still there with 100 chips, it might be though be overall more profitable "all in all" to focus on something else... or even to redesign / rethink the product, as everything is a compromise).

You are doing already some of these, exploring different solutions through various DACs... to our pleasure!

A complete redesign could be at some stage the use of another DAC chip altogether, LOL! But AFAIC I found that DAC chip made less difference to the overall sound than what one might expect...

To be more practical, given your current concentration on LF here, how would you rate the sonic attributes you just achieved vs say a modern delta-sigma implementation with state of the art output stage in the LF department?

Fascinating, whatever you use to progress, I have no clue if that's the best methodology but at least you DO progress... and quickly!

Keep us posted, I will build one of these!

Claude

PS : to come back on the said theory, that's the (efficient) difference between a bottleneck and a constraint, one not being necessarly the other, it all depends on the need (performance need)

His theory of constraints, yep

I agree on this for your project, by multiplying the DAC chip you will focus on addressing a given parameter that you find limiting, but at some points once this is good enough something else will arise that might (or not) set a limit to the performance you want to achieve.

The limit of this theory is the lack of overall view and redistibuting cards (by thinking mainly only subprocesses), the beauty is it is quick and quite efficient when dealing with quite mature processes suffering from (say quite obvious) limitations. Quite useless though, or misleading, when designing from scratch IMHO.

Hence me pointing in the direction 'once you have enough performance adding chips might not be the way forward', but in fact I wasn't exactly thinking constraints, more VFM regarding sound quality (eg even if the constraint LF distorsion is still there with 100 chips, it might be though be overall more profitable "all in all" to focus on something else... or even to redesign / rethink the product, as everything is a compromise).

You are doing already some of these, exploring different solutions through various DACs... to our pleasure!

A complete redesign could be at some stage the use of another DAC chip altogether, LOL! But AFAIC I found that DAC chip made less difference to the overall sound than what one might expect...

To be more practical, given your current concentration on LF here, how would you rate the sonic attributes you just achieved vs say a modern delta-sigma implementation with state of the art output stage in the LF department?

Fascinating, whatever you use to progress, I have no clue if that's the best methodology but at least you DO progress... and quickly!

Keep us posted, I will build one of these!

Claude

PS : to come back on the said theory, that's the (efficient) difference between a bottleneck and a constraint, one not being necessarly the other, it all depends on the need (performance need)

Last edited:

I've not got a performance 'I want to achieve' in mind. Rather I'm curious to explore what kinds of performance are indeed possible. So I plan to add chips until I either get tired of soldering them or until a doubling doesn't give a noticeable improvement. That I would take to be the point of 'enough performance' but only in the direction of multiplying chips. In the case of 'no improvement' being obtained I would assume then that the bottleneck's been moved. The I/V stage has already been optimized as far as I can see as practically possible (down to the thermal noise of the resistors which could be the next bottleneck).

I have been thinking quite a bit about alternative chips and even started building a prototype using some communications DACs (with 20mA output current). But I've been distracted by the progress I've been making on Celibidache. At some point I'll have to go back to that prototype - at least it will act as a kind of reference or anchor point for SQ.

As for comparisons with S-D DACs, I don't have any reasonably advanced designs here to listen to, just one or two odd Taobao boards. But Archimago made some S-D DAC recordings and put them up on his site so it might be a way forward to listen to those for the sake of comparisons. I recall he had at least one AKM and a couple of ESS DACs, the drawback being only one recording of classical music

I have been thinking quite a bit about alternative chips and even started building a prototype using some communications DACs (with 20mA output current). But I've been distracted by the progress I've been making on Celibidache. At some point I'll have to go back to that prototype - at least it will act as a kind of reference or anchor point for SQ.

As for comparisons with S-D DACs, I don't have any reasonably advanced designs here to listen to, just one or two odd Taobao boards. But Archimago made some S-D DAC recordings and put them up on his site so it might be a way forward to listen to those for the sake of comparisons. I recall he had at least one AKM and a couple of ESS DACs, the drawback being only one recording of classical music

It all sounds very exciting and we are very mucky that you explore the limits for us!

To me enhencing your current designs until the point of no noticeable improvement sounds like a good plan. You then have a reference point and you can use it then with future developments around other architectures or chips. Very exciting!

Thanks for the hint re Archimago, I will try to listen to that!

Have a nice day

Claude

To me enhencing your current designs until the point of no noticeable improvement sounds like a good plan. You then have a reference point and you can use it then with future developments around other architectures or chips. Very exciting!

Thanks for the hint re Archimago, I will try to listen to that!

Have a nice day

Claude

Celibidache 9th order filter PCBs

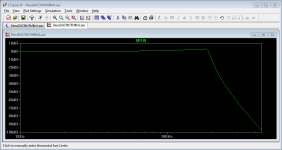

The dedicated Celibidache filter PCBs have arrived - frequency response plot attached. Since the NOS droop is compensated for in the passive filter now there's no need for an active filter stage giving the HF lift. Which saves power and board space. Stop-band rejection is close to -100dB by 44kHz.

The dedicated Celibidache filter PCBs have arrived - frequency response plot attached. Since the NOS droop is compensated for in the passive filter now there's no need for an active filter stage giving the HF lift. Which saves power and board space. Stop-band rejection is close to -100dB by 44kHz.

Attachments

Hi Richard,

Did you consider mounting the dac chips on small stackable daughter boards. It might allow easily comparing 10 to 20 to other chip multiple you care to play with.

Did you consider mounting the dac chips on small stackable daughter boards. It might allow easily comparing 10 to 20 to other chip multiple you care to play with.

"The whole problem... is that fools and fanatics are always so certain of themselves while wise people are full of doubts. - Bertrand Russell"

+1

The dedicated Celibidache filter PCBs have arrived - frequency response plot attached. Since the NOS droop is compensated for in the passive filter now there's no need for an active filter stage giving the HF lift. Which saves power and board space. Stop-band rejection is close to -100dB by 44kHz.

I hope you are making kits available.

Paul - I've given some consideration to ways of mounting chips on daughter boards. With the current layout though stacking is very limited due to the filter board over the top of the chips. Also with the design I have there are other parts of the circuit that need changing (biasing current sources) when the number of chips is changed. So its not quite a simple plug-and-play.

@commstech - filters won't be available in kit form due to the impracticality of providing selected value caps in multiple small bags. Shipping individual inductors is also labour-intensive on packaging.

@commstech - filters won't be available in kit form due to the impracticality of providing selected value caps in multiple small bags. Shipping individual inductors is also labour-intensive on packaging.

I've recently acquired one of @IVX's Cosmos ADCs and its a great tool for investigating the output of my DACs. Its shown that 2.7V is a bit too low a voltage for operating the DAC chips as the measured distortion creeps up a bit. So on the next revision of Celibidache I am going to run the chips at 3V. This means more heat in the I/V stage as a higher supply gives rise to more current to deal with - 40 chips gives 24mA total current swing.

To deal with the extra current I'm paralleling the OPS current sources and offloading some dissipation in the output darlington to a zener diode. We shall see how that pans out - if it turns out to degrade the SQ then the next step will be to switch to SOT-223 output transistors.

To deal with the extra current I'm paralleling the OPS current sources and offloading some dissipation in the output darlington to a zener diode. We shall see how that pans out - if it turns out to degrade the SQ then the next step will be to switch to SOT-223 output transistors.

- Home

- Source & Line

- Digital Line Level

- lingDAC - cost effective RBCD multibit DAC design