That would tell you the response from Vin to Vout, which can easily be changed by the choice of the resistor between Vin and the JFET gates. What about the stability of the feedback loop?

That would tell you the response from Vin to Vout, which can easily be changed by the choice of the resistor between Vin and the JFET gates. What about the stability of the feedback loop?

Yes you can check that also, but that is a small fish to fry.

At the moment I am referring to Genergs circuit, I suspect it won't have a safe gain margin. I have found just playing with resistance values at the gate of jfet is not always the best approach, it requires thoughtful use of resistance values through out the whole circuit including feedback loop.

My limited observations have been that increasing the resistance at the gate of the jfet improves phase margin but often does very little to improve gain margin. It often requires much more thought than just doing that.

Last edited:

Yep that's me.PicoBastard

Now I have your attention. I have limited time to confirm this right now.

There are 2 effective ways to bring stability to the closed loop circuit of this amp.

1) Increasing the resistances at the gate of the toshiba fets k2013/j313

2) Increasing the impedance of the feedback loop

3) Combination of both

In terms of maximising Slew while maintaining stability can you determine the sweet spot.

Is it best doing:

1) Minimising feedback loop impedance and increasing gate resistances at the mosfets

2) Minimising resistance at the gates of the mosfets and increasing the impedance of the feedback loop

3) Or is the sweet spot somewhere in the middle

My guess is probably option 2 is the best, but I have not personally done the comparison properly.

Even though ltspice is not accurate in measuring Slew (in my opinion) it is informative in terms of observing trends. All we need to see is an improving trend.

For all comparisons try and maintain Gain Margin of say 12dB or better but keep it the same.

Edit: If you're not interested in doing that, I'll look into that later. Just a bit busy right now.

Last edited:

There are so many parameters to play with that affect the impedance of the loop. Some that might not be obvious are:

- JFET Idss

- Amount of DC degeneration of the front-end MOSFET changing gate to rail voltage.

- Resistance between JFET drain and cascode emitter.

- Resistance between cascode base and cascode bias generator.

Yeah yeah. You don't need to try and prove anything here.

I said effective ways.

Most of those methods offer minimum change and don't make too much sense in playing around with too much.

Jfet Idss isn't changing much ie usually 8mA plus or minus 1mA.

We're not adding degeneration (well I'm not)

Blah blah etc

I wouldn't call 20dB of global feedback a small amount (I've personally chosen 15dB for myself though)

Lets call it 12dB of gain margin. Just to keep something fixed. The actual figure is not super important it just needs to be fixed to do the comparison.

If you're not interested in doing it that's ok.

It was just something I intended to check to confirm whether my guess is correct.

I said effective ways.

Most of those methods offer minimum change and don't make too much sense in playing around with too much.

Jfet Idss isn't changing much ie usually 8mA plus or minus 1mA.

We're not adding degeneration (well I'm not)

Blah blah etc

I wouldn't call 20dB of global feedback a small amount (I've personally chosen 15dB for myself though)

Lets call it 12dB of gain margin. Just to keep something fixed. The actual figure is not super important it just needs to be fixed to do the comparison.

If you're not interested in doing it that's ok.

It was just something I intended to check to confirm whether my guess is correct.

Last edited:

A resistor of 470R or more between the JFET drain and the cascode emitter has a significant affect on the phase margin, and lowers the loop bandwidth.

I have been targeting an open-loop gain (OLG) of about 44dB and global feedback of 12-14dB, leaving about 10-12dB for local feedback. I will run some simulations at higher levels of OLG.

I have been targeting an open-loop gain (OLG) of about 44dB and global feedback of 12-14dB, leaving about 10-12dB for local feedback. I will run some simulations at higher levels of OLG.

Hi 2picoclever,

when I take serious what you say about testing amp stability in Spice....

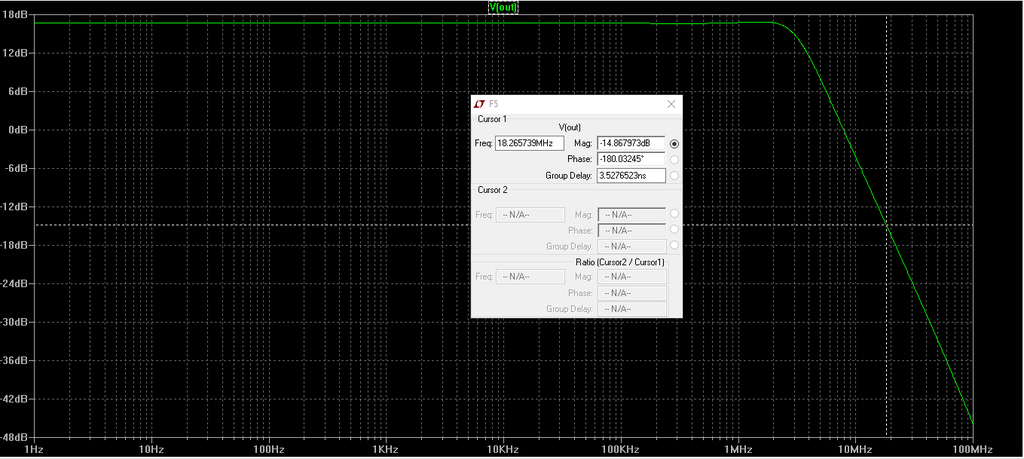

Most of my drafts are in danger to oscillate because the -db value at -180° is lower than 12dB at 1 V AC input.

Hm... can you show a beast circuit that is stable with your criteria?

Indeed the Aleph3 shows a -dB value at -180° phase that is near -24dB.

Interesting and confusing at same time..... I will check further known circuits from FW for this behavior.

Indeed

when I take serious what you say about testing amp stability in Spice....

Most of my drafts are in danger to oscillate because the -db value at -180° is lower than 12dB at 1 V AC input.

Hm... can you show a beast circuit that is stable with your criteria?

Indeed the Aleph3 shows a -dB value at -180° phase that is near -24dB.

Interesting and confusing at same time..... I will check further known circuits from FW for this behavior.

Indeed

and as Lynn says a higher value of the input gate stopper at the J-fets changes the situation.

As far as I can say to a better -dB value. So F7 with its 39k is very stable.....?

As far as I can say to a better -dB value. So F7 with its 39k is very stable.....?

Everything changes something. Perhaps that is why Nelson prefers simple circuits; fewer parameters to optimize. And indeed I have started to work again on an even simpler circuit, with far fewer parameters. I had abandoned it earlier because of FE bias stability problems which are now solved. I suspect that it is very similar to what picoDumbs is exploring.

A resistor of 470R or more between the JFET drain and the cascode emitter has a significant affect on the phase margin, and lowers the loop bandwidth.

I have been targeting an open-loop gain (OLG) of about 44dB and global feedback of 12-14dB, leaving about 10-12dB for local feedback. I will run some simulations at higher levels of OLG.

Yes but at 8mA current draw (almost 4V drop) through that region you can only take that idea so far and maintain say 12V to 13V Vds across the jfets. So I class that as less effective or limited in it's use.

Adding resistance to the gate of the mosfet you don't have that limitation of constantly dropping voltage.

Anyway this is not what interests me at all, I already know all of this.

What interests me is, out of the 3 options (the third option being a combination of the first 2 options) I proposed which combination gives best performance while maintaining stability.

Never mind, I will look into it myself. I won't ask for any more favors, I thought I was already asking a bit too much.

Looking forward to seeing the progress of your build.

Last edited:

Everything changes something. Perhaps that is why Nelson prefers simple circuits; fewer parameters to optimize. And indeed I have started to work again on an even simpler circuit, with far fewer parameters. I had abandoned it earlier because of FE bias stability problems which are now solved. I suspect that it is very similar to what picoDumbs is exploring.

Keep going Lynn, that is always my aim.

I don't like straining the brain, it keeps me up at night with endless questions.

I am very interested. I was going in a different direction, but have changed course with a design that might be similar to yours....

Never mind, obviously you are not interested. I will look into it myself. I won't ask for any more favors.

Looking forward to seeing the progress of your build.

and as Lynn says a higher value of the input gate stopper at the J-fets changes the situation.

It changes it but not always for the better especially if you are right on the edge of stability.

In my eScaped Goat, it required dropping the value to 100 Ohms at the gate of the Jfet not increasing it.

Drop the value to 100 Ohms at the jfet and watch the gain margin IMPROVE.

It's a bit of balancing act, you need to consider the amp as a whole.

Try it.

I'm not suggesting using 100 Ohms in your final version, I'm saying that just adding resistance there at the jfet without considering the other locations first can have unintended consequences.

Last edited:

It is interesting that the XA25 User Manual does not show plots of THD vs. Frequency or a plot of the residual distortion waveform. I am now getting THD figures close to those plots, but the H2 phase wanders all over the place. Maybe it is no longer important at such low distortion levels.

I am very interested. I was going in a different direction, but have changed course with a design that might be similar to yours.

Ok, that is great.

Simplify where ever possible.

Looking forward to seeing it.

My completed amp is a long way off, even though the circuit is completed, I need to finish building cases, I suspect it will be 2 weeks before the cases are complete, then maybe another 2 weeks to have power supply and amp circuit installed.

I need to stay focused now and not let the brain distract me too much. Hahaha

Last edited:

Yes I believe that is true.It is interesting that the XA25 User Manual does not show plots of THD vs. Frequency or a plot of the residual distortion waveform. I am now getting THD figures close to those plots, but the H2 phase wanders all over the place. Maybe it is no longer important at such low distortion levels.

You can either go for a strong negative phase harmonic at 0.01% distortion and higher, or go the other direction and just minimise it to virtually zero.

Because the rising rate of distortion with power is so low compared with common source amplifiers, I think it is less critical. The fun feature is zero degeneration.

It would still be fun to try different things though.

- Home

- Amplifiers

- Pass Labs

- F4 Beast Builders