Thank you for the information. That was exactly what I wanted to hear 🙂

I will probably try to get the signal from 74LVC157. Then the switching between DSD and PCM will be automatic.

--Per

I will probably try to get the signal from 74LVC157. Then the switching between DSD and PCM will be automatic.

--Per

In the Sabre dac app note, ESS recommends inverted MCLK when that's synchronous, although they only says

"The inverted MCLK ensures that the Sabre noise as low as possible." and there's no further explanations.

Anyone tried these?

As far as I tried myself, (I stolen MCLK from transport via LVDS and made inverted at the LVDS receiver input.)

I felt it's slightly better in SQ, but I can't say surely it's better because I haven't done strict A/B comparison yet.

Besides, I have no skill and equipments to measure noise performance correctly.

I 'm just curious what other people found or felt in synchronous + inverted MCLK.

"The inverted MCLK ensures that the Sabre noise as low as possible." and there's no further explanations.

Anyone tried these?

As far as I tried myself, (I stolen MCLK from transport via LVDS and made inverted at the LVDS receiver input.)

I felt it's slightly better in SQ, but I can't say surely it's better because I haven't done strict A/B comparison yet.

Besides, I have no skill and equipments to measure noise performance correctly.

I 'm just curious what other people found or felt in synchronous + inverted MCLK.

nope havent tried the inverted MCLK, its on my list of to do's though, thanks for reminding me

Hello

Can I ask what the difference in sound quality is when you go from synchronous as apposed to asynchronous.

Regards

Arthur

Can I ask what the difference in sound quality is when you go from synchronous as apposed to asynchronous.

Regards

Arthur

Hi, PHEONIX

As far as I have noticed, syncronous mode gives better separation, As if each instruments/voices reproduced with each own location.

On the contrary, when async, I felt some instruments or voices appears in the same location.

This kind of improvement sometimes seemed to result in such as "less muddy", "more revealed" sounds.

I recommend you to try yourself if you are interested. 🙂

As far as I have noticed, syncronous mode gives better separation, As if each instruments/voices reproduced with each own location.

On the contrary, when async, I felt some instruments or voices appears in the same location.

This kind of improvement sometimes seemed to result in such as "less muddy", "more revealed" sounds.

I recommend you to try yourself if you are interested. 🙂

Hi, PHEONIX

As far as I have noticed, syncronous mode gives better separation, As if each instruments/voices reproduced with each own location.

On the contrary, when async, I felt some instruments or voices appears in the same location.

This kind of improvement sometimes seemed to result in such as "less muddy", "more revealed" sounds.

I recommend you to try yourself if you are interested. 🙂

Hello wtk_smile

Can your describe your dac setup to me, what hardware and software control do you use.

SDTrans384 - i2s, including MCLK - Buffalo2 DAC

I use Arduino with Hifiduino code as a external dac controller.

It's very useful for buffalo2 dac because variable resister settings were very limited in stock MCU.

OSF bypass function required for 176.4khz or higher sample rate as in my current setup DAC's MCLK

are 22.5792mhz or 24.576mhz.

I only had experienced syncronous clocking using SDtrans384 and QA-550, both worked well.

Some - or many, I'm not sure - async usb-i2s DDC converters also should work in the same way.

Here's a example

Synchronous clocking the Buff 2 - Buffalo DAC - Twisted Pear Audio Support

I use Arduino with Hifiduino code as a external dac controller.

It's very useful for buffalo2 dac because variable resister settings were very limited in stock MCU.

OSF bypass function required for 176.4khz or higher sample rate as in my current setup DAC's MCLK

are 22.5792mhz or 24.576mhz.

I only had experienced syncronous clocking using SDtrans384 and QA-550, both worked well.

Some - or many, I'm not sure - async usb-i2s DDC converters also should work in the same way.

Here's a example

Synchronous clocking the Buff 2 - Buffalo DAC - Twisted Pear Audio Support

the phase is inverted, i have an invert MCLK phase register on my USB->i2s convertor as well and it appears it has a postive effect. i guess only Dustin can tell us why it benefits the ess dacs, but i guess it must not be that unusual. maybe it has something to do with latching onto the incoming clock more reliably

Hello Wktk_Smile

>I use Arduino with Hifiduino code as a external dac controller.

Which Arduino board do you use.

Regards

Arthur

>I use Arduino with Hifiduino code as a external dac controller.

Which Arduino board do you use.

Regards

Arthur

Hi guys,

Has anyone had any luck making sense of the Registers #48-71?

They are supposed to provide a lot of information on the status of the s/pdif channel like clock accuracy, sample frequency, word length, etc.

I am not having trouble reading them, but I'm getting a bunch of 0s on most of them that don't really seem to match up to the data I should be getting according to the datasheet.

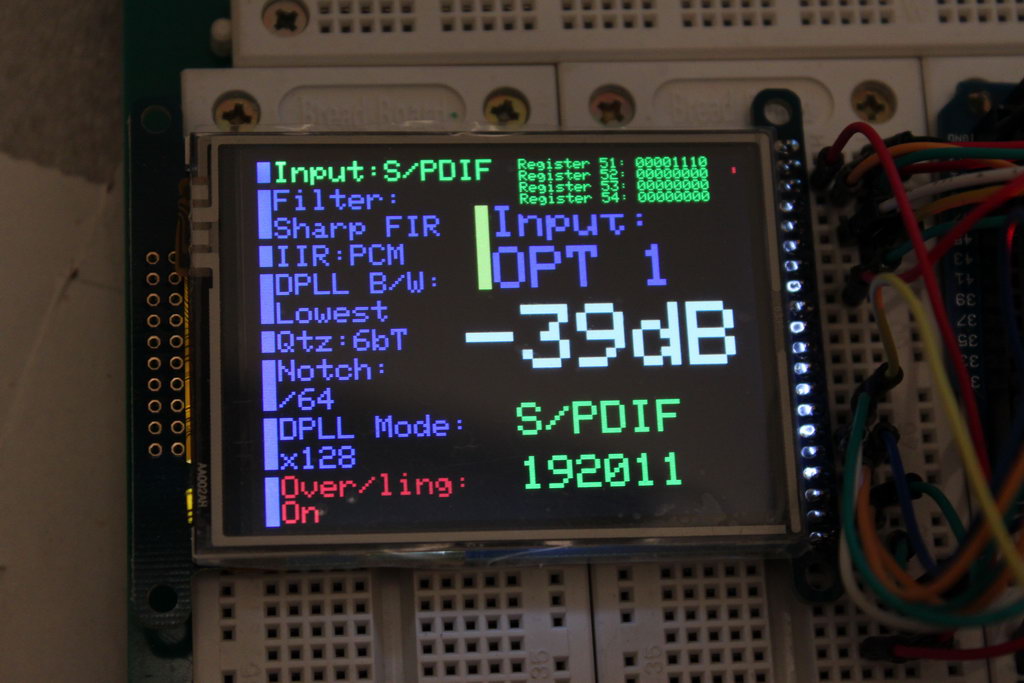

I am using a modified version of the Hifiduino code on a Mega with a 2.8" TFT screen.

(btw, great job glt, I am really greatful for the code)

Has anyone had any luck making sense of the Registers #48-71?

They are supposed to provide a lot of information on the status of the s/pdif channel like clock accuracy, sample frequency, word length, etc.

I am not having trouble reading them, but I'm getting a bunch of 0s on most of them that don't really seem to match up to the data I should be getting according to the datasheet.

I am using a modified version of the Hifiduino code on a Mega with a 2.8" TFT screen.

(btw, great job glt, I am really greatful for the code)

Here you go:

Obviously it is still in development (and on a breadboard 😛).

The only useful information that I have managed to get from registers 48-71 is the sampling rate (see Register 51 above).

I was hoping to get some more info but the rest of the registers appear to be all zeroes.

Obviously it is still in development (and on a breadboard 😛).

The only useful information that I have managed to get from registers 48-71 is the sampling rate (see Register 51 above).

I was hoping to get some more info but the rest of the registers appear to be all zeroes.

Attachments

Dimdim,

Very nice!

I ordered a MEGA and also TFT screen... (the widescreen model from iTead). Will have to wait for the library to be updated...

Regarding the SPDIF registers, I get the feeling they are not used/populated. Think about it, where would the data come from?

Any luck programming the filters?

Very nice!

I ordered a MEGA and also TFT screen... (the widescreen model from iTead). Will have to wait for the library to be updated...

Regarding the SPDIF registers, I get the feeling they are not used/populated. Think about it, where would the data come from?

Any luck programming the filters?

I assume you ordered the ITDB02-3.2WD, right? It's a very attractive display. Does iTead have any sort of an ETA on the library?

Regarding the registers, I am guessing that since they exist and are read only, it would make sense for them to actually contain data. For instance, the word length.

I have not gotten to the filters yet.. I have put on pause the development of the controller since I'm busy building the actual DAC (B III).

Regarding the registers, I am guessing that since they exist and are read only, it would make sense for them to actually contain data. For instance, the word length.

I have not gotten to the filters yet.. I have put on pause the development of the controller since I'm busy building the actual DAC (B III).

Regarding the registers, I am guessing that since they exist and are read only, it would make sense for them to actually contain data. For instance, the word length.

Hi, Dimdim,

What kind of S/PDIF source device are you using? Is it configured to send "channel status information" through the S/PDIF?

Bunpei

In the Sabre dac app note, ESS recommends inverted MCLK when that's synchronous, although they only says

"The inverted MCLK ensures that the Sabre noise as low as possible." and there's no further explanations.

Anyone tried these?

As far as I tried myself, (I stolen MCLK from transport via LVDS and made inverted at the LVDS receiver input.)

Hi, wktk_smile,

I'm not sure that this information has something to do with your interest.

The following Japanese web page by a DAC designer reported a possible noise. You may understand the contents written in Japanese language.

DAC

Bunpei

Last edited:

Hi, Dimdim,

What kind of S/PDIF source device are you using? Is it configured to send "channel status information" through the S/PDIF?

Bunpei

I'm testing with two sources: a common DVD player and a PC's on-board sound.

I also have a Behringer SRC2496, perhaps I should try with that as well, since it supports a number of output options.

- Home

- Source & Line

- Digital Line Level

- ESS Sabre Reference DAC (8-channel)