Have you configured the I2S input/output ports for your task?Anybody have idea what I have doing wrong?

Take the project sigma studio from this thread and see how I configured the I2S ports, in this project the I2S port output is clocked from the BCLK frequency at the I2S input. ASRC is also used there for the input and output of the I2S stream.

https://www.diyaudio.com/community/threads/3way-dsp-amp-adapter-for-dante-aes67-board.426074/

Thanks, I am not, probably neither is configured correctly, sigma studio is realy confusing, whatever I set its always seems analog instead of digital. What I need is simple 10 band parametric equ, one input and one output, not need mute, volume, asrc, just that 10 band equ and simple i2s input and i2s output. or at least something very simple, just input and output, neither I tried is working, probably because of wrong configuration in sigma studio. And have no idea how to debug since I didn't included pinouts for adi usb device, thinked that things will work on first try but seems I was very wrong. I have only i2c option left for comunication with adau1462. Unable to understand sigma studio, even unable to get on the net any simple i2s example flow in-out with external mclk.

On the other hand I burned out all 3 comtrue, two srcs and one usb, have no idea if that was in realtion to soldering or something killed it for example adau killed it? Replaced all 3 and still can't get adau to flow pulses to their out. I2c comunication is working, reset circuit too, but no pulses and have no idea right now what to try : (

On the other hand I burned out all 3 comtrue, two srcs and one usb, have no idea if that was in realtion to soldering or something killed it for example adau killed it? Replaced all 3 and still can't get adau to flow pulses to their out. I2c comunication is working, reset circuit too, but no pulses and have no idea right now what to try : (

Last edited:

First src ic doing anyhing2pcm, fixed rate 48k, master clock is 12.288MHz, osciloscope tells that src is working on bck, data, lrck. And things goes to the adau in0 and out0 but why it didn't pulses at out is realy strange for me, must be that I didn't configured sigma studio corectly, clock, pin function, or something else.

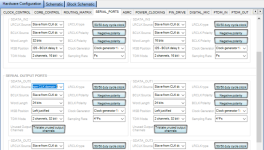

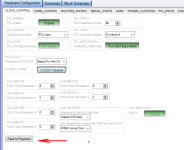

this is how adau is used in our ddpd v2, using adau for the first time

this is how adau is used in our ddpd v2, using adau for the first time

Last edited:

To begin with, I would advise you to get a connection between Sigmastudio and ADAU using a USBi programmer.I2c comunication is working, reset circuit too, but no pulses and have no idea right now what to try : (

This is necessary to read the ADAU settings, there are a lot of settings inside the ADAU that can lead to a negative result. Without USBi, you will not see how ADAU is configured, i.e. you will not be able to see and understand the reason for the ADAU not working in your case....

Yes but too late, didn't included pinouts for usb : ( Must hack pcb in order to make that usb comunication. I have usb device for programming. I thinked things will be easy to do trought i2c but seems I was very wrong. Compoinents is 0201, too small for hacking anyhing : (

I don't know why you need a master clock if the adau has ASRC, but as I understand it, in order to use the master clock without ASRC, you need to supply the master clock to the adau clock pin, and this requires settings inside the adau.

You can unsolder the microcontroller and solder an external USB programmer to the I2C terminals of the ADAU. Or programmatically switch the MC ports to the Z state and simply solder the wires from the programmer to the I2C channel.Yes but too late, didn't included pinouts for usb :

USBi will work on two pins only? And trird pin gnd. If yes I will try add ipex connector at bottom layer, i2c line is available at bottom layer so I can try hack pcb and add two ipex connectors for i2c

This is because ADAU has its own ASRC, and therefore it can output a signal via I2S in the slave via an external clock on the BCLK pin. Simply put, ADAU does not need a master clock, and there are simply no examples for this case.Unable to understand sigma studio, even unable to get on the net any simple i2s example flow in-out with external mclk.

Yes. I2C works, but it still requires three pins, the third pin is ground.USBi will work on two pins only?

I'm using generated C code from adau, so it generates default_download routine with all things configured allready so no need to stop anything because routine does all that step by step until all i2c bytes is transfered to the adau. But if I use USBi than I will need to do things manualy as you say. Thank you, I will check, it must be something in that relation that clock is not configured corectly, also my i2c send 701 bytes in one cycle, i will try to split it to chunks, that might probably fail on stm32f411, than if neither work I will try add ipex connectors for i2c hack

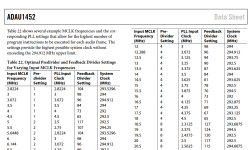

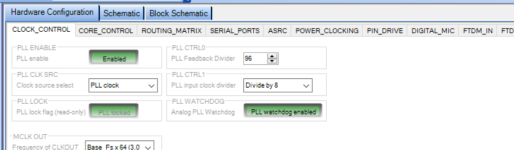

My mclk is 12.288, and I set clock source "direct from mclk", and per table looks like my clock is correct? Than something else is missing. Have no idea how to setup i2s source, there is some clock domains which I not understand what that mean or how to configure them, for example what mean clock domain 0, clock domain 1... clock domain 4... etc, unclear : (

Attachments

Last edited:

Since there are four I2S inputs in the ADAU, for the I2S slave reception mode you can clock I2S data from different BCLK inputs, in other words, if your BCLK clock signal comes to the ADAU BCLK IN0 input, then you need to specify domain 0 in the port settings.for example what mean clock domain 0, clock domain 1... clock domain 4... etc, unclear : (

Power clocking seems diferent in sigma studio 4.7 , I have enable that serial 0 input and output, but nothing is working. Today I will try hack our pcb and add somehow ipex connectors on i2c line to connect with USBi, no choices left for debuging : (

Seems sigma studio have bugs? For example I see that trace on pictures is all green even when something is disabled? Or this window is for real time work when USBi is connected? Do I need to send all that commands after default_download?? For example this function default_download configures adau device:

looks like 0xF650 command for serial ports enable is missing in default_downloaf routine generated by sigma studio?

Seems sigma studio have bugs? For example I see that trace on pictures is all green even when something is disabled? Or this window is for real time work when USBi is connected? Do I need to send all that commands after default_download?? For example this function default_download configures adau device:

Code:

void default_download() {

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOFT_RESET_ADDR, REG_SOFT_RESET_BYTE, R0_SOFT_RESET_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOFT_RESET_ADDR, REG_SOFT_RESET_BYTE, R1_SOFT_RESET_Default );

SIGMA_WRITE_DELAY( DEVICE_ADDR, R2_RESET_DELAY_SIZE, R2_RESET_DELAY_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_HIBERNATE_ADDR, REG_HIBERNATE_BYTE, R3_HIBERNATE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_HIBERNATE_ADDR, REG_HIBERNATE_BYTE, R4_HIBERNATE_Default );

SIGMA_WRITE_DELAY( DEVICE_ADDR, R5_HIBERNATE_DELAY_SIZE, R5_HIBERNATE_DELAY_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_KILL_CORE_ADDR, REG_KILL_CORE_BYTE, R6_KILL_CORE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_KILL_CORE_ADDR, REG_KILL_CORE_BYTE, R7_KILL_CORE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_PLL_ENABLE_ADDR, REG_PLL_ENABLE_BYTE, R8_PLL_ENABLE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_PLL_CTRL1_ADDR, REG_PLL_CTRL1_BYTE, R9_PLL_CTRL1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_PLL_CLK_SRC_ADDR, REG_PLL_CLK_SRC_BYTE, R10_PLL_CLK_SRC_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_MCLK_OUT_ADDR, REG_MCLK_OUT_BYTE, R11_MCLK_OUT_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_PLL_ENABLE_ADDR, REG_PLL_ENABLE_BYTE, R12_PLL_ENABLE_Default );

SIGMA_WRITE_DELAY( DEVICE_ADDR, R13_PLL_LOCK_DELAY_SIZE, R13_PLL_LOCK_DELAY_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_POWER_ENABLE0_ADDR, REG_POWER_ENABLE0_BYTE, R14_POWER_ENABLE0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_POWER_ENABLE1_ADDR, REG_POWER_ENABLE1_BYTE, R15_POWER_ENABLE1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_BLOCKINT_EN_ADDR, REG_BLOCKINT_EN_BYTE, R16_BLOCKINT_EN_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SDATA_OUT3_PIN_ADDR, REG_SDATA_OUT3_PIN_BYTE, R17_SDATA_OUT3_PIN_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_ASRC_INPUT0_ADDR, REG_ASRC_INPUT0_BYTE, R18_ASRC_INPUT0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_ASRC_OUT_RATE0_ADDR, REG_ASRC_OUT_RATE0_BYTE, R19_ASRC_OUT_RATE0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE0_ADDR, REG_SOUT_SOURCE0_BYTE, R20_SOUT_SOURCE0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE1_ADDR, REG_SOUT_SOURCE1_BYTE, R21_SOUT_SOURCE1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE2_ADDR, REG_SOUT_SOURCE2_BYTE, R22_SOUT_SOURCE2_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE3_ADDR, REG_SOUT_SOURCE3_BYTE, R23_SOUT_SOURCE3_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE4_ADDR, REG_SOUT_SOURCE4_BYTE, R24_SOUT_SOURCE4_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE5_ADDR, REG_SOUT_SOURCE5_BYTE, R25_SOUT_SOURCE5_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE6_ADDR, REG_SOUT_SOURCE6_BYTE, R26_SOUT_SOURCE6_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE7_ADDR, REG_SOUT_SOURCE7_BYTE, R27_SOUT_SOURCE7_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE8_ADDR, REG_SOUT_SOURCE8_BYTE, R28_SOUT_SOURCE8_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE9_ADDR, REG_SOUT_SOURCE9_BYTE, R29_SOUT_SOURCE9_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE10_ADDR, REG_SOUT_SOURCE10_BYTE, R30_SOUT_SOURCE10_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE11_ADDR, REG_SOUT_SOURCE11_BYTE, R31_SOUT_SOURCE11_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE12_ADDR, REG_SOUT_SOURCE12_BYTE, R32_SOUT_SOURCE12_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE13_ADDR, REG_SOUT_SOURCE13_BYTE, R33_SOUT_SOURCE13_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE14_ADDR, REG_SOUT_SOURCE14_BYTE, R34_SOUT_SOURCE14_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE15_ADDR, REG_SOUT_SOURCE15_BYTE, R35_SOUT_SOURCE15_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE16_ADDR, REG_SOUT_SOURCE16_BYTE, R36_SOUT_SOURCE16_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE17_ADDR, REG_SOUT_SOURCE17_BYTE, R37_SOUT_SOURCE17_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE18_ADDR, REG_SOUT_SOURCE18_BYTE, R38_SOUT_SOURCE18_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE19_ADDR, REG_SOUT_SOURCE19_BYTE, R39_SOUT_SOURCE19_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE20_ADDR, REG_SOUT_SOURCE20_BYTE, R40_SOUT_SOURCE20_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE21_ADDR, REG_SOUT_SOURCE21_BYTE, R41_SOUT_SOURCE21_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE22_ADDR, REG_SOUT_SOURCE22_BYTE, R42_SOUT_SOURCE22_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SOUT_SOURCE23_ADDR, REG_SOUT_SOURCE23_BYTE, R43_SOUT_SOURCE23_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_0_0_ADDR, REG_SERIAL_BYTE_0_0_BYTE, R44_SERIAL_BYTE_0_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_0_1_ADDR, REG_SERIAL_BYTE_0_1_BYTE, R45_SERIAL_BYTE_0_1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_1_0_ADDR, REG_SERIAL_BYTE_1_0_BYTE, R46_SERIAL_BYTE_1_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_1_1_ADDR, REG_SERIAL_BYTE_1_1_BYTE, R47_SERIAL_BYTE_1_1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_2_0_ADDR, REG_SERIAL_BYTE_2_0_BYTE, R48_SERIAL_BYTE_2_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_2_1_ADDR, REG_SERIAL_BYTE_2_1_BYTE, R49_SERIAL_BYTE_2_1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_3_0_ADDR, REG_SERIAL_BYTE_3_0_BYTE, R50_SERIAL_BYTE_3_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_3_1_ADDR, REG_SERIAL_BYTE_3_1_BYTE, R51_SERIAL_BYTE_3_1_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_4_0_ADDR, REG_SERIAL_BYTE_4_0_BYTE, R52_SERIAL_BYTE_4_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_5_0_ADDR, REG_SERIAL_BYTE_5_0_BYTE, R53_SERIAL_BYTE_5_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_6_0_ADDR, REG_SERIAL_BYTE_6_0_BYTE, R54_SERIAL_BYTE_6_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_SERIAL_BYTE_7_0_ADDR, REG_SERIAL_BYTE_7_0_BYTE, R55_SERIAL_BYTE_7_0_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, PROGRAM_ADDR, PROGRAM_SIZE, Program_Data );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, PARAM_ADDR, PARAM_SIZE, Param_Data );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, DM1_DATA_ADDR, DM1_DATA_SIZE, DM1_DATA_Data );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_KILL_CORE_ADDR, REG_KILL_CORE_BYTE, R59_KILL_CORE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_START_ADDRESS_ADDR, REG_START_ADDRESS_BYTE, R60_START_ADDRESS_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_START_PULSE_ADDR, REG_START_PULSE_BYTE, R61_START_PULSE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_START_CORE_ADDR, REG_START_CORE_BYTE, R62_START_CORE_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_START_CORE_ADDR, REG_START_CORE_BYTE, R63_START_CORE_Default );

SIGMA_WRITE_DELAY( DEVICE_ADDR, R64_START_DELAY_SIZE, R64_START_DELAY_Default );

SIGMA_WRITE_REGISTER_BLOCK( DEVICE_ADDR, REG_HIBERNATE_ADDR, REG_HIBERNATE_BYTE, R65_HIBERNATE_Default );

}looks like 0xF650 command for serial ports enable is missing in default_downloaf routine generated by sigma studio?

Attachments

Last edited:

Sigma Studio seems to remember the last state of the registers in ADAU, to find out the current state of the registers you need to press the read button.Seems sigma studio have bugs? For example I see that trace on pictures is all green even when something is disabled? Or this window is for real time work when USBi is connected? Do I need to send all that commands after default_download??

I don’t know how and when these settings are transferred to ADAU.

I'm checked now default download, this is what is does:

This:

addr: 0x70, regAddr: 0xF050, len: 0x2, values: { 0x1D, 0x11 }

is responsible for power clocking, for example writing 0x1D11 to the register 0xF050 defines the whole power clocking output scheme, in our case as like on my power clocking window that things is allready done from function default_download, excatly what sigma studio generated during linking project. So in my case something is not good, maybe adau died too when all 3 comtrue died? Or I missing something in sigma studio, realy have no idea

Code:

root@dm920 /media/hdd/ADAU1462 # ./adau

addr: 0x70, regAddr: 0xF890, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF890, len: 0x2, values: { 0x00, 0x01 }

waiting 5312 us

addr: 0x70, regAddr: 0xF400, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF400, len: 0x2, values: { 0x00, 0x01 }

waiting 5312 us

addr: 0x70, regAddr: 0xF403, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF403, len: 0x2, values: { 0x00, 0x01 }

addr: 0x70, regAddr: 0xF003, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF001, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF002, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF005, len: 0x2, values: { 0x00, 0x01 }

addr: 0x70, regAddr: 0xF003, len: 0x2, values: { 0x00, 0x01 }

waiting 5312 us

addr: 0x70, regAddr: 0xF050, len: 0x2, values: { 0x1D, 0x11 }

addr: 0x70, regAddr: 0xF051, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF450, len: 0x2, values: { 0x00, 0x01 }

addr: 0x70, regAddr: 0xF797, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF100, len: 0x2, values: { 0x00, 0x01 }

addr: 0x70, regAddr: 0xF140, len: 0x2, values: { 0x00, 0x05 }

addr: 0x70, regAddr: 0xF180, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF181, len: 0x2, values: { 0x00, 0x0A }

addr: 0x70, regAddr: 0xF182, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF183, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF184, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF185, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF186, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF187, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF188, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF189, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF18A, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF18B, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF18C, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF18D, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF18E, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF18F, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF190, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF191, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF192, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF193, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF194, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF195, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF196, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF197, len: 0x2, values: { 0x00, 0x02 }

addr: 0x70, regAddr: 0xF200, len: 0x2, values: { 0x00, 0x40 }

addr: 0x70, regAddr: 0xF201, len: 0x2, values: { 0x00, 0x22 }

addr: 0x70, regAddr: 0xF204, len: 0x2, values: { 0x90, 0x00 }

addr: 0x70, regAddr: 0xF205, len: 0x2, values: { 0x00, 0x22 }

addr: 0x70, regAddr: 0xF208, len: 0x2, values: { 0x90, 0x40 }

addr: 0x70, regAddr: 0xF209, len: 0x2, values: { 0x00, 0x22 }

addr: 0x70, regAddr: 0xF20C, len: 0x2, values: { 0x90, 0x00 }

addr: 0x70, regAddr: 0xF20D, len: 0x2, values: { 0x00, 0x22 }

addr: 0x70, regAddr: 0xF210, len: 0x2, values: { 0x90, 0x40 }

addr: 0x70, regAddr: 0xF214, len: 0x2, values: { 0x90, 0x00 }

addr: 0x70, regAddr: 0xF218, len: 0x2, values: { 0x90, 0x00 }

addr: 0x70, regAddr: 0xF21C, len: 0x2, values: { 0x90, 0x00 }

addr: 0x70, regAddr: 0xC000, len: 0x2C0, values: { 0x00, 0x00, 0x00, 0x02, 0x0C, 0x00, 0xDC, 0xDC, 0x0D, 0x00, 0xFF, 0xD2, 0x0D, 0x00, 0xFF, 0xD0, 0x0D, 0x00, 0xF4, 0x50, 0x0D, 0x00, 0xF4, 0x00, 0xC0, 0x00, 0x23, 0x80, 0x80, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x23, 0x00, 0x80, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x23, 0xC0, 0x80, 0x00, 0x00, 0x10, 0xC0, 0x00, 0x22, 0x00, 0x80, 0x00, 0x00, 0x00, 0x08, 0x80, 0xDC, 0xE0, 0x0C, 0x00, 0xDC, 0xDC, 0x0A, 0x21, 0x00, 0x12, 0x08, 0x00, 0x00, 0x10, 0x01, 0x00, 0x00, 0x14, 0x06, 0x40, 0x40, 0x10, 0x0A, 0x21, 0x00, 0x16, 0x08, 0x00, 0x00, 0x14, 0x01, 0x00, 0x00, 0x18, 0x06, 0x40, 0x50, 0x10, 0xC0, 0x00, 0x20, 0x00, 0x80, 0x00, 0x00, 0x2B, 0x0D, 0x00, 0xFF, 0xC1, 0xC0, 0x00, 0x20, 0x00, 0x80, 0x00, 0x00, 0x01, 0x0D, 0x00, 0xF4, 0x62, 0xC0, 0x00, 0x20, 0x00, 0x80, 0x00, 0x00, 0x00, 0x0D, 0x00, 0xF4, 0x62, 0xC0, 0x00, 0x20, 0x00, 0x80, 0x00, 0x00, 0x02, 0x0D, 0x00, 0xFF, 0xD1, 0x00, 0x00, 0x00, 0x03, 0x0D, 0x00, 0xFF, 0xD2, 0x00, 0x00, 0x00, 0x05, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x02, 0x01, 0x00, 0x26, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x08, 0x9E, 0xDC, 0xE0, 0x08, 0x9C, 0x00, 0x14, 0x08, 0x9A, 0x00, 0x10, 0x00, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x4F, 0x00, 0x00, 0x08, 0x8A, 0xDC, 0xE0, 0x0A, 0x23, 0x00, 0x06, 0x0A, 0x2B, 0x00, 0x07, 0x00, 0x88, 0x20, 0x00, 0x0A, 0xA7, 0x00, 0x05, 0x00, 0x00, 0x00, 0x22, 0xC0, 0x00, 0x2D, 0x30, 0x80, 0x00, 0x50, 0x00, 0x30, 0x00, 0xB4, 0x6A, 0x00, 0x88, 0x20, 0x00, 0xC0, 0x00, 0x28, 0x70, 0x80, 0x00, 0x60, 0x00, 0x02, 0x09, 0x00, 0x4C, 0x00, 0x8C, 0x11, 0x91, 0x00, 0x00, 0x00, 0x24, 0x00, 0x8C, 0x2A, 0x02, 0x30, 0x00, 0xBC, 0xE9, 0x00, 0x84, 0x0D, 0x9C, 0x00, 0x20, 0x0B, 0x2D, 0x00, 0x00, 0xC2, 0xF1, 0x01, 0x00, 0x00, 0x4A, 0x06, 0x00, 0x50, 0x14, 0x36, 0x40, 0x50, 0x15, 0x26, 0x40, 0x40, 0x15, 0x09, 0x2B, 0x00, 0x06, 0x09, 0x2B, 0x00, 0x07, 0x00, 0x00, 0x00, 0x00, 0x0C, 0x00, 0xFC, 0x40, 0x06, 0x40, 0x10, 0x0E, 0x0C, 0x00, 0xFC, 0x41, 0x06, 0x40, 0x10, 0x1E, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x0E, 0x00, 0x04, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x1D, 0x00, 0x00, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x6F, 0x00, 0x18, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x7F, 0x00, 0x08, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x2F, 0x00, 0x21, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x3F, 0x00, 0x36, 0xC0, 0x00, 0x08, 0x0F, 0x8D, 0x80, 0x00, 0x4F, 0x03, 0x06, 0x00, 0x6E, 0xC0, 0x00, 0x0D, 0x91, 0x80, 0x42, 0xFD, 0x84, 0xC0, 0x00, 0x0D, 0x81, 0x80, 0x06, 0xFD, 0x94, 0x00, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x0B, 0x91, 0x80, 0x46, 0xFD, 0xA0, 0xC0, 0x00, 0x0C, 0x11, 0x80, 0x12, 0xFD, 0x84, 0xC0, 0x00, 0x0C, 0x01, 0x80, 0x06, 0xFD, 0x94, 0x00, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x0A, 0x11, 0x80, 0x16, 0xFD, 0xA0, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x6F, 0x00, 0x18, 0x03, 0x05, 0x00, 0x7F, 0xC0, 0x00, 0x0D, 0x81, 0x80, 0x43, 0xFD, 0x84, 0xC0, 0x00, 0x0D, 0x91, 0x80, 0x07, 0xFD, 0x94, 0x00, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x0B, 0x81, 0x80, 0x47, 0xFD, 0xA0, 0xC0, 0x00, 0x0C, 0x01, 0x80, 0x13, 0xFD, 0x84, 0xC0, 0x00, 0x0C, 0x11, 0x80, 0x07, 0xFD, 0x94, 0x00, 0x00, 0x00, 0x00, 0xC0, 0x00, 0x0A, 0x01, 0x80, 0x17, 0xFD, 0xA0, 0xC0, 0x00, 0x00, 0x00, 0x82, 0x7F, 0x00, 0x08, 0x05, 0x0C, 0x10, 0x0E, 0x05, 0x2C, 0x10, 0x1E, 0xFC, 0x74, 0x80, 0x00, 0x80, 0x02, 0x09, 0xC3, 0xE0, 0x3A, 0x80, 0x00, 0x80, 0x00, 0x01, 0x22, 0xF0, 0x68, 0x80, 0x0B, 0x88, 0x02, 0x3D, 0xC2, 0x03, 0x05, 0x00, 0x96, 0xE0, 0xA1, 0x00, 0x07, 0x8C, 0x0A, 0x05, 0x22, 0xFA, 0x64, 0xE8, 0x4F, 0x88, 0x83, 0xC7, 0x22, 0xF4, 0x66, 0xE8, 0xC3, 0x88, 0x83, 0xC5, 0x3E, 0xE2, 0xA5, 0x00, 0x07, 0x8C, 0x8A, 0x05, 0x22, 0xF1, 0x74, 0xE0, 0x4F, 0x88, 0x02, 0x05, 0xC3, 0xF0, 0x68, 0xE0, 0xCB, 0x88, 0x02, 0x3D, 0xC2, 0xE0, 0xA1, 0x00, 0x07, 0x8C, 0x0A, 0x05, 0x22, 0xE0, 0x00, 0x68, 0x4F, 0x88, 0x80, 0x00, 0x00, 0xE0, 0x00, 0x68, 0xC0, 0x80, 0x00, 0x00, 0x00, 0xE2, 0xA5, 0x00, 0x00, 0x80, 0x00, 0x00, 0x20, 0x05, 0x4D, 0x10, 0x2E, 0x05, 0x6D, 0x10, 0x3E, 0x06, 0x00, 0x10, 0x2E, 0x06, 0x00, 0x90, 0x3E, 0x0D, 0x10, 0xFC, 0xC0, 0x08, 0x80, 0x00, 0x10, 0x08, 0x82, 0x00, 0x14, 0x00, 0x00, 0x20, 0x01, 0x00, 0x00, 0x21, 0x01, 0x09, 0x80, 0x00, 0x10, 0x09, 0x82, 0x00, 0x14, 0x00, 0x00, 0x00, 0x02, 0x0C, 0x10, 0xF4, 0x60, 0x02, 0xC2, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00 }

addr: 0x70, regAddr: 0x0, len: 0x1C0, values: { 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x50, 0x00, 0x00, 0x00, 0x50, 0x00, 0x00, 0x00, 0x1C, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x40, 0x00, 0x00, 0x00, 0x40, 0x00, 0x00, 0x00, 0x20, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x20, 0x8A, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00 }

addr: 0x70, regAddr: 0x6000, len: 0x190, values: { 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00 }

addr: 0x70, regAddr: 0xF403, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF404, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF401, len: 0x2, values: { 0x00, 0x08 }

addr: 0x70, regAddr: 0xF402, len: 0x2, values: { 0x00, 0x00 }

addr: 0x70, regAddr: 0xF402, len: 0x2, values: { 0x00, 0x01 }This:

addr: 0x70, regAddr: 0xF050, len: 0x2, values: { 0x1D, 0x11 }

is responsible for power clocking, for example writing 0x1D11 to the register 0xF050 defines the whole power clocking output scheme, in our case as like on my power clocking window that things is allready done from function default_download, excatly what sigma studio generated during linking project. So in my case something is not good, maybe adau died too when all 3 comtrue died? Or I missing something in sigma studio, realy have no idea

It could be anything you want. From bad soldering to incorrect ADAU settings. Until you see the actual ADAU settings, you can guess for a long time.So in my case something is not good, maybe adau died to when all 3 comtrue died?

- Home

- Amplifiers

- Class D

- Direct Digital Power DAC (DDPD)