Miro gave the option to inject external power supplies at those 0R jumper points.

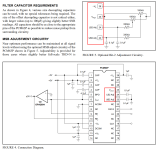

If you don’t have the proper testing equipment for MSB adjustments, better off not populating the circuit, more likely to make things worse than better.

If you don’t have the proper testing equipment for MSB adjustments, better off not populating the circuit, more likely to make things worse than better.

For the option of external power like Vunce mentioned, and also for separate PSU between the two channels if you wish.Why are so many resistors R0 required?

I would like to have this opportunity)Miro gave the option to inject external power supplies at those 0R jumper points.

If you don’t have the proper testing equipment for MSB adjustments, better off not populating the circuit, more likely to make things worse than better.

I also wanted to ask if it is possible, if desired, to connect a digital filter (spdiff) here?

Probably you can have digital filters and OS implemented, but since the essence of Miro's designs of the various DACs stemmed from avoiding them, you probably no longer can call it this :

😀😀

😀😀

Do you mean the switcher implemented directly in the I2S to PCM CPLD (2 functions in 1 CPLD? 😁) ... it is possible, but it needs a lot of testing and coding 🤓@miro1360 I really appreciate the efforts you are putting in to help DIY community making different variations of excellent DACs which are better than many commercial products.

I recently noticed another addition to the project which is CPLD based logic to replace the shift registers. Although I have never played with Altera or Xilinx devices before but having a general idea I was thinking wouldn't it be possible to develop signal switching (I2S 2-3 in 1 out or emulation of shift registers and then out to the DAC chips), with the hope that EPM240 has enough juice and memory to do it.

Just an idea..

Have ordered a few boards though.

The easiest way is to use this inputs selector as separate device 🤔 #2909

This is possible with CPLD, but you need to modify the VHDL code to fit the SAA7030 🤣Hello @miro1360 i was watching the great converter you made for the TDA 1540, and i was wondering if it could be used with SAA7030 and TDA1540 for oversampling.

yes that's what i was thinking (aloud) may be add a visual interface. Well that will depend how fast I could learn/implement VHDL I guess. I think its more efficient this way. While I was doing some surfing I did come across a gentleman who had implemented the core of PCM2706 in CPLD as college project.Do you mean the switcher implemented directly in the I2S to PCM CPLD (2 functions in 1 CPLD? 😁) ... it is possible, but it needs a lot of testing and coding 🤓

The easiest way is to use this inputs selector as separate device 🤔 #2909

Lets see.

About post#2909 I already have the boards with my, populated all of them now I have a few extra. I am keeping only 2 of them.

@rehanabid

I implemented that switch into the 20-bit project, untested, you can test it.

Connect button on pin 3 and GND (pin 3 will be shorted to the GND with this button).

There is not implemented debouncer in code. I tried to avoid it by configuring the input as schmitt trigger (maybe it does not work that way and switching inputs will be chaotic - if so, try to add a small capacitor (47nF?) on pin 3 and GND as a passive button debouncer).

Maybe it won't work at all 😁

I implemented that switch into the 20-bit project, untested, you can test it.

Connect button on pin 3 and GND (pin 3 will be shorted to the GND with this button).

There is not implemented debouncer in code. I tried to avoid it by configuring the input as schmitt trigger (maybe it does not work that way and switching inputs will be chaotic - if so, try to add a small capacitor (47nF?) on pin 3 and GND as a passive button debouncer).

Maybe it won't work at all 😁

Attachments

@rehanabid

I implemented that switch into the 20-bit project, untested, you can test it.

Connect button on pin 3 and GND (pin 3 will be shorted to the GND with this button).

There is not implemented debouncer in code. I tried to avoid it by configuring the input as schmitt trigger (maybe it does not work that way and switching inputs will be chaotic - if so, try to add a small capacitor (47nF?) on pin 3 and GND as a passive button debouncer).

Maybe it won't work at all

Thanks @miro1360 just waiting for my boards to arrive, which are currently stuck in customs. With eid holidays and all that hopefully receive them somewhere next week, after that I will start experimenting with them.

Hopefully will come-up with something, should i succeed will share it here.

miro highly appreciate you willingness to share, efforts of your hard work with the DIY community.

@rehanabid

Now I figured out, that you asked for "3 I2S inputs to 1 PCM output" and I created the opposite (1 I2S input to 3 PCM outputs)

Here is the correct version "3 I2S inputs to 1 20-bit PCM output" 😎

Now I figured out, that you asked for "3 I2S inputs to 1 PCM output" and I created the opposite (1 I2S input to 3 PCM outputs)

Here is the correct version "3 I2S inputs to 1 20-bit PCM output" 😎

Attachments

thanks miro will experiment with the code once I receive the cpld boards. once successfully tested will share with rest of the board.Now I figured out, that you asked for "3 I2S inputs to 1 PCM output" and I created the opposite (1 I2S input to 3 PCM outputs)

Here is the correct version "3 I2S inputs to 1 20-bit PCM output" 😎

This with CPLD is a real job. There is also Spartan 7 now... 100,000 logical cells...

Even filtration can be done with Spartan.

No one alive has a chance to guess that there is a filter when this processes.

Here is an exercise from the Faculty of Electrical Engineering here on how to do it

http://home.etf.rs/~milic/Solution_Manual/Chapter_4_exercises/Chapter_4_exercises.html

Even filtration can be done with Spartan.

No one alive has a chance to guess that there is a filter when this processes.

Here is an exercise from the Faculty of Electrical Engineering here on how to do it

http://home.etf.rs/~milic/Solution_Manual/Chapter_4_exercises/Chapter_4_exercises.html

Last edited:

And the price is much higher. It doesn't even have to be cheap. I don't care about the price if it's good. Not good but the best.Spartan 7 is FPGA and this is much more complex and FPGA can do almost everything what an engineer can put into that 😊

- Home

- Source & Line

- Digital Line Level

- DAC AD1862: Almost THT, I2S input, NOS, R-2R