The J111 claims 20 mA but in reallity the J113 is 80% of the time at that idss.

@Birjac, the TI noise figure are not that good, but the idea of the good enough matched double Jfet package JE2140 is tempting...

@Birjac, the TI noise figure are not that good, but the idea of the good enough matched double Jfet package JE2140 is tempting...

Last edited:

It will work with that types I checked this afternoon J111 2SK117 etc. BUT somehow with icreased power suply range from +5V to +15V thins are getting better. And very good results 🙂 are obtained with good old 2N4391 in sascade. Better than all contemporary... 🙁Thanks Zoran for the circuitry behavior input.

I use often the J113 with its average 15 to 20 mA (the datasheet says 2 mA...) because it's cheap and good enough for my needs. But the J310 is quieter of course (but x13 the price, ouch !)

.

I have a notion that thes positive "branch" should not be a part of +5V ditial PS? And -15V shoud be "shared" with DAC analog supply? Probably @ThorstenL will give some key about it?

.

@ThorstenL

About the 6Vp-p slightly more than 2Vrms stadard) I think that this is the very good results. Riv of 1500 ohm, droping the DC from 15V to about -7V cca. Io.

In that total Io, +2mA for DAC current should have ben excluded and total Io for the converter circuit drops to 5.2mA Main MPSA18 consuming even less because of 2 other BJTs...

So that is the limit fo current for 6Vp-p output version... Zout should be (i didnt check 🙁 sorry = Riv = 1500 ohms)

One thing is constant with thic circuit THD=0.0081 % among almost every Riv value, and offset does not change a lot and can be easely corrected to 0mV.

.

Again FFT is very good for SE topology and non-complementary design and value of output signal.

I switch the DI from 1N4148 to MPSA18 E-BC connection. 🤢

The + power, I set to +15V, somehow I think that shouldnt be shared with digital +5V of DAC? What do You think?

;

One Q more please, BC857B is the only BJT in SMD package... Can we find the appropriate in TO-92 package?

I tried numerous types but I dint catch the results like one with BC857B SMD

About the 6Vp-p slightly more than 2Vrms stadard) I think that this is the very good results. Riv of 1500 ohm, droping the DC from 15V to about -7V cca. Io.

In that total Io, +2mA for DAC current should have ben excluded and total Io for the converter circuit drops to 5.2mA Main MPSA18 consuming even less because of 2 other BJTs...

So that is the limit fo current for 6Vp-p output version... Zout should be (i didnt check 🙁 sorry = Riv = 1500 ohms)

One thing is constant with thic circuit THD=0.0081 % among almost every Riv value, and offset does not change a lot and can be easely corrected to 0mV.

.

Again FFT is very good for SE topology and non-complementary design and value of output signal.

I switch the DI from 1N4148 to MPSA18 E-BC connection. 🤢

The + power, I set to +15V, somehow I think that shouldnt be shared with digital +5V of DAC? What do You think?

;

One Q more please, BC857B is the only BJT in SMD package... Can we find the appropriate in TO-92 package?

I tried numerous types but I dint catch the results like one with BC857B SMD

Last edited:

Look at what 2A3 at the output of this lets say "MPSA18 IV" does. With Riv=225 ohm we have about 0.9Vp-p @ Riv

next is anode follower direct coupled (No Co) to 2A3. The current trough the main MPSA18 is increased to I think about 12mA (sorry that I didnt display...)

With 3.2Vp-p output and low Zout, with very good FFT and noise floor. To remind these are abstract DC Power Sullies, circuit needs very good ones to aproach these results in the sims...

.

(Actually I was thinking to place 4P1L in triode mode and prepared Riv value for "her", but I dint have spice model at hands... It is not the most fortunate setting for 2A3 in this application, should be different...)

.

Just to illustrate the concept.

.

next is anode follower direct coupled (No Co) to 2A3. The current trough the main MPSA18 is increased to I think about 12mA (sorry that I didnt display...)

With 3.2Vp-p output and low Zout, with very good FFT and noise floor. To remind these are abstract DC Power Sullies, circuit needs very good ones to aproach these results in the sims...

.

(Actually I was thinking to place 4P1L in triode mode and prepared Riv value for "her", but I dint have spice model at hands... It is not the most fortunate setting for 2A3 in this application, should be different...)

.

Just to illustrate the concept.

.

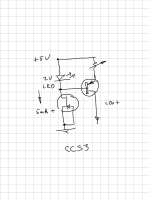

Thanks.Just a comment. J-Fet CCS appear simple, but they cause headaches.

Last edited:

How come, if i recall it should be lower than j310.Birjac, the TI noise figure are not that good, but the idea of the good enough matched double Jfet package JE2140 is tempting...

It is not noise figure only, more is about thansconductance and othe parameters I think? I was tried in sims new models among others and IT and, if I am remeber well, not performing as older types? I dont know I can check again. Main thing is that these MPSA performing good and it does not have SMD version. Somehow I dont like to mix TO-92 and SMD packages on the same device? One or another pd booth but separate... 🙂

Sure, though the voltage across the device and the current through the device is constant, hence is only affected by the ambient. Stacked FET's may be more susceptible to ambient than an LM334, a device that can also be compensated for temperature if required.View attachment 1344127

LM334 Reference voltage is temperature dependent, thus so is the current.

Thor

A high IDSS is required when implementing an LM334 as it needs a minimum operating voltage drop of > 1 Volt to function. In other words the IDSS needs to be higher than the operating current to be shut down by the LM334 while maintaining > 1 Volt drop.The J111 claims 20 mA but in reallity the J113 is 80% of the time at that idss.

@Birjac, the TI noise figure are not that good, but the idea of the good enough matched double Jfet package JE2140 is tempting...

Why not use depletion mosfets in cascade with a Vgs multiplier for CCS? For example BSS159 or BSS139 will give better results than any jfet.

Main MPSA18 consuming even less because of 2 other BJTs...

PNP as "VAS" or control transistor, it runs at minimal current. With 2.4k load to drive the actual main transistor, ~ 250uA.

The + power, I set to +15V, somehow I think that shouldnt be shared with digital +5V of DAC? What do You think?

+5V is what I show using in my "current state" design. It's enough.

One Q more please, BC857B is the only BJT in SMD package... Can we find the appropriate in TO-92 package?

Sorry, should read BC557B, same transistor.

A BC560C would be better choice, but I'm designing for stuff in the junk box.

Sure, though the voltage across the device and the current through the device is constant, hence is only affected by the ambient. Stacked FET's may be more susceptible to ambient than an LM334, a device that can also be compensated for temperature if required.

Yes, so we compensate LM334 for temperature and cascode it with J-Fets send noise is hardly something to write home about. This noise does appear on the output.

What I show is conceptually extremely simple.

SE current conveyor into resistive load, bias CCS to ensure we have enough current in the conveyor.

The downside is that there is no room for error, thermal drift, extra noise.

Thor

Do you have data on the thermal stability?

And which exact LED has the right thermal charactistic, genuinely low noise and production consistency?

And which exact LED has the right thermal charactistic, genuinely low noise and production consistency?

a guy here should answer to that : @abraxalito he used some and have low noise concistency (lower than green led from MVS Audio if I'm not wrong), dunno about thermal !

Then I propose TL431, because thermally it's stable and only needs 1mA. Yes, noisy, but we can filter noise with simple RC.

The Baxandall Super Pair is inherently compensated thermally.

So we make ONE stable reference, filter it's noise, compensate thermal behaviour of the CCS transistors and voila, we get a bunch of very low noise CCS (essentially the compensation follower transistor and the CCS transistor plus resistor) thermally stable and sharable.

If we need extra CCS referenced to the negative line, add a positive CCS nd use a mirror on -15V.

The whole circuit is 100% predictably, reliable and easy to replicate.

Thor

The Baxandall Super Pair is inherently compensated thermally.

So we make ONE stable reference, filter it's noise, compensate thermal behaviour of the CCS transistors and voila, we get a bunch of very low noise CCS (essentially the compensation follower transistor and the CCS transistor plus resistor) thermally stable and sharable.

If we need extra CCS referenced to the negative line, add a positive CCS nd use a mirror on -15V.

The whole circuit is 100% predictably, reliable and easy to replicate.

Thor

Maybe something like Jung GLED

https://www.diyaudio.com/community/threads/mr-jungs-ultra-low-noise-vref-the-gled431.285346/page-4

https://www.diyaudio.com/community/threads/mr-jungs-ultra-low-noise-vref-the-gled431.285346/page-4

Yes it is enough. BUT I am thinking about +5V as more digital PS line? Isnt it better not to be linked to?+5V is what I show using in my "current state" design. It's enough.

I replaced with this type first but somehow it seems that results was not so good... I will check the Spice model.Sorry, should read BC557B, same transistor.

Thanks

.

Jung and others have done work on the topic of LED's as low noise references.Do you have data on the thermal stability?

And which exact LED has the right thermal charactistic, genuinely low noise and production consistency?

How much does it matter in this network? Dump 5mA into a green LED to get above the knee at around 2 Volt drop, giving around a 3 volt drop for the FET for a 5 Volt supply, subtract a VBE drop and insert an appropriate resistor to set an operating point. If you capacitive couple to a tube network how important is the operating point, or the thermals?

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A