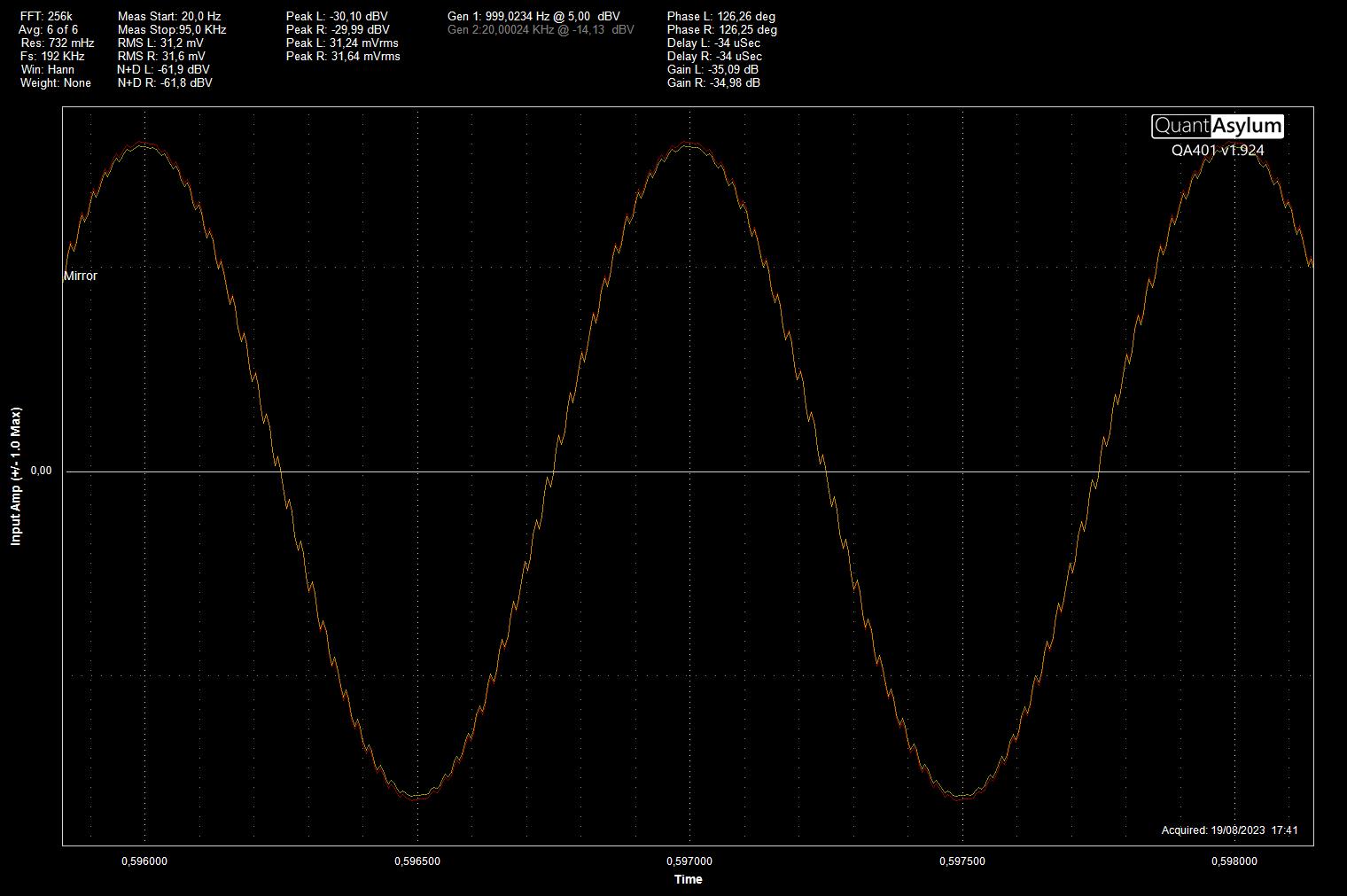

I run the QA401 in time domain today , instead of frequency domain , interresting

but I do not see the offset of the two channel as expected ?

.

but I do not see the offset of the two channel as expected ?

.

I finaly received the sowters trafos 1495 and connect them to my setup , after some testing it seems that i/v resistors are mandatory at the dac output to ground , I have 80 ohms , and no resistor at the secondaries , it does not work

0 mv DC , thanks to the biais trimmer , and the lowest distortion figure thanks to the 10 ohm trimmer

things could get a bit better I think , matter of time

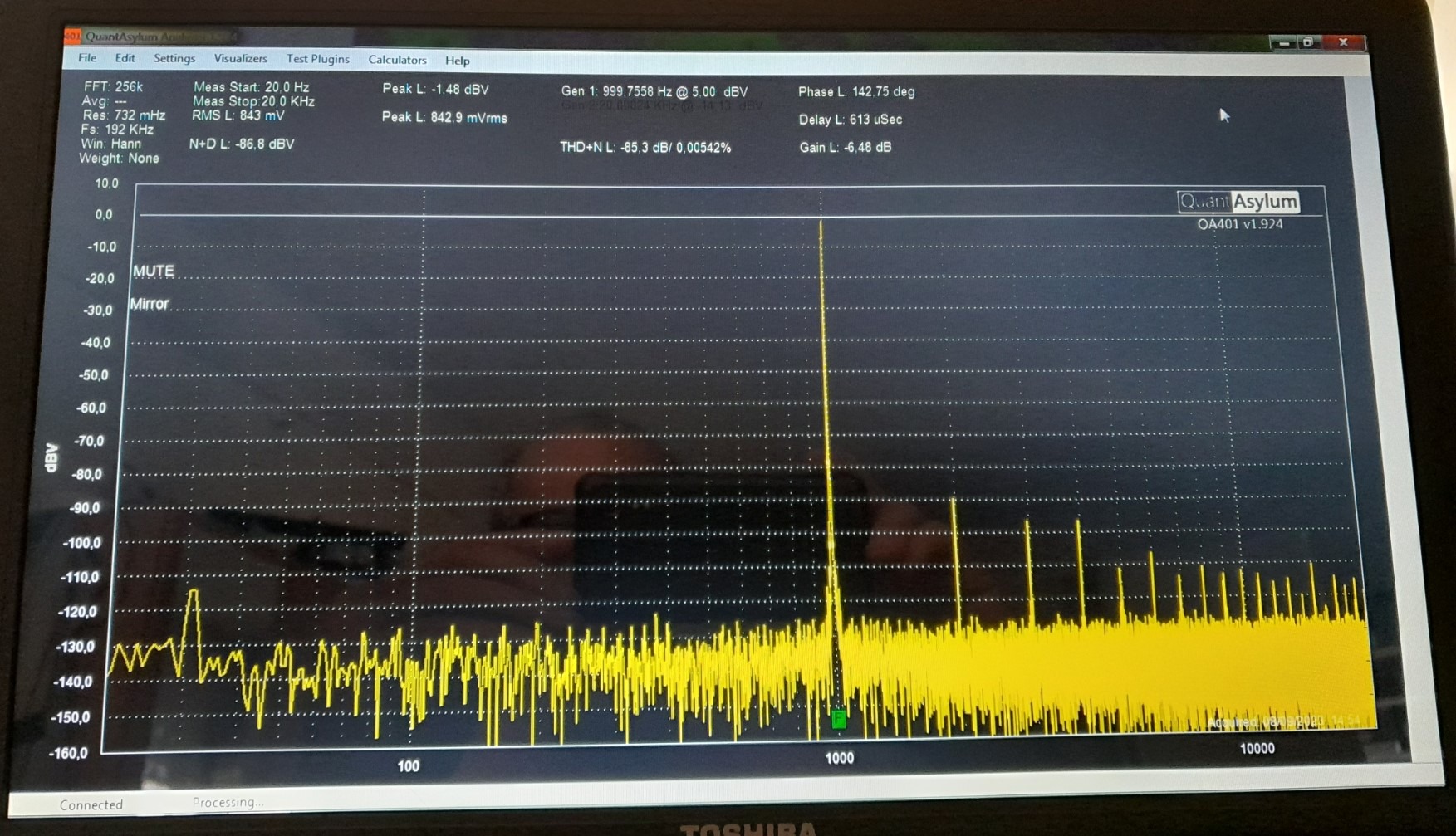

I decided to go parallel , and I got this first result in the audio domain :

secondaries in series give twice the voltage but an slightly higher distorsion figure

now I have to find the good HF filtering method , any passive advice welcome 😉

.

0 mv DC , thanks to the biais trimmer , and the lowest distortion figure thanks to the 10 ohm trimmer

things could get a bit better I think , matter of time

I decided to go parallel , and I got this first result in the audio domain :

secondaries in series give twice the voltage but an slightly higher distorsion figure

now I have to find the good HF filtering method , any passive advice welcome 😉

.

Last edited:

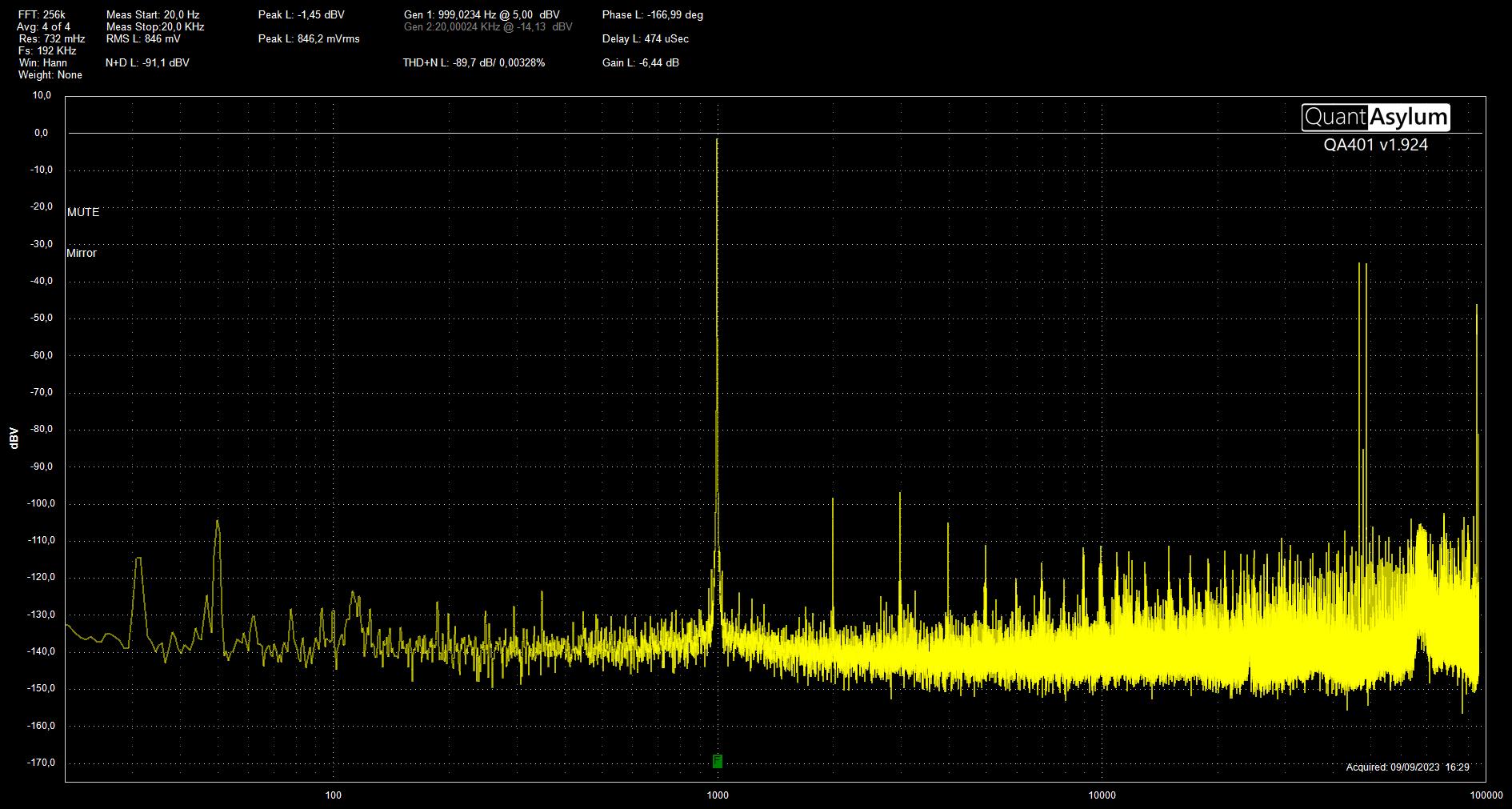

best distortion figure at the moment :

still searching for the best passive HF flitering option

.

still searching for the best passive HF flitering option

.

Last edited:

Real question (no provocation) Why are you so focused on THD ? For me it seems more than low enough. Sure there are other important aspects like power supply capacitor quality etc.

Well , at the moment the setup does not work properly , it only work on mono mode 24 bit , this way it sound great , but only that way , if I set 16 bit and stereo I have the music in the background but the overall is highly distorted

I have verified the all thing many time and the pcb and components are exactly as per John's schematics at post 6116 , left justified not I2S

and measurements shows good numbers as is

fact is I am not able to tell if the schematics are good or not in the first place , so it's a bit difficult for me to find where the error is

not to mention that nobody has ever report listening session on this setup as is

.

I have verified the all thing many time and the pcb and components are exactly as per John's schematics at post 6116 , left justified not I2S

and measurements shows good numbers as is

fact is I am not able to tell if the schematics are good or not in the first place , so it's a bit difficult for me to find where the error is

not to mention that nobody has ever report listening session on this setup as is

.

Last edited:

Ok, so it means the 17bit configuration is still not proven working...? How are you feeding the 17bit data stream into the logic circuit? Do you use 18bit and discard one bit?

BTW I am using the TDA1541A with PMD100 in 8x oversampling mode (simultaneous input), it sounds great, but with very low levels I get distortion, similar to what's described with regard to DEM not working properly. I have the usual 470pF cap connected to the DEM pins, the bit decouplers are 220nF each. When I convert a file from 44.1kHz to 22kHz the distortion becomes less disturbing (but still audible), hence I wonder if the DEM cap needs to be half the value (i.e. 220pF) for fs=384kHz?

BTW I am using the TDA1541A with PMD100 in 8x oversampling mode (simultaneous input), it sounds great, but with very low levels I get distortion, similar to what's described with regard to DEM not working properly. I have the usual 470pF cap connected to the DEM pins, the bit decouplers are 220nF each. When I convert a file from 44.1kHz to 22kHz the distortion becomes less disturbing (but still audible), hence I wonder if the DEM cap needs to be half the value (i.e. 220pF) for fs=384kHz?

The THD should be in the ballpark , this is why I set it first , if it's not there's no way to get any furtherReal question (no provocation) Why are you so focused on THD ? For me it seems more than low enough. Sure there are other important aspects like power supply capacitor quality etc.

the all thing is battery ( lipo ) powered , may be the best way for very low level of noise , and the cap I choose are the best for the job

.

The logic circuit is feed by an DIR9001 build and set as per post 6080

I see. And do you feed the DIR9001 with 24bit data? Or is it 16bit and the other 8 bits are padded with zeros?

The DIR9001 is feed by an usb to spdif CM6631A board , I dont know how it deal's with 16 bit data , but if I set the window's driver at 16 bit it does not work with 16 bit data nor in stereo , as I said driver must be set 24 bit mono

.

.

Make sure the data comes in the right format to the glue logic, otherwise 17bit mode will be impossible. Remember: for simultaneous input you need offset binary. And iirc the DIR9001 outputs left justified, not i2s!

Last edited:

what do you mean as " right format" , the DIR9001 is set 24 bit left justified as the glue logic is build and set for , there is no I2S here

.

.

Last edited:

Fine. But if you use simultaneous input you need offset binary. The DIR9001 outputs two's complement iirc. Just trying to help, because it seems to me there is some problem with data format according to your description...

I appreciate your help , fact is my skills in digital are weak , so I ask a lot a question that help me to understand 😉

I guess John knew this offset binary you talk about and included it in his design in first place , I hope so

.

I guess John knew this offset binary you talk about and included it in his design in first place , I hope so

.

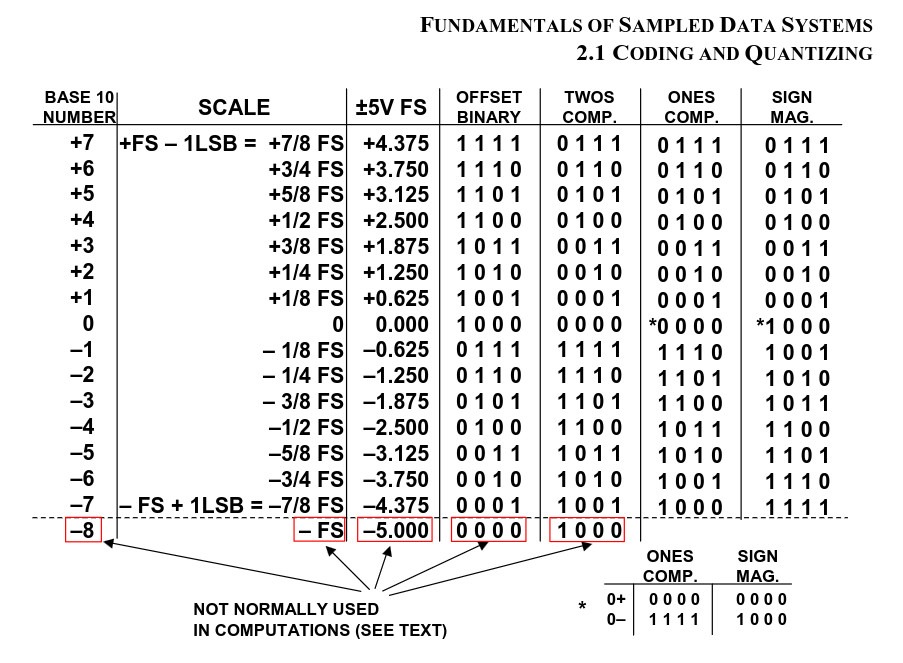

Look (taken from here):

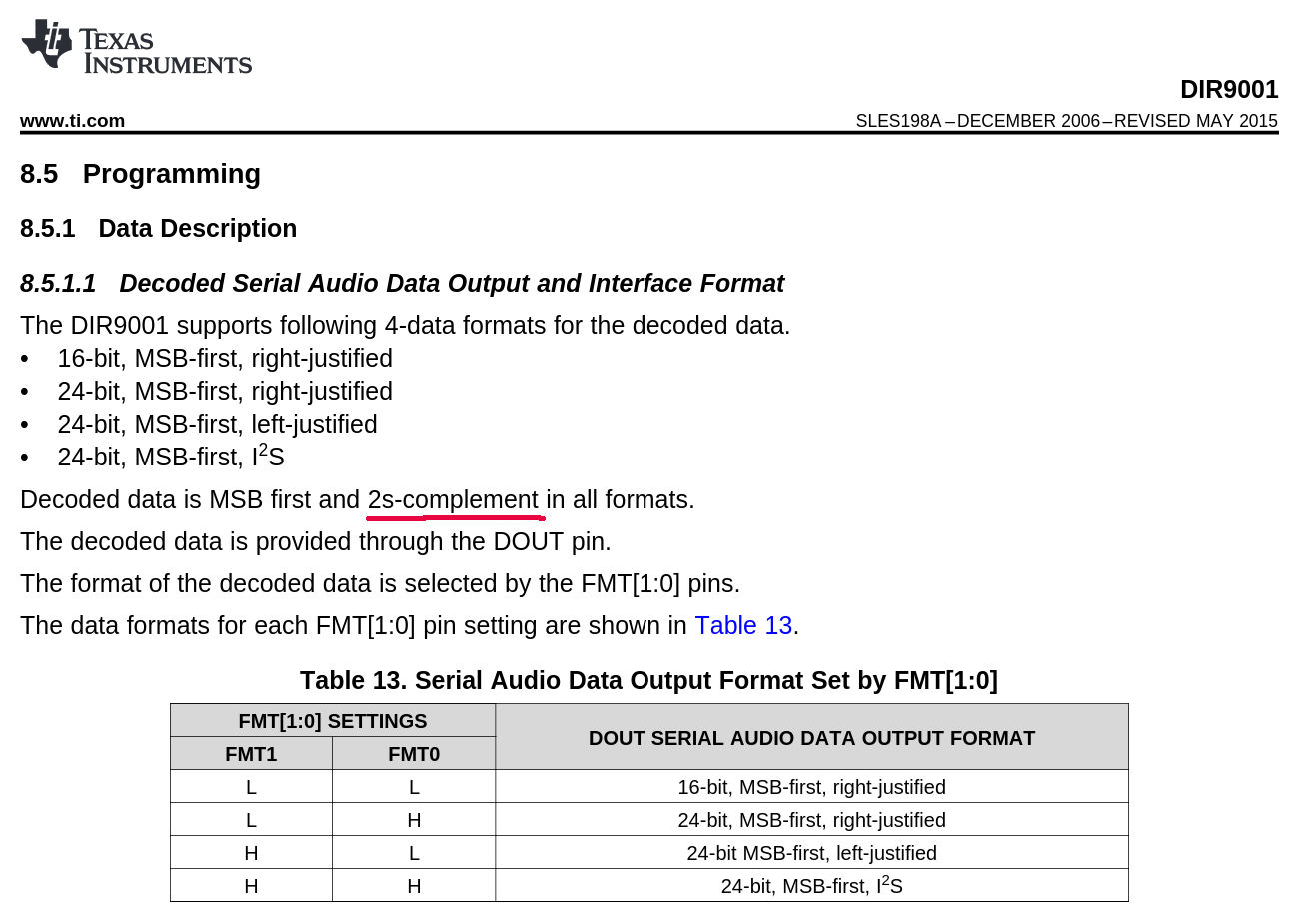

John calls his solution "17bit signed magnitude" DAC, but the DIR9001 outputs "two's complement":

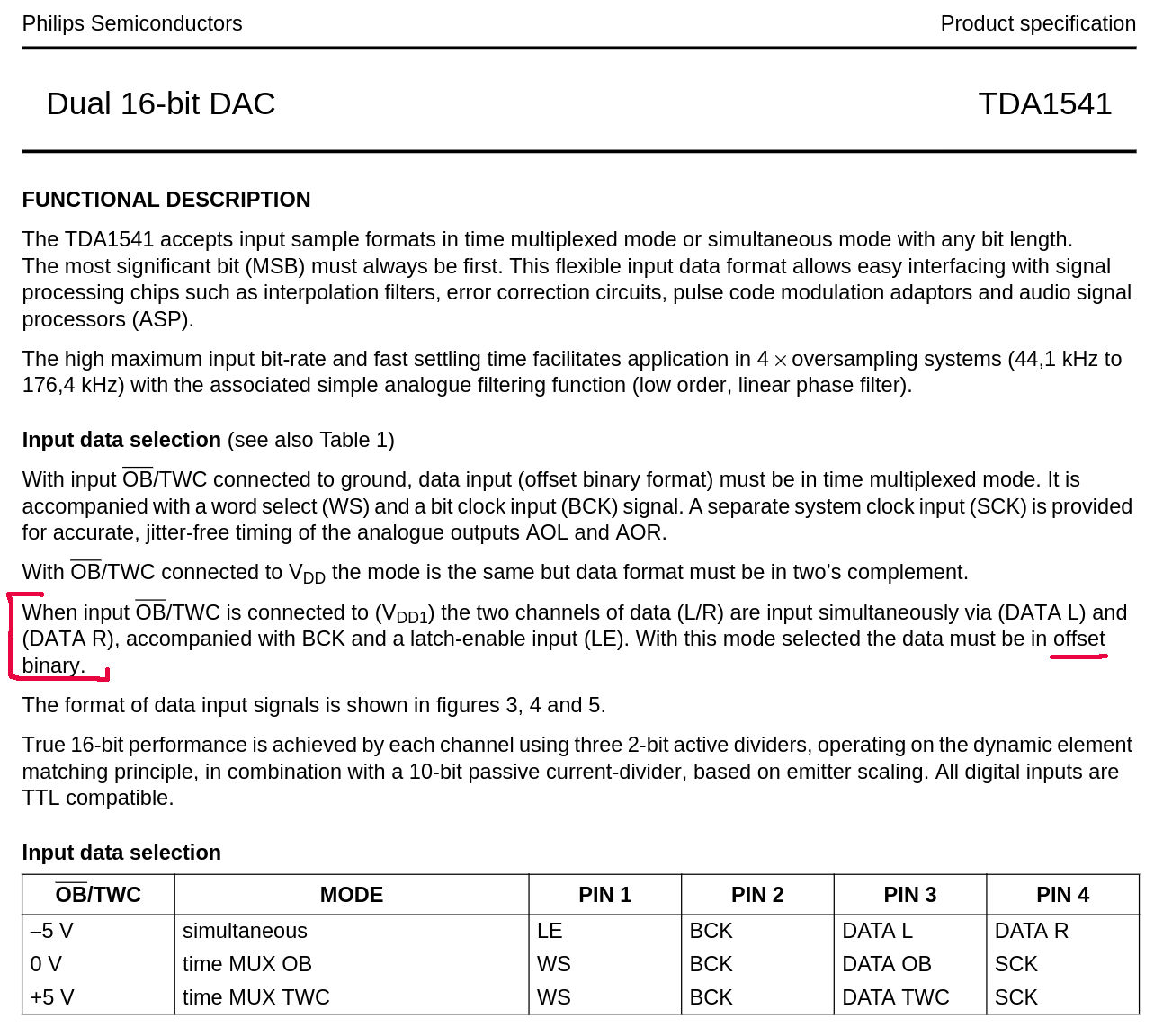

The TDA1541A expects "offset binary" if used in simultaneous mode:

Correct me if I am wrong, but it seems there could be some confusion that leads to the problems you (and others) describe. Did John mention the modul or chip he used as a source for his 17bit DAC?

John calls his solution "17bit signed magnitude" DAC, but the DIR9001 outputs "two's complement":

The TDA1541A expects "offset binary" if used in simultaneous mode:

Correct me if I am wrong, but it seems there could be some confusion that leads to the problems you (and others) describe. Did John mention the modul or chip he used as a source for his 17bit DAC?

I am not able to tell you if you are right or not , I suppose you are

I found reading back in this threads that Johns has made a mistake in his first release of the simultaneous converter they talk about at post 6227 , so it is possible that he has made the same error making the glue logic converter for the 17 bit Signed Magnitude version , but still I am not able to see it

at the time there were guys who said it wont work but nobody tell why , nor point where in the schematics was the problem

so now I know it does not work but I don't know why , and even if it is an issue of binary offset I am not able to fix it

hope someone who knows about that matter will help 😉

.

I found reading back in this threads that Johns has made a mistake in his first release of the simultaneous converter they talk about at post 6227 , so it is possible that he has made the same error making the glue logic converter for the 17 bit Signed Magnitude version , but still I am not able to see it

at the time there were guys who said it wont work but nobody tell why , nor point where in the schematics was the problem

so now I know it does not work but I don't know why , and even if it is an issue of binary offset I am not able to fix it

hope someone who knows about that matter will help 😉

.

Last edited:

iirc John did make various versions of logic for i2s and left justified, but I don't know if he fed his simulations with 2s compliment or COB. What I know from my own TDA1541A project is that I need to program my PMD100 to output COB, otherwise the TDA1541A wont work. I am no fan of NOS, but I would love to use the PMD100 to feed the 17bit signed magnitude DAC. I think that should allow to further simplify the logic - but that's another topic...

If you know about logic you can have a look at the schematic and explanation at post 6116 , this is the one I made , this will be a massive help for me and maybe other people 🙂

.

.

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A