DEM filter capacitors are not likely causing it. I had a similar problem with incorrectly realized reclocking. I do reclocking on the WS signal only.

Today I change my venerable 3009 trimpots on the biasing circuit by these : https://www.mouser.fr/ProductDetail/71-1280G-500-K ,I did not expect any change in sound and I can't tell there really are , or maybe in the subjective world , but it is way more easy to set the dc output , to 0.000 mv dc as I wished to , and just for that it worth it 😉

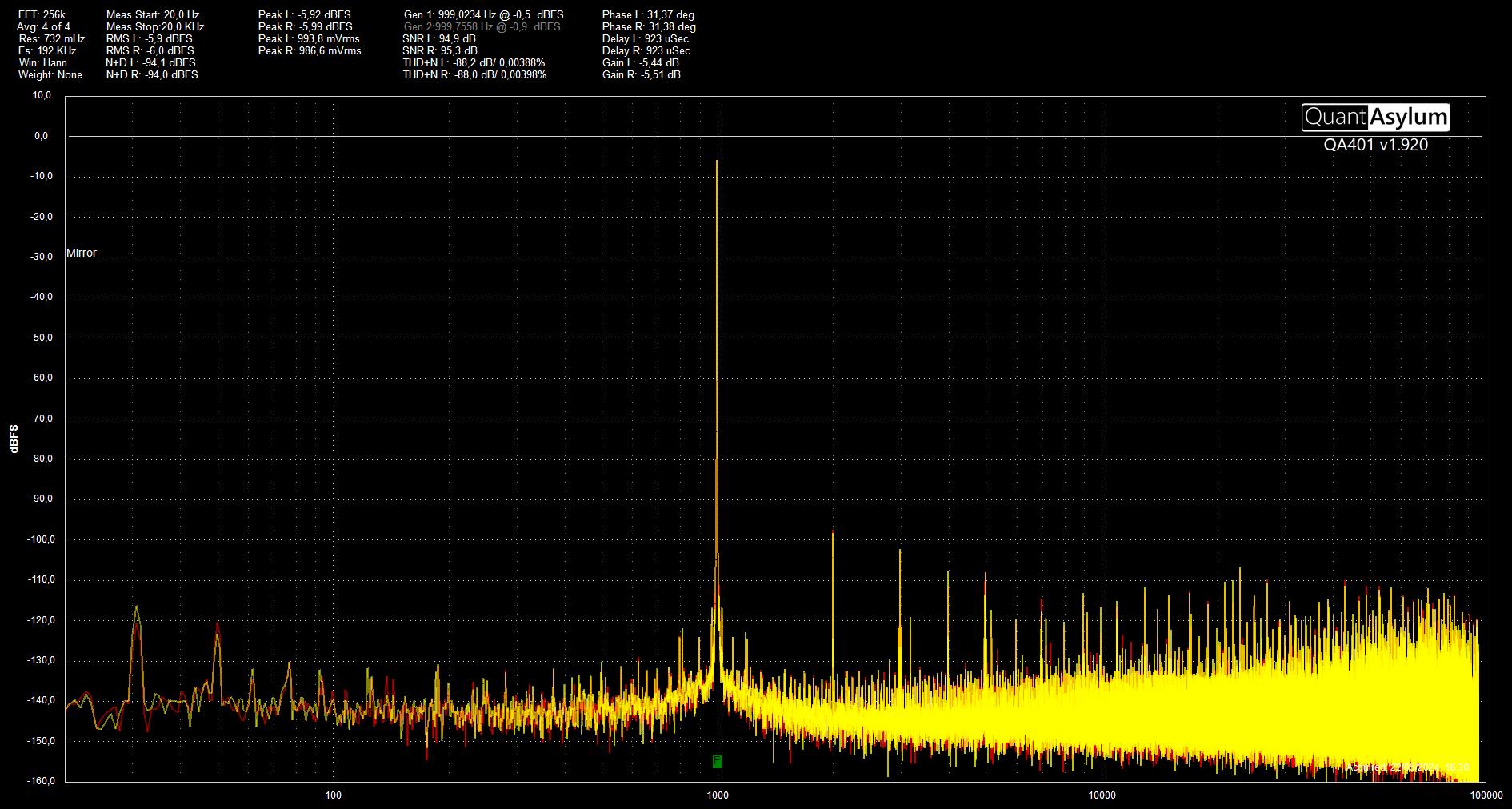

I set the I/V resistor at 50 ohms , it seems to me to be the sweet spot of it , here is the measurement :

trafo ratio is 1:18 , so chip output is 50 mv rms

the transparency of that DAC is amazing , voices and instruments plays like real , the stereo imaging is as wide as possible, tones are so subtils , the balance between low and high is perfect , nothing more nor less

it will be very hard to do any better in an passive setup as it is , with no filtering at all

it has been a great venture , thank's to John from EC-DESIGN in the first place who gave me the start with he's genius ideas , and all of those who cares 😎

.

.

I set the I/V resistor at 50 ohms , it seems to me to be the sweet spot of it , here is the measurement :

trafo ratio is 1:18 , so chip output is 50 mv rms

the transparency of that DAC is amazing , voices and instruments plays like real , the stereo imaging is as wide as possible, tones are so subtils , the balance between low and high is perfect , nothing more nor less

it will be very hard to do any better in an passive setup as it is , with no filtering at all

it has been a great venture , thank's to John from EC-DESIGN in the first place who gave me the start with he's genius ideas , and all of those who cares 😎

.

.

Last edited:

Have you also tried super low I/V like 10 ohm if that is feasible in your system?

Vishay 1280G would be my choice too in a finished design.

Vishay 1280G would be my choice too in a finished design.

I tried down to 30 ohms as I/V , but it doesn't give me enough voltage for the sowters 1495 and the gain in distortion is not that much

.

.

Looking at the harmonics profile on the MVLabs https://www.mvaudiolabs.com/digital/tda1541-iv-resistor-selection/

that 50 ohms looks very interesting, with H2,3,4 dominating; 60 Ohm looks even more interesting, with H7,9 well below the higher ones.

This is unlike 10 ohms which I was considering, where H3 dominates, then H2, and then H7,9, which looks quite ugly (on the plot at least).

With paralleled 1541A, 60R direct to the grid of 801A would give 4mA x 60R=240mV x 7.5 (gain of 801A) = 1.28Vrms, which could be sort of

enough for my power amp which has below 1Vrms sensitivity. But 240mA at the output that's about 10x than the datasheet quotes as the max

that 50 ohms looks very interesting, with H2,3,4 dominating; 60 Ohm looks even more interesting, with H7,9 well below the higher ones.

This is unlike 10 ohms which I was considering, where H3 dominates, then H2, and then H7,9, which looks quite ugly (on the plot at least).

With paralleled 1541A, 60R direct to the grid of 801A would give 4mA x 60R=240mV x 7.5 (gain of 801A) = 1.28Vrms, which could be sort of

enough for my power amp which has below 1Vrms sensitivity. But 240mA at the output that's about 10x than the datasheet quotes as the max

Last edited:

Took me a bit to realize my mistake: It is not the Ohms that matter but the output voltage. At 60R each chips' output is at the equivalent of 120R which is way too much. At Fabrice's 50 Ohms per chip, which looks like a sweet spot, my chain will generate (@lcsaszar I include the max/rms markings for you): 4mAmax x 24R=96mVmax x 7.5 = 0.5Vrms which is lowish. But adding the 1:8 tranny like I planned at the beginning and then attenuating at the TVC at the output should give the needed headroom to drive the amp and as a bonus increased current output of the preamp to drive my 6m interconnects. I actually happen to have 24R Z-foils, giving the equivalent of 48R for 2 chips.

Last edited:

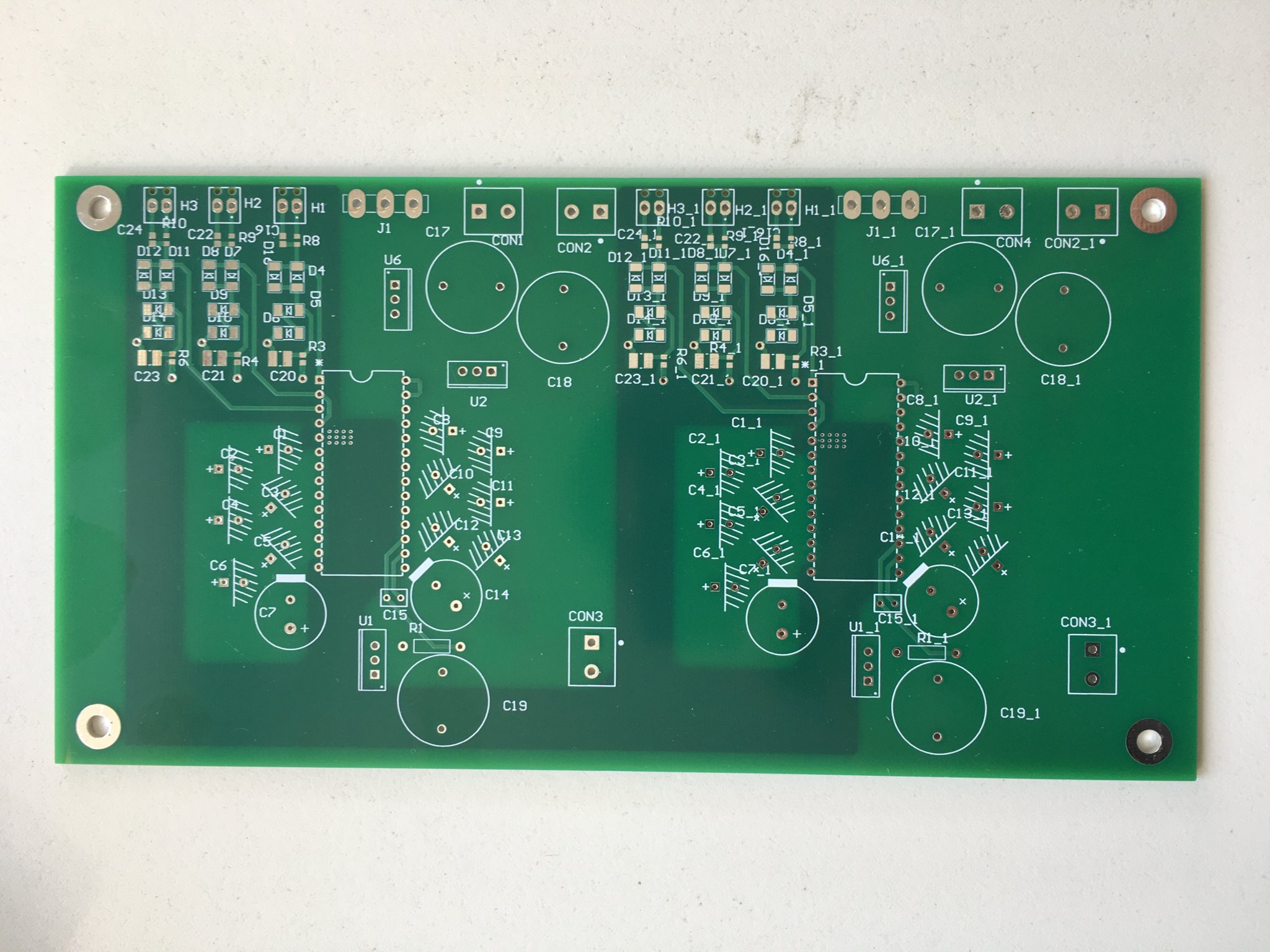

Small step for a Chinese manufacturer, a big step for the project 😁 At this point I’d like to say how mich I hate CircuitMaker. No footprints or wrong footprints, a disaster, never again

Anyone has a fully assembled working dual tda1541 for sale? Balanced or parallel either one. Preferred transformer or tube output please let me know. Been looking for a tda1541 DAC for quite sometime

IMHO your Abbas is good enough, just offer it a better digital frontend USB based over the CS spidf input.

Board almost populated, few small parts left. Soldering SMT, esp 0603 form factor „partisan” way with normal iron was a darn challenge 😀

I wouldnt be an analogue guy without some point to point job 😉

Decouplers - Nichicon KZ and Elna silmic ii between -5 and -15V. The i/v resistors plus biasing still missing

The most tedious part-16pin diy umbilical cable:

I wouldnt be an analogue guy without some point to point job 😉

Decouplers - Nichicon KZ and Elna silmic ii between -5 and -15V. The i/v resistors plus biasing still missing

The most tedious part-16pin diy umbilical cable:

Just recommisioned my dual balanced dac after about a year. (Dir 9001 Spdif trasceiver and Ian Canada's I2s to PCM board)

I remember again why I like that 1541 sound so much.

I'm experimenting with a Behringer Ultramatch SRC2496 to upsample 44.1k 16bit (coax spdif) and 48K 24bit (Toslink) to 96K/24bit.

The result with 48K YT input from my LG tv is so smooth and clean (Sowter I/V transformer output) and very easy to listen to.

I thnk I might look inside for the I2S connections and bypass my Dir9001.

I remember again why I like that 1541 sound so much.

I'm experimenting with a Behringer Ultramatch SRC2496 to upsample 44.1k 16bit (coax spdif) and 48K 24bit (Toslink) to 96K/24bit.

The result with 48K YT input from my LG tv is so smooth and clean (Sowter I/V transformer output) and very easy to listen to.

I thnk I might look inside for the I2S connections and bypass my Dir9001.

Newsflash - A BBFOTO just happened! Everything we think we know about TDA1541 IS WRONG!

Ok folks, I am playing idly with the idea of making another "all out" TDA1541 DAC and I just had a BBFOTO (Big Blinding Flash Of The Obvious).

And no, NOT EVERYTHING is wrong. But a fair bit will need some often minor, yet in audio terms likely significant revision.

Back when I worked on the AMR CD-77 I had a certain fundamental approach, informed by Philips own literature (which I have since lost, but most of which has re-appeared in the public domain since). I'd call that approach the Fast/RF centric one.

Even in today's most radical designs we can see this heritage and I will posit that retaining this heritage is actually "wrong"...

It is physically expressed as a TDA1541 treated as an RF device, with the DEEM Clock synchronised to BCK, low(ish) value small size film DEEM decoupling capacitors, a solid AGND ground plane under the DAC to which all DEEM Pin Cap's are returned and the PSU Pin's as well. Digital inputs are attenuated and slew rate limited.

To be honest, the result in terms of sound quality is excellent. In RF terms this is passable, externally and on the pin's RF tends to be low.

When I get around to restoring my TDA1541 DAC inside the PM-75 Amplifier, I will use this, with Grundig Style DEEM reclock etc. It is too hard to do it otherwise.

But we also know from the work of John (ecdesigns) Brown that an inevitable result of the Fast/RF style use of the TDA1541 is a lot RF feeding through to the analogue out.

I remember well enough the very wide, furry traces of even the best RF style TDA1541 implementation. This is caused by crosstalk on the actual die and leadframes/bondwires and as such no amount of external decoupling, Magic Cap's (TM) etc. will fix this.

This is one of the reasons why Transformer + Tube analogue work so well, there is a lot of HD, but the load resistance of TDA1541 is very low (so the extra RF doesn't eat into the AC compliance and the "fur" get's shaved off the fuzz from our our inchworm trace by the Transformers filtering (plus any after) and what is left usually doesn't bother our tubes.

It is also the reason why the OPA637 I/U conversion works really well.

The Op-Amp is very fast, but to be stable we use a capacitor of 5 X Cfb (typically ~2nF) to ground, so 1.8kOhm // 2nF feedback and 10nF to ground. Make the 10nF a small C0G SMD cap directly to the ground plane, a lot of RF noise disappears and again, our fuzzy inchworm trace of a sinewave get's shaved and cleaned.

However, John and MV-Audiolabs have done a lot of excellent work on how to go further.

For detailed readings and sources of diagrams I will use, MV-Audiolabs is great resource:

https://www.mvaudiolabs.com/digital/

The basic idea I'll call "slow/DC Style". This is based on a few realisations.

1) The actual current sources that determine the output current of the DAC are formed by a (likely temperature compensated) Darlington cascode transistor, a resistor and the external DEEM capacitor. I bit does not determine the instantaneous current.

Image Credit Philips/MV-Audiolabs

The charge in the capacitor is the averaged bit current from the DEEM switching. SO AS LONG as the capacitance value is large enough to "hold" the average compared to current outflow, the circuit is completely self adjusting and accurate, but needs a number of cycles to get to a stable condition.

So small value capacitors need fast DEEM switching, large value capacitors allow slow DEEM switching. In fact, to quote a clear assertion by MVAL:

There is however a bit more to DEEM clock frequencies than meets the eye immediately. The DEEM circuit's switching frequency invariably "breaks through" into our audio output. You can see it at MVAL's site. The key "breakthrough" frequencies are actually Fdeem /2 & /4, not Fdeem itself.

Breakthrough is at low levels, but to reach reliable inaudibility, I think we require a DEEM frequency that fulfils the following strictures:

1) Fdeem must be either greater 20kHz x 4 (> 80kHz) or less than 20Hz x 2 (< 40Hz).

This ensures that the DEEM switching frequency subharmonic breakthrough ends up outside the audible range. Too low a frequency the DEEM switching becomes audible as low level tone! MVAL also observes that modulation at ~ 3-4Hz is most audible/objectionable giving a "wow & flutter" feel, so Fdeem/4 > 4Hz.

2) If using Fdeem > 80kHz the DEEM clock frequency must be synchronised with the word clock and must be AT LEAST 4 X word clock, top ensure all 4 current dividers are used for each sample.

This means:

WCK Fdeem

44.1kHz 176.4kHz

88.2kHz 352.8kHz

176.4kHz 705.6kHz

352.8kHz 1411.2kHz

3) If using Fdeem < 40Hz interactions and interference with Fmains must be considered. Having a free running oscillator will cause beat notes with the mains frequency. In MVAL's example, if we have 50Hz and 48Hz we generate a 2Hz Beat note, the level of which depends on circuit linearity.

The likely best option is to synchronise with the mains frequency which itself has very good stability (otherwise the "grid" does not work, multiple generators must link together and must be frequency and phase-locked, or huge blind currents will flow causing breakers to trip). Generators weighting many tons and spining fast are very stable in terms of rotational speed.

It is easy to get frequencies of Fmains X 2 using a few diodes, an Optocoupler and an extra transistor to square the signal. Use any classic documented differential direct coupled DEEM injection. Maybe like so:

However we may still wish to fulfil the Fdeem < 40Hz stricture.

This means:

Fmains Fdeem Fripple/2 Fripple/4

50Hz 25Hz 12.5Hz 6.25 Hz

60Hz 30Hz 15 Hz 7.5 Hz

50Hz 50Hz 25 Hz 12.5 Hz

60Hz 60Hz 30 Hz 15 Hz

50Hz 100Hz 50 Hz 25 Hz

60Hz 120Hz 60 Hz 30 Hz

With the above I think Fmains x 2 places too much ripple in the audible range, even though MVAL and John Brown both seem to use 100Hz (maybe also down to limitations on the oscillator operating sable at very low frequencies) and Fmains / 2 approaches the VLF limit region. Probably best to try both Fmains clock and Fmains/2 .

So we have determined Fdeem requirements logically.

Next stop, what value DEEM capacitors do we need?

We know current outflow is X and current inflow may be instantaneously (say) +/-5% (which 1980's IC technology should ensure and which RJvdP states as accuracy of the current division).

The variation of voltage in the capacitor due to the variation in current inflow should cause less than 0.25LSB within a single Fdeem period.

So we may use "charge time = C x V/I". So rearranged C = charge time x I / V

We know (roughly) delta I (5% of I bit) and can estimate delta V.

We also know from MVAL that at ~120Hz Fdeem ~680uF on MSB and 100uF on B15 pushes F/2 & F/4 below -118dB, a 10dB or 3-fold improvement over 100uF/100uF.

I would suspect that actual underlying mechanism that lowers the peak is less the capacitance and more the ESR of the capacitor. The KL series is not specified for ESR, but looking at other Nichicon capacitors confirms a 1:3...1:4 ESR ratio for 100uF/25V vs 680uF/25V. I would estimate Nichicon KL 680uF/25V at around 70mOhm.

So nothing new, right?

Not so fast.

Let's look at this picture again:

Vref = +5V

So our output current flows towards +5V, because Philips, instead of making the DAC output balanced "wastes" the unused DAC current to +5V.

But where does all the current flowing in Cext come from? It comes from Ibit and Ibit comes from -15V. We can review this schematic, which is reverse engineered by a eastern european gentleman. Not 100% accurate, but it get's most things right.

First, the main output current loop is -15V to +5V. Preferaby we make one complete power supply, shunt regulated, tapped, making sure that no current escapes.

The signal current from AOL/AOR must return to +5V.

All DEEM logic current generation, analogue references exist between AGND and -15V ONLY.

HOWEVER DEEM decoupling capacitor current returns to -15V. If, because of vestigial "RF" design ideas we first return to AGND, we contaminate the reference pin. Hence the criticality often remarked of sending ALL DEEM capacitors returns ONLY to AGND and the critical decoupling to the -15V pin. If this is done correctly Kirchoffs laws makes sure AGND if the kelvin point, but really, the DEEM Pin currents need to go to -15V. So just connect them there!

+5V (and -5V) are not purely digital pins. However the logic is described thusly by RJvdP:

"In the internal digital part a low-voltage swing unsaturated current-mode logic (CML) is used for speed and low-interference noise."

This means nothing saturates, everything is differential (non-standard ECL in effect) and we get very little logic noise, usually at 2 and higher harmonics (differential circuits in their linear operation). So the logic in use can get contaminated mainly from the digital inputs where logic can be saturated. We prevent this by applying signal conditioning to prevent that.

Again, MVAL has an excellent article on that, I mostly agree with his solution. I do think that instead of diodes, diode connected transistors should be used as references and they should be thermally coupled to the TDA1541. Also, the circuit should make especially sure that data lines cannot drift, with average currents changing. So I would propose an adjustment as follows:

All transistors compensate each others thermal drift, if placed close together. The sensor transistors must be in close thermal contact with TDA1541. The emitter followers present under 8R DC impedance to ground, much lower than two series connected 1N4148. Seeing that the clipping diodes dump significant currents at high frequencies to ground, the signal conditioning circuit should be co-located with the source (and relocking) and arranged on the PCB suitably, so the circulating currents return to their source via a solid ground plane. It needs to oprate from a different power supply than the TDA1541 as well.

The slew rate limited and low swing signals are ideal for our micro-coax, to directly address the TDA1541 pins with minimal current flow in the "ground".

It is obvious that LS/ECL standard decoupling is needed between +5V and DGND and that the grounds from the source coax should connect directly to the DGND pin without involving other ground planes etc.

Finally, I think that the DEEM decoupling requires both our large value electrolytic capacitors and small ones with a tighter loop. Here is why:

John Brown showed precisely what comes out of our DEEM decoupling PIN's. DEEM clock is 384kHz. There is digital feedthrough. But more crucially we see very narrow spikes each time DEEM switches. Noise on these pin's ranges from these narrow 10...20nS spikes caused by the DEEM logic switching (and this is not related to the DEEM frequency, only to the transistors switching speed) to the bit clock and other glitches at every 8th bit clock.

That's pretty broadband and above what our big electrolytics can handle. So we need a -15V plane under the TDA1541 to which we can return this noise using our usual film/ceramic/whatever capacitors. An AGND plane should be below the -15V plane and should also have similar decoupling between AGND & -15V (priority decoupling for high frequencies).

A DGND plane belongs on the top of the PCB to link to +5V for good HF decoupling.

Then -5V links to +5V & -15V via decoupling.

AGND and DGND now meet at the power star, not at AGND pin.

The DGND Plane carries main ground for logic (this is where a lot of current flows) while AGND is treated as analogue reference Pin.

Ultimately a single 20V power supply is made, with taps as needed to give "+5V", "GND", "-5V" & "-15V". This supply is used only for TDA1541 and DEEM sync to mains, nothing else.

All other digital logic is separate on separate supplies, output a pre-conditioned low jitter signal to TDA1541. Grounds only link via Coax Cable grounds.

The analogue stage MUST link it's signal current return to +5V, NOT AGND. It needs low input impedance. If filter capacitors (or impedance compensation capacitors to compensate rising impedance with frequency) are used on the AOL/AOR pins, they must link to +5V not AGND.

This is my analysis so far. I am looking forward to comments, criticisms etc.

Thor

Ok folks, I am playing idly with the idea of making another "all out" TDA1541 DAC and I just had a BBFOTO (Big Blinding Flash Of The Obvious).

And no, NOT EVERYTHING is wrong. But a fair bit will need some often minor, yet in audio terms likely significant revision.

Back when I worked on the AMR CD-77 I had a certain fundamental approach, informed by Philips own literature (which I have since lost, but most of which has re-appeared in the public domain since). I'd call that approach the Fast/RF centric one.

Even in today's most radical designs we can see this heritage and I will posit that retaining this heritage is actually "wrong"...

It is physically expressed as a TDA1541 treated as an RF device, with the DEEM Clock synchronised to BCK, low(ish) value small size film DEEM decoupling capacitors, a solid AGND ground plane under the DAC to which all DEEM Pin Cap's are returned and the PSU Pin's as well. Digital inputs are attenuated and slew rate limited.

To be honest, the result in terms of sound quality is excellent. In RF terms this is passable, externally and on the pin's RF tends to be low.

When I get around to restoring my TDA1541 DAC inside the PM-75 Amplifier, I will use this, with Grundig Style DEEM reclock etc. It is too hard to do it otherwise.

But we also know from the work of John (ecdesigns) Brown that an inevitable result of the Fast/RF style use of the TDA1541 is a lot RF feeding through to the analogue out.

I remember well enough the very wide, furry traces of even the best RF style TDA1541 implementation. This is caused by crosstalk on the actual die and leadframes/bondwires and as such no amount of external decoupling, Magic Cap's (TM) etc. will fix this.

This is one of the reasons why Transformer + Tube analogue work so well, there is a lot of HD, but the load resistance of TDA1541 is very low (so the extra RF doesn't eat into the AC compliance and the "fur" get's shaved off the fuzz from our our inchworm trace by the Transformers filtering (plus any after) and what is left usually doesn't bother our tubes.

It is also the reason why the OPA637 I/U conversion works really well.

The Op-Amp is very fast, but to be stable we use a capacitor of 5 X Cfb (typically ~2nF) to ground, so 1.8kOhm // 2nF feedback and 10nF to ground. Make the 10nF a small C0G SMD cap directly to the ground plane, a lot of RF noise disappears and again, our fuzzy inchworm trace of a sinewave get's shaved and cleaned.

However, John and MV-Audiolabs have done a lot of excellent work on how to go further.

For detailed readings and sources of diagrams I will use, MV-Audiolabs is great resource:

https://www.mvaudiolabs.com/digital/

The basic idea I'll call "slow/DC Style". This is based on a few realisations.

1) The actual current sources that determine the output current of the DAC are formed by a (likely temperature compensated) Darlington cascode transistor, a resistor and the external DEEM capacitor. I bit does not determine the instantaneous current.

Image Credit Philips/MV-Audiolabs

The charge in the capacitor is the averaged bit current from the DEEM switching. SO AS LONG as the capacitance value is large enough to "hold" the average compared to current outflow, the circuit is completely self adjusting and accurate, but needs a number of cycles to get to a stable condition.

So small value capacitors need fast DEEM switching, large value capacitors allow slow DEEM switching. In fact, to quote a clear assertion by MVAL:

"If we connected [an] ideal capacitor having infinite capacitance and let it reach averaged voltage, DEM circuit could be stopped entirely!"

There is however a bit more to DEEM clock frequencies than meets the eye immediately. The DEEM circuit's switching frequency invariably "breaks through" into our audio output. You can see it at MVAL's site. The key "breakthrough" frequencies are actually Fdeem /2 & /4, not Fdeem itself.

Breakthrough is at low levels, but to reach reliable inaudibility, I think we require a DEEM frequency that fulfils the following strictures:

1) Fdeem must be either greater 20kHz x 4 (> 80kHz) or less than 20Hz x 2 (< 40Hz).

This ensures that the DEEM switching frequency subharmonic breakthrough ends up outside the audible range. Too low a frequency the DEEM switching becomes audible as low level tone! MVAL also observes that modulation at ~ 3-4Hz is most audible/objectionable giving a "wow & flutter" feel, so Fdeem/4 > 4Hz.

2) If using Fdeem > 80kHz the DEEM clock frequency must be synchronised with the word clock and must be AT LEAST 4 X word clock, top ensure all 4 current dividers are used for each sample.

This means:

WCK Fdeem

44.1kHz 176.4kHz

88.2kHz 352.8kHz

176.4kHz 705.6kHz

352.8kHz 1411.2kHz

3) If using Fdeem < 40Hz interactions and interference with Fmains must be considered. Having a free running oscillator will cause beat notes with the mains frequency. In MVAL's example, if we have 50Hz and 48Hz we generate a 2Hz Beat note, the level of which depends on circuit linearity.

The likely best option is to synchronise with the mains frequency which itself has very good stability (otherwise the "grid" does not work, multiple generators must link together and must be frequency and phase-locked, or huge blind currents will flow causing breakers to trip). Generators weighting many tons and spining fast are very stable in terms of rotational speed.

It is easy to get frequencies of Fmains X 2 using a few diodes, an Optocoupler and an extra transistor to square the signal. Use any classic documented differential direct coupled DEEM injection. Maybe like so:

However we may still wish to fulfil the Fdeem < 40Hz stricture.

This means:

Fmains Fdeem Fripple/2 Fripple/4

50Hz 25Hz 12.5Hz 6.25 Hz

60Hz 30Hz 15 Hz 7.5 Hz

50Hz 50Hz 25 Hz 12.5 Hz

60Hz 60Hz 30 Hz 15 Hz

50Hz 100Hz 50 Hz 25 Hz

60Hz 120Hz 60 Hz 30 Hz

With the above I think Fmains x 2 places too much ripple in the audible range, even though MVAL and John Brown both seem to use 100Hz (maybe also down to limitations on the oscillator operating sable at very low frequencies) and Fmains / 2 approaches the VLF limit region. Probably best to try both Fmains clock and Fmains/2 .

So we have determined Fdeem requirements logically.

Next stop, what value DEEM capacitors do we need?

We know current outflow is X and current inflow may be instantaneously (say) +/-5% (which 1980's IC technology should ensure and which RJvdP states as accuracy of the current division).

The variation of voltage in the capacitor due to the variation in current inflow should cause less than 0.25LSB within a single Fdeem period.

So we may use "charge time = C x V/I". So rearranged C = charge time x I / V

We know (roughly) delta I (5% of I bit) and can estimate delta V.

| Bit (Pin/Pin) | Bit Current (mA) | Delta BC (mA) | Bit Voltage (V) | Delta BV (mV) | Cmin (uF) 60Hz |

| MSB (13/18) | 2 | 0.1 | -7.5 | 0.0143 | 116 |

| B15 (12/19) | 1 | 0.05 | -7.6 | 0.0145 | 57 |

| B14 (11/20) | 0.5 | 0.025 | -5.5 | 0.0105 | 40 |

| B13 (10/21) | 0.25 | 0.0125 | -5.3 | 0.0101 | 20 |

| B12 (9/22) | 0.125 | 0.00625 | -3.9 | 0.0074 | 14 |

| B11 (8/23) | 0.0625 | 0.003125 | -3.9 | 0.0074 | 7 |

| LSB (7/24) | 0.03125 | 0.0015625 | -3.5 | 0.0067 | 4 |

We also know from MVAL that at ~120Hz Fdeem ~680uF on MSB and 100uF on B15 pushes F/2 & F/4 below -118dB, a 10dB or 3-fold improvement over 100uF/100uF.

I would suspect that actual underlying mechanism that lowers the peak is less the capacitance and more the ESR of the capacitor. The KL series is not specified for ESR, but looking at other Nichicon capacitors confirms a 1:3...1:4 ESR ratio for 100uF/25V vs 680uF/25V. I would estimate Nichicon KL 680uF/25V at around 70mOhm.

So nothing new, right?

Not so fast.

Let's look at this picture again:

Vref = +5V

So our output current flows towards +5V, because Philips, instead of making the DAC output balanced "wastes" the unused DAC current to +5V.

But where does all the current flowing in Cext come from? It comes from Ibit and Ibit comes from -15V. We can review this schematic, which is reverse engineered by a eastern european gentleman. Not 100% accurate, but it get's most things right.

First, the main output current loop is -15V to +5V. Preferaby we make one complete power supply, shunt regulated, tapped, making sure that no current escapes.

The signal current from AOL/AOR must return to +5V.

All DEEM logic current generation, analogue references exist between AGND and -15V ONLY.

HOWEVER DEEM decoupling capacitor current returns to -15V. If, because of vestigial "RF" design ideas we first return to AGND, we contaminate the reference pin. Hence the criticality often remarked of sending ALL DEEM capacitors returns ONLY to AGND and the critical decoupling to the -15V pin. If this is done correctly Kirchoffs laws makes sure AGND if the kelvin point, but really, the DEEM Pin currents need to go to -15V. So just connect them there!

+5V (and -5V) are not purely digital pins. However the logic is described thusly by RJvdP:

"In the internal digital part a low-voltage swing unsaturated current-mode logic (CML) is used for speed and low-interference noise."

This means nothing saturates, everything is differential (non-standard ECL in effect) and we get very little logic noise, usually at 2 and higher harmonics (differential circuits in their linear operation). So the logic in use can get contaminated mainly from the digital inputs where logic can be saturated. We prevent this by applying signal conditioning to prevent that.

Again, MVAL has an excellent article on that, I mostly agree with his solution. I do think that instead of diodes, diode connected transistors should be used as references and they should be thermally coupled to the TDA1541. Also, the circuit should make especially sure that data lines cannot drift, with average currents changing. So I would propose an adjustment as follows:

All transistors compensate each others thermal drift, if placed close together. The sensor transistors must be in close thermal contact with TDA1541. The emitter followers present under 8R DC impedance to ground, much lower than two series connected 1N4148. Seeing that the clipping diodes dump significant currents at high frequencies to ground, the signal conditioning circuit should be co-located with the source (and relocking) and arranged on the PCB suitably, so the circulating currents return to their source via a solid ground plane. It needs to oprate from a different power supply than the TDA1541 as well.

The slew rate limited and low swing signals are ideal for our micro-coax, to directly address the TDA1541 pins with minimal current flow in the "ground".

It is obvious that LS/ECL standard decoupling is needed between +5V and DGND and that the grounds from the source coax should connect directly to the DGND pin without involving other ground planes etc.

Finally, I think that the DEEM decoupling requires both our large value electrolytic capacitors and small ones with a tighter loop. Here is why:

John Brown showed precisely what comes out of our DEEM decoupling PIN's. DEEM clock is 384kHz. There is digital feedthrough. But more crucially we see very narrow spikes each time DEEM switches. Noise on these pin's ranges from these narrow 10...20nS spikes caused by the DEEM logic switching (and this is not related to the DEEM frequency, only to the transistors switching speed) to the bit clock and other glitches at every 8th bit clock.

That's pretty broadband and above what our big electrolytics can handle. So we need a -15V plane under the TDA1541 to which we can return this noise using our usual film/ceramic/whatever capacitors. An AGND plane should be below the -15V plane and should also have similar decoupling between AGND & -15V (priority decoupling for high frequencies).

A DGND plane belongs on the top of the PCB to link to +5V for good HF decoupling.

Then -5V links to +5V & -15V via decoupling.

AGND and DGND now meet at the power star, not at AGND pin.

The DGND Plane carries main ground for logic (this is where a lot of current flows) while AGND is treated as analogue reference Pin.

Ultimately a single 20V power supply is made, with taps as needed to give "+5V", "GND", "-5V" & "-15V". This supply is used only for TDA1541 and DEEM sync to mains, nothing else.

All other digital logic is separate on separate supplies, output a pre-conditioned low jitter signal to TDA1541. Grounds only link via Coax Cable grounds.

The analogue stage MUST link it's signal current return to +5V, NOT AGND. It needs low input impedance. If filter capacitors (or impedance compensation capacitors to compensate rising impedance with frequency) are used on the AOL/AOR pins, they must link to +5V not AGND.

This is my analysis so far. I am looking forward to comments, criticisms etc.

Thor

LOL,, subscribed ! Persisting is existing ! Thanks

Thorsten, you said you haven't tried the simultaneous mode yet ( in order to have a point of view about it, I look forward you try it,, did you already?). With the very late Taiwan chips it is a game changer I have found, Although the way it is made and the layout should matter.

What about the analog output referenced to 5V ?

The diferential input Z of the opa637 is not a bit high ?

What about for instance : opa861, AD811 (the old flavor of the moment here in this forum) I haven't tried that one) : AD1633 (dif op amp), AD828 if low curent noise and capacitance input matters ?)

You use an op amp + bjt + Mosfet hybrid scheme on your Ifi home DAC best home DAC nowadays, is that easier maybe with the high output and low noise of a PCM1793 ?

I focused on your input on some modern chips above in this thread : TDA1541A musicality beated ? (I mean with 16/44 materials)

Thanks for the Summer comeback, I was getting boried by the Olympcs ! 😀

Edit : I wish I had a good 6072A and 5687, I had to be satisfied with solid state or an E188CC. Will you use the same tubes or confs with your nowadays knowledge VS the CD-77 or maybe your personal one that migth be even better cause it is hard to source NIB todays ?

Best

😎

Thorsten, you said you haven't tried the simultaneous mode yet ( in order to have a point of view about it, I look forward you try it,, did you already?). With the very late Taiwan chips it is a game changer I have found, Although the way it is made and the layout should matter.

What about the analog output referenced to 5V ?

The diferential input Z of the opa637 is not a bit high ?

What about for instance : opa861, AD811 (the old flavor of the moment here in this forum) I haven't tried that one) : AD1633 (dif op amp), AD828 if low curent noise and capacitance input matters ?)

You use an op amp + bjt + Mosfet hybrid scheme on your Ifi home DAC best home DAC nowadays, is that easier maybe with the high output and low noise of a PCM1793 ?

I focused on your input on some modern chips above in this thread : TDA1541A musicality beated ? (I mean with 16/44 materials)

Thanks for the Summer comeback, I was getting boried by the Olympcs ! 😀

Edit : I wish I had a good 6072A and 5687, I had to be satisfied with solid state or an E188CC. Will you use the same tubes or confs with your nowadays knowledge VS the CD-77 or maybe your personal one that migth be even better cause it is hard to source NIB todays ?

Best

😎

Last edited:

Not just simultaneous mode,, but also stopping the bit clock once the data is latched and D-A is taking place.

Does IanCanada I2StoPCM did that already iirc ? (though there was a little error and it was 15 bits)

Yes it does. Some say there is an error but I can't hear it (ancient ears though and tinnitus in one so can't give a definitive answer)

This what I use and I find it good as well, nothing seems to miss to my ears. (but I did have to tweak its masterclock a little as its power supply - SC-Cut low frequency is a game changer if you do not use active DEM clocking - for instance for a few I understand, the Grunding DEM mode needs x4 oversampling)

Why not using LRCK DEM slaving in spite of Blck ? Which is the most critical between both ?

I remember John gave up the idea of two TDA1541A due to the too much factory mismatch between two chips related to the substrate parasitics as well and I see he used high voltage in the late iterations (V10 to V14 something ???)

Why not using LRCK DEM slaving in spite of Blck ? Which is the most critical between both ?

I remember John gave up the idea of two TDA1541A due to the too much factory mismatch between two chips related to the substrate parasitics as well and I see he used high voltage in the late iterations (V10 to V14 something ???)

Last edited:

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A