I have checked some cap datasheets, looking for low leakage ones and trying to find something that is available locally. These are not bad, but not as good as the Nichicon UKL:

Nichicon Muse ES: 3uA max.

Nichicon FW: 4uA to 3uA max.

Nichicon KW: 4uA to 3uA max.

Panasonic FC: 3uA max.

Any suggestions for common caps with low leakage?

Nichicon Muse ES: 3uA max.

Nichicon FW: 4uA to 3uA max.

Nichicon KW: 4uA to 3uA max.

Panasonic FC: 3uA max.

Any suggestions for common caps with low leakage?

OK, please ignore the post above, I now understand the leakage spec a bit better. Different for each value and will vary with applied voltage of course.

That said the Pan FC has low leakage Grunf member via J Diden tests. As Nichicon UKZ and UKG.

Pan FC has a plus with the bettet inductance and Nichicon ES the best noise floor but is bipolar. You can not go wrong with FC.

UKL being the reference for leakage but it doesn t say you all in an analog use 🙂

Pan FC has a plus with the bettet inductance and Nichicon ES the best noise floor but is bipolar. You can not go wrong with FC.

UKL being the reference for leakage but it doesn t say you all in an analog use 🙂

Thanks.

This video is not about leakage, but I found it an useful test for caps:

Now I'm looking at how to curve trace transistors with an analog scope in X-Y mode. I think this can be better than digitizing curve tracers, it will give an idea which transistors are the best (for example looking at the "return sweep" as mentioned here: https://www.diyaudio.com/community/threads/jlh-headphone-amp.159202/page-47). If the sweep forms a loop then there's memory distortion (thermal memory, that we have discussed a few times). I took the image from the link above where member jbau looks at curves of small signal transistors.

This video is not about leakage, but I found it an useful test for caps:

Now I'm looking at how to curve trace transistors with an analog scope in X-Y mode. I think this can be better than digitizing curve tracers, it will give an idea which transistors are the best (for example looking at the "return sweep" as mentioned here: https://www.diyaudio.com/community/threads/jlh-headphone-amp.159202/page-47). If the sweep forms a loop then there's memory distortion (thermal memory, that we have discussed a few times). I took the image from the link above where member jbau looks at curves of small signal transistors.

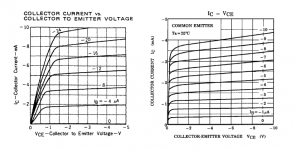

I didn't want to make it too complicated but the choice of transistors is important. What to look for in a datasheet? One important thing is Early voltage. Looking at Ic versus Vce, the more Ic variation over a Vce range, the lower the Early voltage (not good). When Ic stays almost the same over a large Vce variation then V Early is high (good). This is quite important if the circuit has PNP current sources because the PNP usually has much lower Early than the NPN. BTW we should avoid high beta transistors for a PNP current source because high beta usually comes with low Early. We want high early for high CCS impedance.What one should use for the transistors TO-92?

Below you can see data for the 2SA970 (right) and 2SA992 (left). From this data I estimate that A970 has higher Early, about double the Early voltage of the A992. But don't trust the datasheets - check the parts on a curve tracer if possible. An old curve tracer (CRT) shows a lot like I mentioned in the post above. I don't have one, I'm looking into using my analog scope as a curve tracer.

Must have missed that one! Nice pcb, and we used the same schematic i think.Hi Zbunjen,

Good to know somebody is following up on the sign magnitude design. Unfortunately I don't have time to finish my project however I have an assembled but not fully tested board based on the schematic in this post:

https://www.diyaudio.com/community/...ate-nos-dac-using-tda1541a.79452/post-5857535

If you are interested I can send it to you as a reference to play with. Hopefully it could be useful to get the final desing with dual TDAs done.

Reach out to me over PM.

After about 7-8 different iterations i pulled the trigger and i am assembling the boards these days, so we'll see if it works. But it is nice to know i have your support, that's very generous and i might take you up on your offer if i cant troubleshoot mine or maybe even just to play with comparing the two (but it is just digital, so i believe if both are sensibly designed, then if it works it works.. but still thanks for that)

+1 for Nichi UKL1E101KPD and Rubycon TWL. I have both, and measured both, and they are an order of magnitude lower leakage than other cap types. Its pretty hard to substitute a LL cap for a regular one. But yeah, i guess question is about what you can find locally, then...good luck! 🙂I have checked some cap datasheets, looking for low leakage ones and trying to find something that is available locally. These are not bad, but not as good as the Nichicon UKL:

Nichicon Muse ES: 3uA max.

Nichicon FW: 4uA to 3uA max.

Nichicon KW: 4uA to 3uA max.

Panasonic FC: 3uA max.

Any suggestions for common caps with low leakage?

If suggesting FC, why not newer FM at that point?That said the Pan FC has low leakage Grunf member via J Diden tests. As Nichicon UKZ and UKG.

Pan FC has a plus with the bettet inductance and Nichicon ES the best noise floor but is bipolar. You can not go wrong with FC.

UKL being the reference for leakage but it doesn t say you all in an analog use 🙂

I like the FC but to be honest it would be less than ideal for this application...and FM too.

I didn't suggested the Pan FC as alowleakage substitution but in spite of UKZ,UKG... if in for Alexandre needs the UKL was not sourcable locally.

I do not like FM most of the time for analog circuitry but few exceptions and it is not a FC substitution and at the game of the newest the FR is a better hint for digital circuitry. We have all our preference, for instance John like Nichicon UKA and I personnaly do not like it...

Good tip about the Rubycon as low leakage cap, how do you rate it over the UKL, please ? I found a BC but also out of stocks...

I do not like FM most of the time for analog circuitry but few exceptions and it is not a FC substitution and at the game of the newest the FR is a better hint for digital circuitry. We have all our preference, for instance John like Nichicon UKA and I personnaly do not like it...

Good tip about the Rubycon as low leakage cap, how do you rate it over the UKL, please ? I found a BC but also out of stocks...

Last edited:

Makes sense for Alexandre, if he cant get low leakage locally then...I didn't suggested the Pan FC as alowleakage substitution but in spite of UKZ,UKG... if in for Alexandre needs the UKL was not sourcable locally.

I do not like FM most of the time for analog circuitry but few exceptions and it is not a FC substitution and at the game of the newest the FR is a better hint for digital circuitry.

Agreed for analog i wouldnt use it either, but for supply decoupling, FM (and FR as you point out) are king for me for price/performance.

Well, i do not have enough UKL's (need 28 for 2x dac) to use them (so i just tested leakage), and TWL's i use 2x47uf in paralell (so 56 in total). Leakage was basically the same as 100uF single, but at a lower ESR. I wonder if lead inductance will then mess with things, but i expect not.. Anyway, this is what im building still these days so cant even comment on that either! So, sorry for no useful answer 🙂Good tip about the Rubycon as low leakage cap, how do you rate it over the UKL, please ? I found a BC but also out of stocks...

Bah... I have delayed project due to the supplychain problem... I can wait another year for the ukl I need for a clock its power supply.

Great, would love to see and listen how it works out and help if I could.Must have missed that one! Nice pcb, and we used the same schematic i think.

After about 7-8 different iterations i pulled the trigger and i am assembling the boards these days, so we'll see if it works. But it is nice to know i have your support, that's very generous and i might take you up on your offer if i cant troubleshoot mine or maybe even just to play with comparing the two (but it is just digital, so i believe if both are sensibly designed, then if it works it works.. but still thanks for that)

BTW if you would need to debug your sign magnitude or simultaneous logic implementation take a look at sigrok logic analyzer:

https://sigrok.org/wiki/Supported_hardware#Logic_analyzers

Very interesting project, i'll keep this in mind, thanks!Great, would love to see and listen how it works out and help if I could.

BTW if you would need to debug your sign magnitude or simultaneous logic implementation take a look at sigrok logic analyzer:

https://sigrok.org/wiki/Supported_hardware#Logic_analyzers

Of course, i put together the whole thing, 100+ capacitors and so on, and what's missing?

A single LP5907. I thought i had 4 but cant find for the life of me, went through all boxes...this is a part i cant source locally so i have to make an order and wait...sigh..

A single LP5907. I thought i had 4 but cant find for the life of me, went through all boxes...this is a part i cant source locally so i have to make an order and wait...sigh..

I feel your pain!

BTW did I get it right that this is a kind of evaluation board to try to find the best sounding circuit options?

Would you consider creating a stripped down board with the best sounding DEM, audio format, etc circuit after the tests?

BTW did I get it right that this is a kind of evaluation board to try to find the best sounding circuit options?

Would you consider creating a stripped down board with the best sounding DEM, audio format, etc circuit after the tests?

Yes you're right that its a bit of an evaluation board.

And from a user experience standpoint, putting so much features and modes into it become jumper hell to set up, especially if some are clearly inferior and only increase complexity. I basically need to write a manual, and its not ideal.

The plan was to iron out some things, see what is unecessary, what could have been done better etc because there's always something like that you figure out only after building it..

But regarding the best sounding options, it's a bit complex to present myself as authority on what sounds the best, on my system, with my ears, with my music taste etc...but i could certainly make some comments. I wanted to also make measurements and document everything.

Regarding DEM, certainly you could use another one, and there's provisions for smaller SMD caps and such, i thought about it. But honestly i will likely not bother in the end, as the theory of why 50hz was chosen for DEM reclock seems reasonable to me and i dont want to solder and desolder 50 more caps..

I think step one for now is just finishing it and seeing if it even works, refining it is only...step 3 or 4.

And from a user experience standpoint, putting so much features and modes into it become jumper hell to set up, especially if some are clearly inferior and only increase complexity. I basically need to write a manual, and its not ideal.

The plan was to iron out some things, see what is unecessary, what could have been done better etc because there's always something like that you figure out only after building it..

But regarding the best sounding options, it's a bit complex to present myself as authority on what sounds the best, on my system, with my ears, with my music taste etc...but i could certainly make some comments. I wanted to also make measurements and document everything.

Regarding DEM, certainly you could use another one, and there's provisions for smaller SMD caps and such, i thought about it. But honestly i will likely not bother in the end, as the theory of why 50hz was chosen for DEM reclock seems reasonable to me and i dont want to solder and desolder 50 more caps..

I think step one for now is just finishing it and seeing if it even works, refining it is only...step 3 or 4.

Can i get a sanity check?

I've checked it over and cant find the fault.

Basically i got the rest of the caps i needed, and hodgepodged a tl431 to output 3.3v, since i dont have the LDO i should have, and went to test.

Lucky i have all the "breakout" jumpers so i can switch things around for testing.

Dont think its the I/V section, so i dont know...

The "AC" measurements are just RMS by a multimeter, dont have a scope near me right now.

Data lines would go from 0 to about 150mv AC, scaling with volume, but i feel like it should be a bit more.

I also tried the DOR+ * and DOR- * (with the asterisks), indicated as SE on the diagram. And basically every other permutation i could. On some permutations i can get it to have an extremely distorted sound, but nothing more than that.

So just wanted to confirm if this should even work theoretically, before i go hunting for what IC is wrong..any hints?

I've checked it over and cant find the fault.

Basically i got the rest of the caps i needed, and hodgepodged a tl431 to output 3.3v, since i dont have the LDO i should have, and went to test.

Lucky i have all the "breakout" jumpers so i can switch things around for testing.

Dont think its the I/V section, so i dont know...

The "AC" measurements are just RMS by a multimeter, dont have a scope near me right now.

Data lines would go from 0 to about 150mv AC, scaling with volume, but i feel like it should be a bit more.

I also tried the DOR+ * and DOR- * (with the asterisks), indicated as SE on the diagram. And basically every other permutation i could. On some permutations i can get it to have an extremely distorted sound, but nothing more than that.

So just wanted to confirm if this should even work theoretically, before i go hunting for what IC is wrong..any hints?

Last edited:

I would first set TDA in I2S mode, add second channel output and test usb iteface-tda only.

After that connect TS inteface and measure with scope outputs?

Then if it OK reconnect tda for TS mode and check again?

After that connect TS inteface and measure with scope outputs?

Then if it OK reconnect tda for TS mode and check again?

Surely you checked timing or did a functional simulation before you had a pcb made ?So just wanted to confirm if this should even work theoretically,

Thanks Zoran, was thinking this too.I would first set TDA in I2S mode, add second channel output and test usb iteface-tda only.

After that connect TS inteface and measure with scope outputs?

Then if it OK reconnect tda for TS mode and check again?

Okay if schematic doesnt have gross errors (and its fairly simple so...), think i'll do that then.

Embarassing but here is when i cut development time (since i also have a day job), ecdesigns made the signed magnitude logic and a couple of users already verified it works so it should be a messup somewhere on my sideSurely you checked timing or did a functional simulation before you had a pcb made ?

Anyway i order all the time, so no worries, i'll be the sucker. 🙂

The only thing i changed from original post #7092 is made the two circled components separate (lvc1g04 instead of lvc04) for layout reasons, logic-wise they are the same.

I spent a lot of time on the layout, going through 7 iterations until it was elegant.

Are you sure that wasn't the design in post 7057 ?a couple of users already verified it works

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A