Hi Yasioo,I have blank PCBs Dac3_10,Dac3filter_6,

Markw4's clock board pcb,connecting board for I2SoverUSB,pcm2dsd pcb, reclocker board.

Please PM if you want.

Markw4's clock board pcb,connecting board for I2SoverUSB,pcm2dsd pcb, reclocker board.

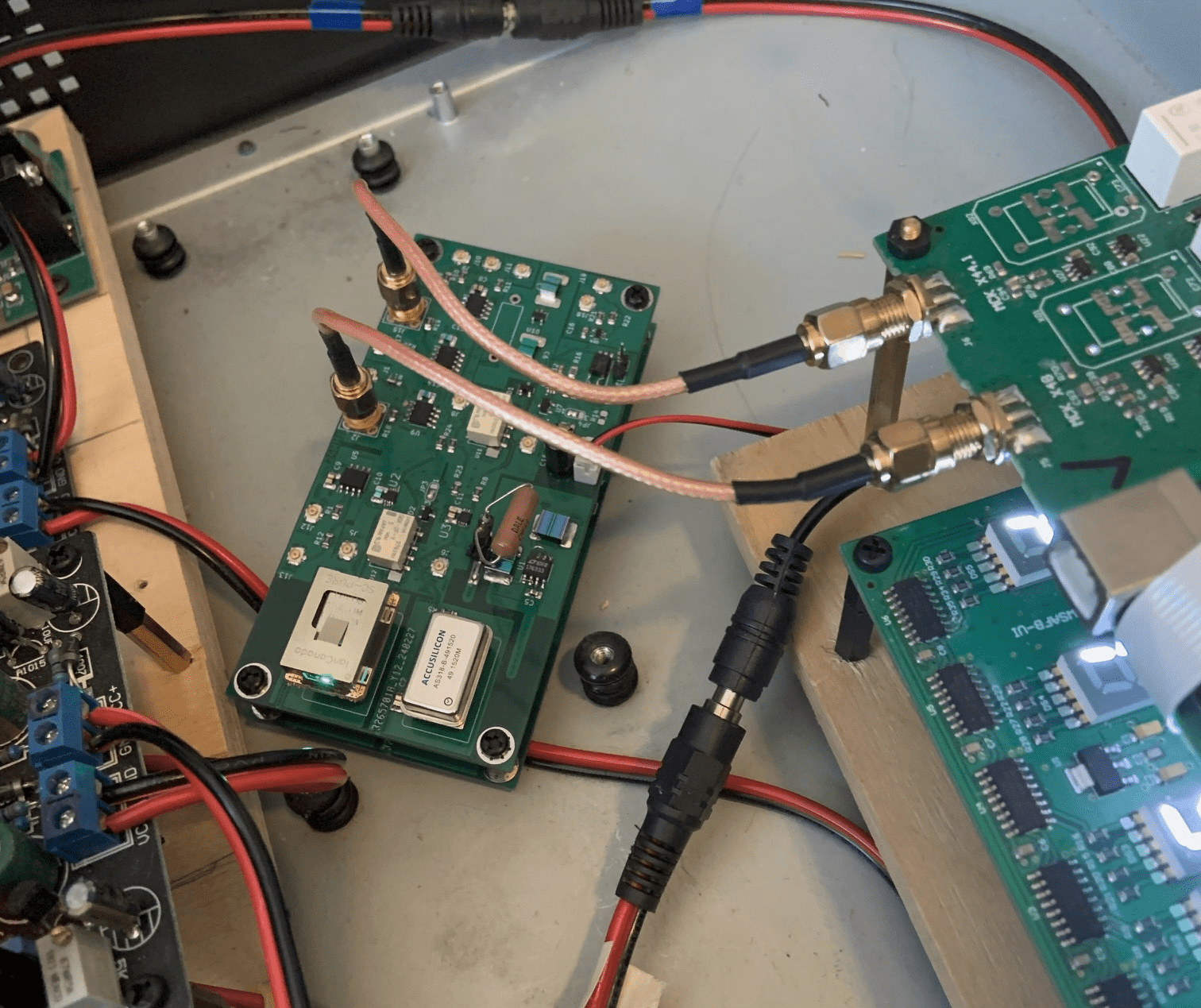

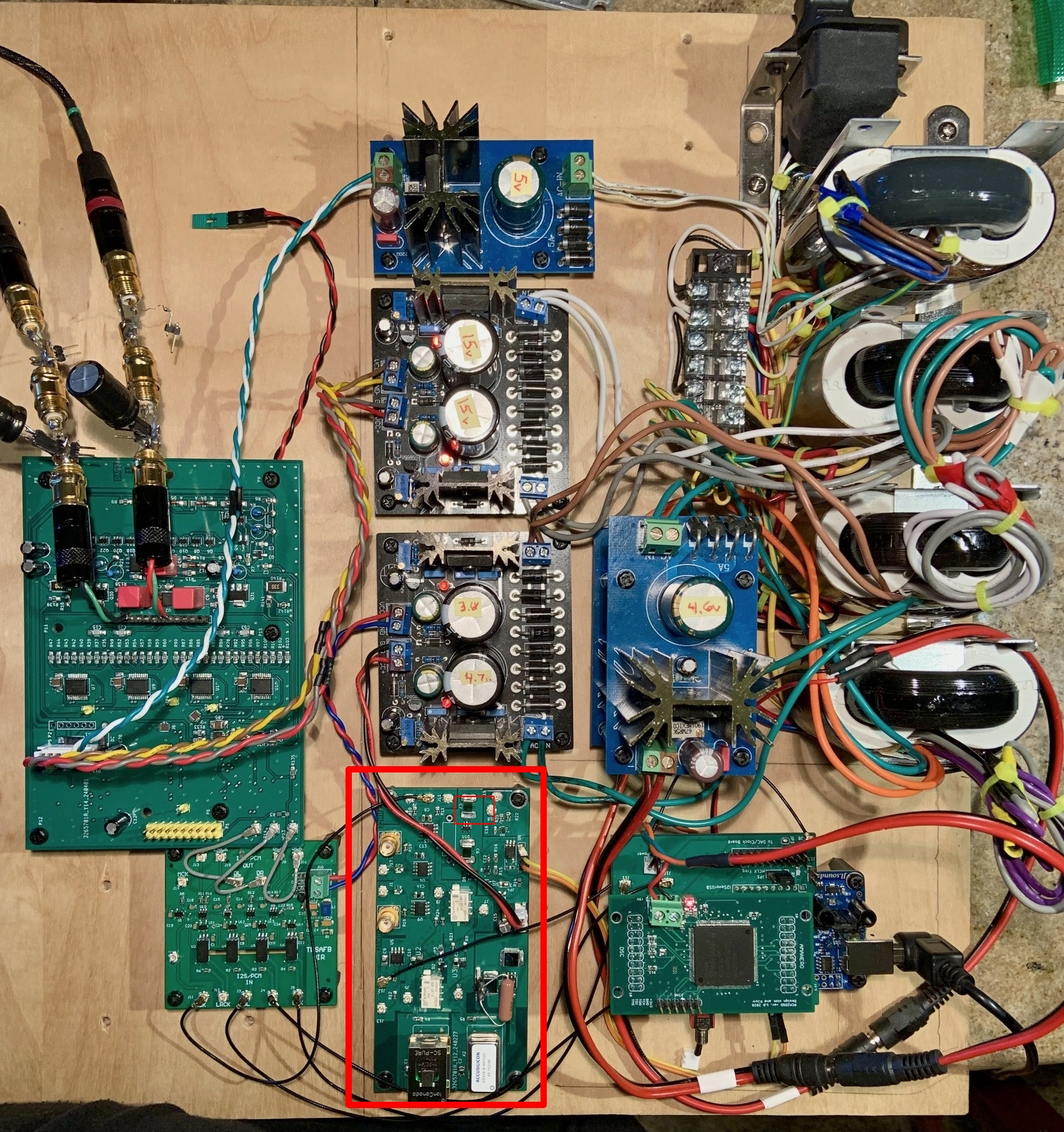

Some pics of a prototype general purpose DAC Clock board, for which I plan to post the Kicad project. First pic is driving a Andrea Mori FIFO Buffer board; second pic is driving a @MarcelvdG RTZ FIRDAC with asynchronous USB, and reclocking before the dac board (clock board prototype is outlined in red).

The original premise was that the clock board would use 45/49MHz clock modules (or external clocks, including sine wave oscillators using suitable squaring adapters). The 45/49MHz frequencies can be used to externally clock an I2SoverUSB board. The clock...

The original premise was that the clock board would use 45/49MHz clock modules (or external clocks, including sine wave oscillators using suitable squaring adapters). The 45/49MHz frequencies can be used to externally clock an I2SoverUSB board. The clock...

- Markw4

- Replies: 423

- Forum: Digital Line Level

I promised a few months ago to try this variantUsing s = j2πf, the comb filter will have notches at f = k/(2T) for all integer k, so exactly at all multiples of half the sample rate. That means that with the Hans variant, at least anything that could mix idle tones around half the sample rate down to audio frequencies would still be suppressed. This is a very interesting feature of the Hans variant, I didn't realize it has this feature until today.

But shortly after, disaster struck because my Picoscope stopped working. That’s why I had to sent it to the UK for repair.Just lifting pins 2 and 3 from one SR and connecting them to pins 12 and 13 from the other SR will do.

Timing of these two signals is not critical, so two short connecting wires will do the job.

Their conclusion was that it was just the USB cable causing the trouble but that the Picoscope still worked fine.

So without any charge for repair it was sent back to Holland and that’s where everything went wrong.

With the UK after their Brexit no longer being part of the EU, on its way back both the English and the Dutch customs were misinformed by UPS and wanted both import and export VAT payments that I refused to pay.

What happened then was a nightmare where nobody within UPS was even able to properly react to or to correct their error, with the consequence that after 3 months sending emails up and down the Picoscope got completely lost.

So a request for a compensating the insured value, resulted in an email from UPS where I was asked whether the scope was despite all odds delivered to my address.

But the most insulting was their mentioning, that if no response was received within 24hours they would consider the case as closed.

Picotech following this all from a distance decided last week to send me a brand-new Picoscope of the same model free of charge.

A fantastic gesture.

Now back to the suggested test to change the 2//2 bit Firdac into a 4 bit Firdac with the simple changes as mentioned above.

My question is, did anyone try this ?

I could accept Marcel’s offer to use his Firdac for this test, but in the meantime several other refinements have been auditioned with positive results.

So, I can perform several measurements, but this will tell little about the effect on sound perception.

Mark, you as having a perfect working Marcel RTZ Firdac, would it be possible for you to lift the required 2 legs from one shift register and connect these legs with two small wire to the legs of the other shift register and see what it does to the sound ?

Hans

Hi Hans,

I would like to keep the RTZ dac system working as it is for now as it is my main reference dac. Don't know when or if I might want to try modifying the dac board itself.

However, I do have a spare bare RTZ dac board I could send to you if you want to populate it with parts and experiment with it there where you are. Actually, I could send you a whole set of bare boards including those I designed and a PCM2DSD board. Or, it also looks like @Cestrian may be reaching a point of satisfaction with his compact clock/reclocker/interconnect board for use with the RTZ dac.

Mark

I would like to keep the RTZ dac system working as it is for now as it is my main reference dac. Don't know when or if I might want to try modifying the dac board itself.

However, I do have a spare bare RTZ dac board I could send to you if you want to populate it with parts and experiment with it there where you are. Actually, I could send you a whole set of bare boards including those I designed and a PCM2DSD board. Or, it also looks like @Cestrian may be reaching a point of satisfaction with his compact clock/reclocker/interconnect board for use with the RTZ dac.

Mark

Last edited:

Hi Mark,

Thx for your very nice proposal but it’s like a ratio between changing a pair of bulbs in the headlights to building a whole car.

For the time being that’s a bit outside my preference for just the purpose of doing a test.

It would be easier to buy a ticket and visit your place.😆

Hans

Thx for your very nice proposal but it’s like a ratio between changing a pair of bulbs in the headlights to building a whole car.

For the time being that’s a bit outside my preference for just the purpose of doing a test.

It would be easier to buy a ticket and visit your place.😆

Hans

Again attemping to put all the information in one post, so I can easily link to it from post #1:

Attached is the .bit file and source code that puts two of my PWM8 modulators and a two-channel FIR filter in an XC6SLX9-2TQG144C (or XC6SLX9-2TQG144I, if you want it to keep working when it is freezing cold). I have gone to speed grade 2, because faster was apparently not needed and speed grade 2 is also what is used in PJotr25's and olo111's simple DSD modulator for DSC2 (a.k.a. PCM2DSD). I also managed to squeeze in an extra filter for filtering and remodulating DSD input signals. The input violates the I2S hold time specification by 0.8 ns, but that is not likely to cause any problems.

It is version 1.4, which features a switchable dither order for all three (re-)quantizers (rounding stages) in the design. According to dither theory, the first n moments of the quantization error can be made independent of the signal by adding n uniformly distributed random signals of 1 LSB peak-peak (1 LSB after requantization, that is) to the signal before rounding. n defaults to 2, but you can make it 1, 3 or 4 by grounding the correct input pins.

The idea behind the modulator is explained in https://linearaudio.net/sites/linearaudio.net/files/03 Didden LA V13 mvdg.pdf pages 32...34 (pdf pages 10...12). It's a quasi-multibit modulator of which the quantizer is dithered according to dither theory, which eliminates the frequency-modulated idle tones around half the sample rate that you have with straightforward single-bit modulators and also their intermodulation products that can otherwise end up in the audio band. You pay for that with less effective noise shaping, hence it has to work at a high bit rate. The FIR interpolation filter output is also rounded with dither (and only rounded to 35 bit word length).

For PCM, the interpolation chain consists of an 8 times interpolating FIR filter that can be set to steep or apodizing, a zero-order hold and the fifth-order low-pass signal transfer function of the sigma-delta modulator. For remodulated DSD, a 15-tap FIR filter with triangular impulse response, zero-order hold and the fifth-order low-pass signal transfer function of the sigma-delta modulator.

The .zip also contains FIR filter impulse and frequency response plots. The horizontal axis is in samples after 8 times interpolation for the impulse responses. For the frequency responses, 0.125 on the horizontal scale corresponds to the input sample rate, the vertical scale is in dB. The zero-order hold and sigma-delta signal transfer function are not included.

The design is supposed to be completely compatible with PCM2DSD, but the output is at a DSD512 rate, so reclocking with the 22.5792 MHz or 24.576 MHz is not going to work, not without double edge clocking anyway. Using the master clock as the bit clock for the DAC should work, though.

There are a couple of conditions:

-It is designed to support PCM sample rates from 8 kHz up to and including 192 kHz and DSD from DSD64 up to and including DSD512 (both 44.1 kHz- and 48 kHz-based). That is, there is no support for 384 kHz PCM.

-The input accepts word lengths up to 32 bit.

-When playing PCM, the master clock must be an exact multiple of 64 times the sample rate, as it usually always is

-The master clock must be in the range from 19 MHz to 25 MHz, the normal values are 22.5792 MHz and 24.576 MHz.

Several pins that are open on the PCM2DSD board can be made high or low to activate extra functions. They have internal pull-ups and pull-downs, so when you leave them open, everything works normally.

"ndithord1" on pin 1, "ndithord3" on pin 41, "ndithord4" on pin 27: internally pulled high, making one and only one of these low changes the dither order n from 2 to 1, 3 or 4, respectively.

"mute" on pin 137: internally pulled low, high level mutes the sigma-delta modulator

"scale[1]" on pin 117: internally pulled low, high level makes sigma-delta input 12 dB more sensitive, can be useful as a debug function to check the effect of overload

"scale[0]" on pin 119: internally pulled high, low level attenuates the signal by 6 dB so you have 6 dB extra headroom for intersample overs

"notSevenofNine" on pin 9: internally pulled high, low level allows only 7 out of the 9 quantization levels

"rot" on pin 7: internally pulled high, low level stops the random rotation function

Making pins 7 and 9 low could be useful for a NRZ FIRDAC of a multiple of eight taps long, like the DSC2.5.2. You then get a normal noise-shaped PWM signal that always has at least one one and at least one zero in each eight clock cycles. The average density of low-to-high and high-to-low transitions then becomes signal-independent. The disadvantage is that you get tones around 1/8 of the master clock rate and its multiples.

Making notSevenofNine low also has the disadvantage that it much reduces the headroom for intersample overshoots. It might even be insufficient at 0 dBFS when the dither order is high. It could therefore be useful to try rot = 0 while leaving notSevenofNine open, when you use a DSC2.5.2.

"notapodizing" on pin 141: internally pulled high, making it low changes the interpolation filter into an apodizing filter (smoother roll-off, shorter impulse response).

"dsdviasd" on pin 139: internally pulled high. When high, a DSD input signal gets filtered and remodulated, when low, a DSD input signal is only resynchronized to the master clock and forwarded to the output (transparent mode).

There is also one extra output:

"iclip" at pin 115: output that goes high for a bit less than a second after an integrator clips. It indicates that an intersample overshoot is larger than the modulator can handle, so you could make scale[0] low to solve that.

Attached is the .bit file and source code that puts two of my PWM8 modulators and a two-channel FIR filter in an XC6SLX9-2TQG144C (or XC6SLX9-2TQG144I, if you want it to keep working when it is freezing cold). I have gone to speed grade 2, because faster was apparently not needed and speed grade 2 is also what is used in PJotr25's and olo111's simple DSD modulator for DSC2 (a.k.a. PCM2DSD). I also managed to squeeze in an extra filter for filtering and remodulating DSD input signals. The input violates the I2S hold time specification by 0.8 ns, but that is not likely to cause any problems.

It is version 1.4, which features a switchable dither order for all three (re-)quantizers (rounding stages) in the design. According to dither theory, the first n moments of the quantization error can be made independent of the signal by adding n uniformly distributed random signals of 1 LSB peak-peak (1 LSB after requantization, that is) to the signal before rounding. n defaults to 2, but you can make it 1, 3 or 4 by grounding the correct input pins.

The idea behind the modulator is explained in https://linearaudio.net/sites/linearaudio.net/files/03 Didden LA V13 mvdg.pdf pages 32...34 (pdf pages 10...12). It's a quasi-multibit modulator of which the quantizer is dithered according to dither theory, which eliminates the frequency-modulated idle tones around half the sample rate that you have with straightforward single-bit modulators and also their intermodulation products that can otherwise end up in the audio band. You pay for that with less effective noise shaping, hence it has to work at a high bit rate. The FIR interpolation filter output is also rounded with dither (and only rounded to 35 bit word length).

For PCM, the interpolation chain consists of an 8 times interpolating FIR filter that can be set to steep or apodizing, a zero-order hold and the fifth-order low-pass signal transfer function of the sigma-delta modulator. For remodulated DSD, a 15-tap FIR filter with triangular impulse response, zero-order hold and the fifth-order low-pass signal transfer function of the sigma-delta modulator.

The .zip also contains FIR filter impulse and frequency response plots. The horizontal axis is in samples after 8 times interpolation for the impulse responses. For the frequency responses, 0.125 on the horizontal scale corresponds to the input sample rate, the vertical scale is in dB. The zero-order hold and sigma-delta signal transfer function are not included.

The design is supposed to be completely compatible with PCM2DSD, but the output is at a DSD512 rate, so reclocking with the 22.5792 MHz or 24.576 MHz is not going to work, not without double edge clocking anyway. Using the master clock as the bit clock for the DAC should work, though.

There are a couple of conditions:

-It is designed to support PCM sample rates from 8 kHz up to and including 192 kHz and DSD from DSD64 up to and including DSD512 (both 44.1 kHz- and 48 kHz-based). That is, there is no support for 384 kHz PCM.

-The input accepts word lengths up to 32 bit.

-When playing PCM, the master clock must be an exact multiple of 64 times the sample rate, as it usually always is

-The master clock must be in the range from 19 MHz to 25 MHz, the normal values are 22.5792 MHz and 24.576 MHz.

Several pins that are open on the PCM2DSD board can be made high or low to activate extra functions. They have internal pull-ups and pull-downs, so when you leave them open, everything works normally.

"ndithord1" on pin 1, "ndithord3" on pin 41, "ndithord4" on pin 27: internally pulled high, making one and only one of these low changes the dither order n from 2 to 1, 3 or 4, respectively.

"mute" on pin 137: internally pulled low, high level mutes the sigma-delta modulator

"scale[1]" on pin 117: internally pulled low, high level makes sigma-delta input 12 dB more sensitive, can be useful as a debug function to check the effect of overload

"scale[0]" on pin 119: internally pulled high, low level attenuates the signal by 6 dB so you have 6 dB extra headroom for intersample overs

"notSevenofNine" on pin 9: internally pulled high, low level allows only 7 out of the 9 quantization levels

"rot" on pin 7: internally pulled high, low level stops the random rotation function

Making pins 7 and 9 low could be useful for a NRZ FIRDAC of a multiple of eight taps long, like the DSC2.5.2. You then get a normal noise-shaped PWM signal that always has at least one one and at least one zero in each eight clock cycles. The average density of low-to-high and high-to-low transitions then becomes signal-independent. The disadvantage is that you get tones around 1/8 of the master clock rate and its multiples.

Making notSevenofNine low also has the disadvantage that it much reduces the headroom for intersample overshoots. It might even be insufficient at 0 dBFS when the dither order is high. It could therefore be useful to try rot = 0 while leaving notSevenofNine open, when you use a DSC2.5.2.

"notapodizing" on pin 141: internally pulled high, making it low changes the interpolation filter into an apodizing filter (smoother roll-off, shorter impulse response).

"dsdviasd" on pin 139: internally pulled high. When high, a DSD input signal gets filtered and remodulated, when low, a DSD input signal is only resynchronized to the master clock and forwarded to the output (transparent mode).

There is also one extra output:

"iclip" at pin 115: output that goes high for a bit less than a second after an integrator clips. It indicates that an intersample overshoot is larger than the modulator can handle, so you could make scale[0] low to solve that.

Attachments

Last edited:

In a loose sense, the higher the dither setting, the less signal-dependent the quantization noise becomes, but the more independent noise is added to the signal. n = 2 is usually assumed to be the best setting for audio.

In an earlier blind listening test on this forum, the two test persons could hear a difference between a file with second-order dither and coarse quantization and a file with additive noise with a similar probability distribution, but they had no preference, which seems to indicate that n = 2 is enough. The quantizer was not embedded in a noise-shaping loop, however, and people may have different preferences - and the quantization noise was much louder than it normally is to make it more audible.

I skipped point 2 from post #3660 because of Mark's reply in post #3661.

In an earlier blind listening test on this forum, the two test persons could hear a difference between a file with second-order dither and coarse quantization and a file with additive noise with a similar probability distribution, but they had no preference, which seems to indicate that n = 2 is enough. The quantizer was not embedded in a noise-shaping loop, however, and people may have different preferences - and the quantization noise was much louder than it normally is to make it more audible.

I skipped point 2 from post #3660 because of Mark's reply in post #3661.

Wow Marcel, what an incredible achievement.

Looking forward to read what the hearing tests will bring this time.

Hans

Looking forward to read what the hearing tests will bring this time.

Hans

Marcel,

When does the FPGA read the dither bits pins? At power on? Between songs? Instantaneously?

When does the FPGA read the dither bits pins? At power on? Between songs? Instantaneously?

Okay. Assuming I loaded the FPGA properly, I don't really hear any significant difference between 2-bits of dither and 4-bits. The sound is still what some people complain about DSD, which is that it sounds "soft." Also, it still sounds blurred together about the same as before. I think your first change to the dither, to keep the dither independent for each channel probably helped some.

Anyway, there are multiple changes going on here. The dac is being operated at twice the clock frequency, and MCLK is being used for BLCK. That's a hardware set of conditions I'm not quite sure how to take into account.

Regarding the dac sound that can be attributed to the FPGA code, at this point I guess most of the blurring/softness is not a function of dither. So maybe its something else. Maybe its time to try your filter idea to see if that changes anything?

Anyway, there are multiple changes going on here. The dac is being operated at twice the clock frequency, and MCLK is being used for BLCK. That's a hardware set of conditions I'm not quite sure how to take into account.

Regarding the dac sound that can be attributed to the FPGA code, at this point I guess most of the blurring/softness is not a function of dither. So maybe its something else. Maybe its time to try your filter idea to see if that changes anything?

For HQ Player the filters than give maybe the best spatial cues are the gaussian ones.

Could you measure a few points of the frequency response of your favourite filter? It's particularly the transition band that matters.

I assume it must be some sort of Gaussian tapered sinc rather than a "real" Gaussian filter, as its roll-off would otherwise be much too slow. The trick is to find out how wide the Gaussian taper must be.

I still don't know if its the spatial cues. There is something like noise, but it must not be dither related. The sound is soft and blurred together. Maybe they are two ways of describing the same perceptual effect, don't know. Low level information is getting lost in what sounds like a fog of noise. Thus, I don't know what about a filter could cause such an effect? My experience with filters that I can select in a dac is that they do to some extent affect phase and maybe noise in the passband. Usually its the linear phase filters that sound best to me, and usually they are the dac default filters.

Anyway, my feeling is that we need to see if we can get its attention, even if we overshoot. The first thing is just to find some change that affects low level detail. Then maybe fine tune it. Sort of some perturbation probing of the system in a search for low level detail control levers.

EDIT: Another random thought, could noise be getting into phase?

Anyway, my feeling is that we need to see if we can get its attention, even if we overshoot. The first thing is just to find some change that affects low level detail. Then maybe fine tune it. Sort of some perturbation probing of the system in a search for low level detail control levers.

EDIT: Another random thought, could noise be getting into phase?

Last edited:

The FIR filter coefficient sets are both linear phase, as otherwise they didn't fit in the FPGA. Normally I would have chosen an apodizing filter that is only approximately linear phase over its passband, but now it had to be completely linear phase.

The zero-order hold is also linear phase.

The sigma-delta signal transfer function is not, instead it is minimum phase. Fifth-order Butterworth at about 210 kHz, if I remember well.

The FIRDAC core is linear phase.

The analogue reconstruction filter is not. Mine is minimum phase (in fact fourth-order Butterworth at 80 kHz), I guess yours is also minimum phase.

The zero-order hold is also linear phase.

The sigma-delta signal transfer function is not, instead it is minimum phase. Fifth-order Butterworth at about 210 kHz, if I remember well.

The FIRDAC core is linear phase.

The analogue reconstruction filter is not. Mine is minimum phase (in fact fourth-order Butterworth at 80 kHz), I guess yours is also minimum phase.

It occurs to me I could do a test with your FPGA code. I could set it to bypass DSD, then send it DSD512 from HQ player (I forget if you support that at the moment). That should show if changing the hardware configuration to support DSD512 and or clocking the dac faster has any adverse effect on perceived SQ.

Maybe possible to do the same with PCM2SDSD removed from the system, but then I would have to do something to make the existing wiring work. Maybe make a dummy PCM2DSD board to plug in and bypass FPGA processing.

Maybe possible to do the same with PCM2SDSD removed from the system, but then I would have to do something to make the existing wiring work. Maybe make a dummy PCM2DSD board to plug in and bypass FPGA processing.

As for HQPlayer, I have no additional information. But the description of many filters can be found:Maybe @PJotr25 would know what they are using?

https://www.northernaudio.com/hqplayer-offers-unrivaled-sound/

It occurs to me I could do a test with your FPGA code. I could set it to bypass DSD, then send it DSD512 from HQ player (I forget if you support that at the moment).

Yes, see post #3685. You have to make "dsdviasd" on pin 139 low, otherwise it filters and remodulates rather than bypasses. The filter used when pin 139 is open or driven high is a 15-tap FIR with triangular weights. Mind you, no one tested this function yet.

Hi All

Yet another FIRdac came to live in Denmark 😀.

I tried it with a Sowter transformer as filter/output but with less than stellar performance (as Markw4 already had anticipated) so I need a filter PCB for the DAC.

Does anybody have a spare filterpcb, preferably the one Nautibuoy made, that I can buy?

I made some measurements of the actual current consumption of the different parts of the DAC.

With 1 Khz 0dB sine, each of the shift register DAC´s use ca. 5 mA (measured over R16 and R141) and the clock doubler uses 7 mA (measured over R14).

These are the voltages that needs to be very quiet and clean.

I would guess, that if the supply only consists of a capacitor(no active feedback PS in sight, with potential noise, overshoot and instability) it would be the cleanest of all solutions??

So a supåercapacitor (actually 2 2,7V in series) for each of these points, that is charged by a 5A supply for the two DAC´s and 7A for the Clock Doubler whenever the mute relay is active would do the job.

1 second of charging will give around 15 min of playing time and ( if two 360F capacitors are used) about 6 hours of non-stop playing time , before charging is necessary and then only about 30 sec charging is necessary. I haven't yet measured the last 5V supply, but if this also is replaced by a Supercapacitor, one could avoid all 230V ac coming in to the FIRDAC while playing and all the chargers could be cheap 230V ac to 5V DC smps.

Any comments to this? I know it is kind of heresy to skip Marcell`s very clever band gab reference power supply..

Karsten

Yet another FIRdac came to live in Denmark 😀.

I tried it with a Sowter transformer as filter/output but with less than stellar performance (as Markw4 already had anticipated) so I need a filter PCB for the DAC.

Does anybody have a spare filterpcb, preferably the one Nautibuoy made, that I can buy?

I made some measurements of the actual current consumption of the different parts of the DAC.

With 1 Khz 0dB sine, each of the shift register DAC´s use ca. 5 mA (measured over R16 and R141) and the clock doubler uses 7 mA (measured over R14).

These are the voltages that needs to be very quiet and clean.

I would guess, that if the supply only consists of a capacitor(no active feedback PS in sight, with potential noise, overshoot and instability) it would be the cleanest of all solutions??

So a supåercapacitor (actually 2 2,7V in series) for each of these points, that is charged by a 5A supply for the two DAC´s and 7A for the Clock Doubler whenever the mute relay is active would do the job.

1 second of charging will give around 15 min of playing time and ( if two 360F capacitors are used) about 6 hours of non-stop playing time , before charging is necessary and then only about 30 sec charging is necessary. I haven't yet measured the last 5V supply, but if this also is replaced by a Supercapacitor, one could avoid all 230V ac coming in to the FIRDAC while playing and all the chargers could be cheap 230V ac to 5V DC smps.

Any comments to this? I know it is kind of heresy to skip Marcell`s very clever band gab reference power supply..

Karsten

As for HQPlayer, I have no additional information. But the description of many filters can be found:

https://www.northernaudio.com/hqplayer-offers-unrivaled-sound/

Interesting that they write: "Non-apodizing filters are good for HiRes recordings (88.2/96kHz and above) because the Nyquist rate is very high. Apodizing filters are most important for Reedbook/CD formats (44.1/48kHz) because of the low Nyquist rate."

Peter Craven, who introduced the whole idea of apodizing filters in audio, wrote the opposite. His apodizing filters are specifically meant for high sample rates. Their main purpose is to make the overall impulse response short, suppression of aliases or images that are inadequately suppressed by half-band filters elsewhere in the signal chain is a nice side-effect.

Last edited:

I will check, I have a huge pile of JLC boxes now.Does anybody have a spare filterpcb, preferably the one Nautibuoy made, that I can buy?

I also might have a built one. Let me check...

(some time later)

Yes, I have actually two built ones. One has opa1678 fitted to last stage and the other one opa2210. In which case I must also have bare pcbs left since min order was 5.

DM if interested.

Last edited:

- Home

- Source & Line

- Digital Line Level

- Return-to-zero shift register FIRDAC