I have question for you, have you tested DSD in your system without PCM2DSD, eg. from HQPlayer?

Does Mute work well?

Does Mute work well?

sure 🙂

my current DSD chain is proven and tested for almost 2 years now.

hqp in DSD (SDM) works perfectly.

And McFIFO muting works great. The mute condition is detected correctly because the source stops the dataflow when music is stoppe/paused/changed.

i don't use an Amanero, but rather a network streamer from pavel (ppy here on diya). He called "PURE" streamer. (www.puredsd.ru) as said few posts ago).

The source is Based on a beaglebone black with custom kernel that is capable of outputs i2s/dsd from gpio.

The output pinout is the same as amanero (to maintain compatibility).

Still, i don't use the MUTE signal from it. I have always used the one from the Fifo.

Indeed the Botic driver on the beaglebone when the track is Stopped... it outputs nothing.

If is possible to implement a way to detect when mute is asserted and STOP the sigmadelta on the output I (and i guess, others) will appreciate that.

Thanks

my current DSD chain is proven and tested for almost 2 years now.

hqp in DSD (SDM) works perfectly.

And McFIFO muting works great. The mute condition is detected correctly because the source stops the dataflow when music is stoppe/paused/changed.

i don't use an Amanero, but rather a network streamer from pavel (ppy here on diya). He called "PURE" streamer. (www.puredsd.ru) as said few posts ago).

The source is Based on a beaglebone black with custom kernel that is capable of outputs i2s/dsd from gpio.

The output pinout is the same as amanero (to maintain compatibility).

Still, i don't use the MUTE signal from it. I have always used the one from the Fifo.

Indeed the Botic driver on the beaglebone when the track is Stopped... it outputs nothing.

If is possible to implement a way to detect when mute is asserted and STOP the sigmadelta on the output I (and i guess, others) will appreciate that.

Thanks

Last edited:

No problem.

thanks anyway.

I will try re-route the signal "externally" from the fifo or maybe gate the signals just after the converter.

thanks anyway.

I will try re-route the signal "externally" from the fifo or maybe gate the signals just after the converter.

Sure it works... No doubt.

I was just asking about a possible adaptation/modification to the firmware to better suit a different use case scenario...

That's all... 🙂

I was just asking about a possible adaptation/modification to the firmware to better suit a different use case scenario...

That's all... 🙂

Last edited:

Sure it works... No doubt.

I was just asking about a possible adaptation/modification to the firmware to better suit a different use case scenario...

That's all... 🙂

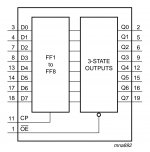

You can the try 74AHCT374 hardware at behind side of PCM2DSD with Pin11 for MCLK, and Pin-1 for Mute.

Attachments

Last edited:

sure 🙂

If is possible to implement a way to detect when mute is asserted and STOP the sigmadelta on the output I (and i guess, others) will appreciate that.

Thanks

I don't have a complete understanding of what your mute system does. I guess the mute signal from FIFO detects the signal itself, not zero, because zero in DSM doesn't have a concrete value, which depends on the modulator(if PCM, zero is always 0). The absence of pulse train on the PCM2DSD output(clock,dalaL, and dataR) is probably the trigger of the mute. The best way is to connect the mute pin to eeprom5pin or 6pin with a jumper wire to signal the mute is on to FPGA. The second is to detect zero of PCM. It's easy to detect zero of PCM, but I don't know the delay between zero of PCM and the mute signal. A trial and error are necessary.

Reply to post 88: the outputs will float during mute, which you can fix with pull-down resistors. An inverter and two or three AND gates (and no '374) should also work, assuming a high level at MUTE means the signal has to be muted and assuming the mute signal doesn't need to be stretched.

Last edited:

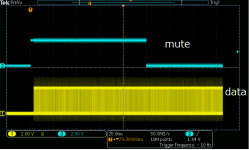

The mute of my amanero clone doesn't make sense(pic.1).😕 It outputs 100milisec high when the output has data. But it does nothing(staying low) when the output becomes zero. You can't use it as "mute." The only way to have a successful mute is to detect PCM zero with FPGA logic and stop pulse train.

Attachments

This works when you need to mute to avoid pops due to DAC clock changes. It basically assumes that the DAC will be able to switch clocks and start outputting valid signal within 100 msec of detecting data. It's crude but it's generic. Of course, putting a FIFO in between means you need to extend that 100ms even more.

I moved the logic one level back to the OS - I have ALSA hooks that tell me when something is opening and closing the PCM device and I mute/unmute with some delay logic based on that. Doesn't work on Windows but I don't care 🙂

I moved the logic one level back to the OS - I have ALSA hooks that tell me when something is opening and closing the PCM device and I mute/unmute with some delay logic based on that. Doesn't work on Windows but I don't care 🙂

This works when you need to mute to avoid pops due to DAC clock changes. It basically assumes that the DAC will be able to switch clocks and start outputting valid signal within 100 msec of detecting data. It's crude but it's generic. Of course, putting a FIFO in between means you need to extend that 100ms even more.

I moved the logic one level back to the OS - I have ALSA hooks that tell me when something is opening and closing the PCM device and I mute/unmute with some delay logic based on that. Doesn't work on Windows but I don't care 🙂

unless you pipe the mute in the fifo itself, if the fifo has more channel than the ones needed for just the audio signal (like a McFifo does) you can channel the mute into the buffer, then it became "good enough" again.

But the behaviour of the mute signal is wrong on that picture.

Amanero have to pull the mute low when music is playing and goes back to high when stops/changes ecc...

The mute of my amanero clone doesn't make sense(pic.1).😕 It outputs 100milisec high when the output has data. But it does nothing(staying low) when the output becomes zero. You can't use it as "mute." The only way to have a successful mute is to detect PCM zero with FPGA logic and stop pulse train.

what is "DATA" ?

DSD_CLK ?

DSD1 ?

DSD2 ?

what is "DATA" ?

DSD_CLK ?

DSD1 ?

DSD2 ?

DATA means Amanero-5pin. 7pin,9pin, and 11pin are always on. FPGA still has 10milisec delay memory even in 192kHz. No DSM pulse train(mute) when no data exists(zero), and regular operation when data exists are possible with some delay like Amanero's mute(4milisec delay). In other words, continuous 4milisec zero triggers no DSM pulse train(signaling mute to FIFO). This is my scenario. Is it OK?

The mute of my amanero clone doesn't make sense(pic.1).😕 It outputs 100milisec high when the output has data. But it does nothing(staying low) when the output becomes zero. You can't use it as "mute." The only way to have a successful mute is to detect PCM zero with FPGA logic and stop pulse train.

also the clock is not shutting down ?

I see the Pin3-4-5 of Amanero alway = H when only Amanero are plugged in to PC, or HQ Player are stoped/paused too. May be it pullup to Vcc !?

I'm using CPLD_1081 and firmware_2006be11 on Windows 10.

I'm using CPLD_1081 and firmware_2006be11 on Windows 10.

Last edited:

I see the Pin3-4-5 of Amanero alway = H when only Amanero are plugged in to PC, or HQ Player are stoped/paused too. May be it pullup to Vcc !?

I'm using CPLD_1081 and firmware_2006be11 on Windows 10.

that's what is indeed right and good.

i have asked a friend of mine that uses amanero, and also him confirmed that MUTE stays HIGH when track is halted/paused/change_fs.

i am doing a gadget like the attached to "FIX" the converter and let it run fine with the McFIFO (not finished...)

Pjotr, can you tell me if the FPGA handles the "DSD_ON" signal at the output ?

i can rely on it or is passed trought like the mute ?

thanks.

Attachments

I'm attached 2 led bulbs: one for Mute leg (pin-11) and one for DSD_En leg (pin-7).

I am sure they work correctly.

When I click the stop/pausing on HQ Player the Mute-led are led-on, and change to led-off while playing.

DSD_On-led are led-on if DSD playing and led-off when PCM playing.

You should use the CPLD_1081 + firmware_2006be11 and try again.

I am sure they work correctly.

When I click the stop/pausing on HQ Player the Mute-led are led-on, and change to led-off while playing.

DSD_On-led are led-on if DSD playing and led-off when PCM playing.

You should use the CPLD_1081 + firmware_2006be11 and try again.

Last edited:

- Home

- Source & Line

- Digital Line Level

- Simple DSD modulator for DSC2