Xc6slx9 version is 256length FIR for 192k, 512length FIR for 96k, 1024length FIR for 48k, and two 5th order DSMs. Xc6slx25 is 1024length FIR for 96k, one 4th order DSM, and one 5th order DSM. Xc6slx9 has only one oversample module because of a small size. That's why xc6slx9 has a half-size FIR with time-multiplexing.

thanks

Today i have soldered and tested succesfully 2 boards.

Electrically speaking they are good to go...

but, because i still miss the serial flash needed to "store" the program i have started experimenting a bit.

I have a a couple of Macronix MX25L3206 (32Mbit) that i have bought for a bios swap on a motherboard.

I have tried anyway, they are pin-per-pin compatible.

from impact i have prepared a prom file with 32M size.

then loaded and selected an N25Q32 from the spi flash selection.

I did that because i found a paper from macronix that state they can be used with that trick.

But when i start the programming, the fpga loaded the firmware (led turned on on the board) but then it said "SPI flash not found".

i was expecting an ID mismatch...

Except i am missing something major... i guess i need to wait for the postman to ring my door 🙂

Thanks nonetheless for the great opportuinity !

I really want to taste how it sounds.

Electrically speaking they are good to go...

but, because i still miss the serial flash needed to "store" the program i have started experimenting a bit.

I have a a couple of Macronix MX25L3206 (32Mbit) that i have bought for a bios swap on a motherboard.

I have tried anyway, they are pin-per-pin compatible.

from impact i have prepared a prom file with 32M size.

then loaded and selected an N25Q32 from the spi flash selection.

I did that because i found a paper from macronix that state they can be used with that trick.

But when i start the programming, the fpga loaded the firmware (led turned on on the board) but then it said "SPI flash not found".

i was expecting an ID mismatch...

Except i am missing something major... i guess i need to wait for the postman to ring my door 🙂

Thanks nonetheless for the great opportuinity !

I really want to taste how it sounds.

I guess there are two possibilities. One is simple but sometimes occurs; cold joint of config-related pins (TCK, TDI, .., CCLK, and DIN). I recommend you examine such pins if soldering is OK. The other is Xilinx cable will not accept your EEPROM even if you specify ignoring chip ID. If so, you may need another EEPROM that Xilinx can recognize.

If you have an EEPROM writer for a BIOS update, you can use it for writing config-EEPROM; desoldering the EEPROM, and writing it with an EEPROM writer. In such a case, an EEPROM writer requires mcs file, not bit. Which way is convenient for you?

If you have an EEPROM writer for a BIOS update, you can use it for writing config-EEPROM; desoldering the EEPROM, and writing it with an EEPROM writer. In such a case, an EEPROM writer requires mcs file, not bit. Which way is convenient for you?

I had more than one problem with the ISE 14.7 on VM (as released by xilinx)... skip_id_check didn't worked.

I found a way to let the 14.7 run on windows 10 x64 baremetal and here i was able to activate the env variable.

In the end i had success.

since the flash is 32Mbit, 4x the recommended 8Mbit in the BOM maybe i can multiboot with the xx3stksm version and the original one. Not sure if it possible... must check 🙂

Board flashed correctly.

Thanks

I found a way to let the 14.7 run on windows 10 x64 baremetal and here i was able to activate the env variable.

In the end i had success.

since the flash is 32Mbit, 4x the recommended 8Mbit in the BOM maybe i can multiboot with the xx3stksm version and the original one. Not sure if it possible... must check 🙂

Board flashed correctly.

Thanks

Good.🙂 But you can't do multiboot from an 8Mb EEPROM because FPGA always reads data from address 0. If you want to multiboot with an SPI EEPROM, some tweak(two EEPROMs) is necessary. You need to reflash if you want to try my file.

Question:

when a track stops what i have to expect at the output of the converter ?

because at the moment when a track stops, it continues to send out data...

when first starts, the outputs are "off".

then as soon as i start a track:

DSD_CLK starts to oscilaltes, and both dsd1/dsd2 has data on them.

but when i stop a track... this don't interrupts.

at the input of the convert i have both mute and i2s stopped.

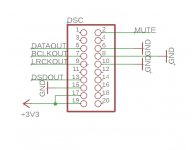

can i have a pinout of the two 2x10 connectors ?

the one labeled "amanero" and the one named "DSC"

thanks

when a track stops what i have to expect at the output of the converter ?

because at the moment when a track stops, it continues to send out data...

when first starts, the outputs are "off".

then as soon as i start a track:

DSD_CLK starts to oscilaltes, and both dsd1/dsd2 has data on them.

but when i stop a track... this don't interrupts.

at the input of the convert i have both mute and i2s stopped.

can i have a pinout of the two 2x10 connectors ?

the one labeled "amanero" and the one named "DSC"

thanks

Last edited:

I see... But a problem i have is that i am using a fifo between the two... The mute signal is no longer taken from the "input" but from the fifo itself that decide few samples before buffer underrun to take action and send the mute.

The fifo in use is the mcFifo of Ian.

I would really appreciate if the data output would be taken down also when mute is asserted at the input...

As you already knew i am not using the pcm2dsd with american and dsc 2.5.2 but instead I am using a beaglebone with bbbrclk (www.puredsd.ru) to supply my dsc sticks.

Do you think can be possible to make such of adjustments ? I don't think is very much... But i know very little of fpgas.

Thanks [emoji4]

The fifo in use is the mcFifo of Ian.

I would really appreciate if the data output would be taken down also when mute is asserted at the input...

As you already knew i am not using the pcm2dsd with american and dsc 2.5.2 but instead I am using a beaglebone with bbbrclk (www.puredsd.ru) to supply my dsc sticks.

Do you think can be possible to make such of adjustments ? I don't think is very much... But i know very little of fpgas.

Thanks [emoji4]

First i want to be sure to ha del the mute correctly.Does it work satisfactorily when playing music?

Dsc family is very sensitive to start/stops of the data flow.

Once sorted out... Surely i will report my findings

If using a fifo that supports dsd along with the pcm2dsd, why not put the fifo on the dsd side, just before the dac? Jitter to the dac should probably be lower that way.

I don't know anything about your FIFO board, but a continuous series of zeros or ones corresponds to a DC offset of two times the maximum peak signal level in DSD, so normally leaving the modulator running with zero input so it generates a bitstream with 50 % ones and 50 % zeros will result in less of a thump than switching off the data output.

If using a fifo that supports dsd along with the pcm2dsd, why not put the fifo on the dsd side, just before the dac? Jitter to the dac should probably be lower that way.

it's already that way. where did you get that i have on the "pcm" side ?

Sorry if i was not clear about it.

at the moment the chain is :

Source(PCM)->PCM_TO_DSD_CONVERTER->LVTTL-TO-LVDS->Hdmi<-LVDS-TO-LVTTL->MCFIFO->DSC

I don't know anything about your FIFO board, but a continuous series of zeros or ones corresponds to a DC offset of two times the maximum peak signal level in DSD, so normally leaving the modulator running with zero input so it generates a bitstream with 50 % ones and 50 % zeros will result in less of a thump than switching off the data output.

The Fifo is not mine 😱 It's made by Ian Canada.

you are 100% right about the half-time strategy strategy, but that leds the fifo don't understand when the stream has stopped.

In my (and if i have to guess, many other) implementation that can be a problem.

In my case, mute must be driven by the Fifo Buffer itself.

There's a delay prior to music actually reach the converters (DSC) because of the fifo length. if the mute is kept "external" from it, then it "opens" the DSC before the music has effectively exit the fifo, and then the "thump" is heard.

the other way aroud (when music stops..) is indeed better, because the mute trigger before the fifo expires.

One way to avoid this is to carry the mute signal on one of the input of the fifo.... so the fifo signal (Hi/Lo state) is buffered as long as the other signals in the fifo... and the "timing" should be restored this way.

In this case, since the McFifo is multichannel, i have many more inputs to spare and then i can use one for muting.

For other people with other kind of fifo systems may not be that easy.

I really prefer to have a modded version of this to better suit my case...

but if the developers are not willing to do so, i totally understand !

Thanks anyway.

PCM2DSD does nothing with the MUTE signal, it just passes this signal from Amanero.

Amanero also has signals all the time in DSD mode.

I don't know how it is in mcFIFO.

Amanero also has signals all the time in DSD mode.

I don't know how it is in mcFIFO.

PCM2DSD does nothing with the MUTE signal, it just passes this signal from Amanero.

Amanero also has signals all the time in DSD mode.

I don't know how it is in mcFIFO.

yes... i know.

i've tried to explain how mcFifo muting works... but evidently i've failed 🙂

mcFifo uses the data left in the buffer to understand if it is time or not to activate/release the mute. it has its own output Mute pin.

if the PCM2DSD output always some data, also when muted, then the fifo buffer never goes towards empty and mute does not works.

Hence my question : Do you think is possible to HALT the sigma delta modulator when MUTE Pin is asserted from amanero ?

Thanks

yes... i know.

Hence my question : Do you think is possible to HALT the sigma delta modulator when MUTE Pin is asserted from amanero ?

It is not possible because the Mute signal does not even go to fpga...

- Home

- Source & Line

- Digital Line Level

- Simple DSD modulator for DSC2