What IO supply voltage do you use for the AD1896? The DAC is only guaranteed to work when the high input level is at least 70 % of its digital supply, 80 % for the clock input.

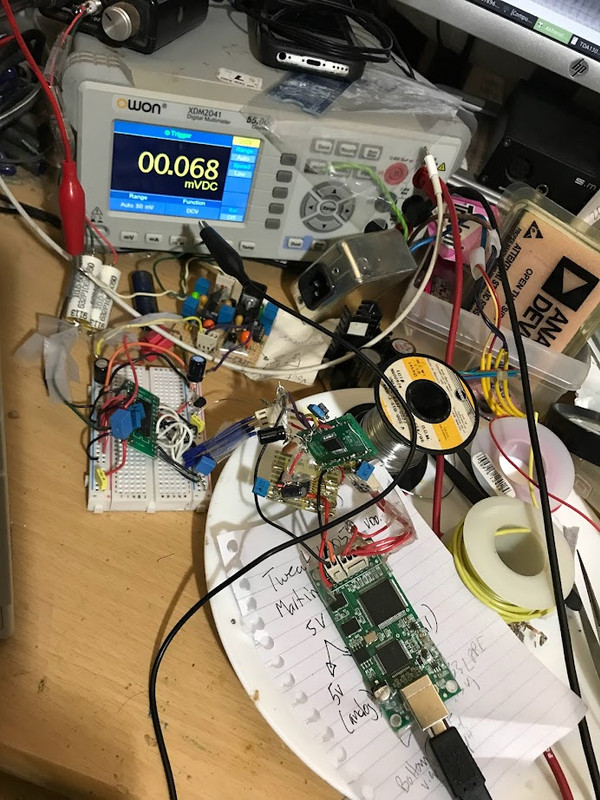

Both the divide-by-two daughterboard (dividing Amanero MCK to 11.289) and the AD1896 (or SRC4192) are supplied 3.3v from the Amanero ( its gpio 3.3v supply lines). This is the easiest way for me to get 3.3v to the AD1896 or SRC4192 need. And then heavily decouple that 3.3v on at various places on the ASRC.

Besides, the long unterminated wires and poor or nonexistent supply decoupling won't help.

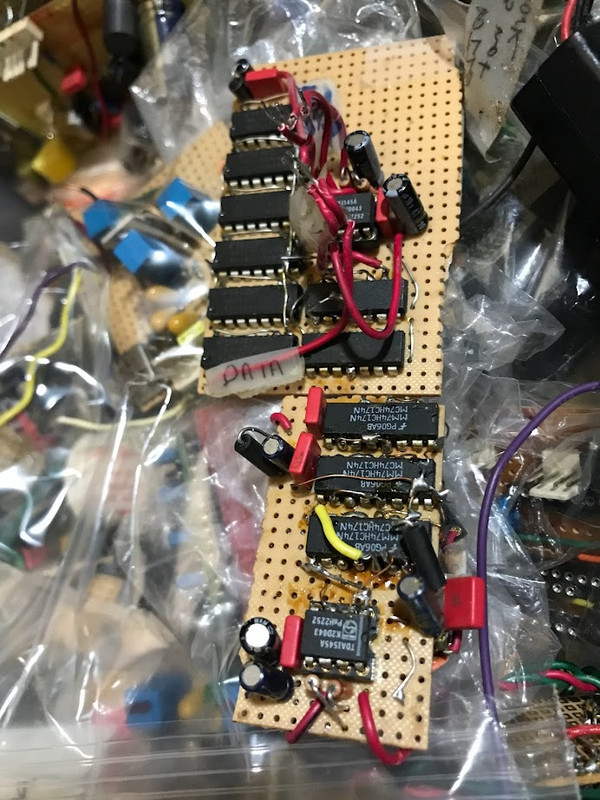

Not sure what you mean by "the long unterminated wires" . Yes, the breadboard connections are not tight. And yes: lots of flying wires. But I am using thick solid core, as short as I can possible manage. The messy, 3D "flying object" arrangement is meant to keep leads short.

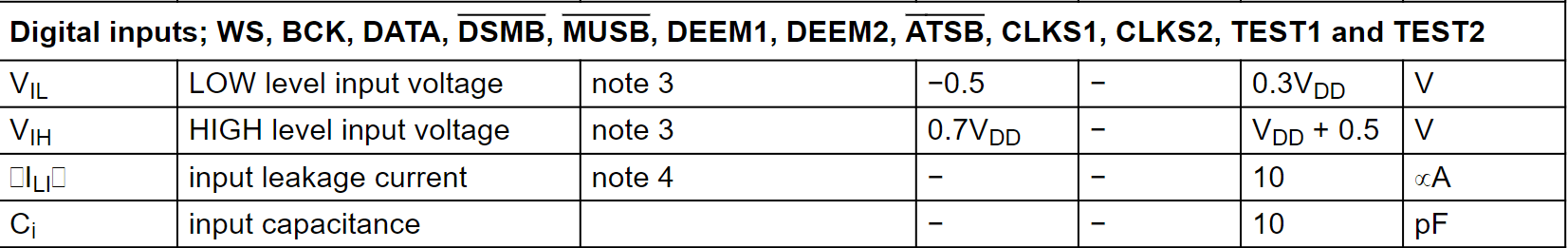

Please check your logic voltage levels - this is what the TDA1305 expects:

I don't think you can expect the DAC @5V to accept the I2S source voltages (incl. the ASRCs) when the're running from 3V3.

I don't think you can expect the DAC @5V to accept the I2S source voltages (incl. the ASRCs) when the're running from 3V3.

Right!Please check your logic voltage levels - this is what the TDA1305 expects:

Amanero out (no /2) ;SRC 4192 (/2)

BCK: 1.64vdc; 1.43

WS: 1.64vdc; 1.43

DATA: ~0.82 ; ~0.88

MCK: 1.64vdc ; 1.33

All above: with with music playing.

The 1305 DS does note V_DD min = 3.4 v. Testing with digital display variable PSU, there is some wiggling room.

The ASRCs are in no way to exceed 3.6 for VDD_CORE, especially the SRC4192.

But too bad the min. specified for V_DD min = 3.4 v. It does work below that. It's only 0.1v to make it the ultra-common 3.3. I do have some fixed VDO at 3.3v. Including some goodies from Linear.

Last edited:

To what end ? One of the benefits offered by the ASRC is the separation of the clock domains. The output clock can be a new clean clock. Operating both sides with the input master clock means any crud derived from the MCLK on the input side is simply added back on the output side.I'm using Amanero(MCLK) 48k -> src4192(RCKI, pin 2) 192k, 4x upsamping.

Amanero MCLK (48k) might be a typo by iitzex. My Amanero MCLK is 22.xx Mhz.To what end ? One of the benefits offered by the ASRC is the separation of the clock domains. The output clock can be a new clean clock. Operating both sides with the input master clock means any crud derived from the MCLK on the input side is simply added back on the output side.

I doubt it is a typo, presumably MCLK is a multiple of Fs where FS is 48kHz, and you may well be missing the point.

I've tried to keep the messy ASRC experiment as all-things-kept-equal as possible. The contenders: a now-highly-modded Chinese dual (parallel) TDA1305 kit vs. the ASRC mess you've seen in my photos.

But with even in the mess with the SRC4192, the inferior of the two ASRCs tried thus far, I keep preferring the ASRC mess. Sounds cleaner and more dynamic. Maybe the superior Amanero has something to do with it ???

About the " logic voltage levels" issue ... The 1305 runs just fine even down to 2.7vdc (I am feeding both analog and digital V pins with the same Tekpower supply -- not ideal, but that's just breadboard convenience ). I'd still like 5v (nominal) on all the 1305's +V pins I can get away with. (I assume the logic voltage level limits are for the 1305's V_DDD digital supply voltage only). In other words ... keep V_DDD digital supply voltage (pin 10) at 3.3v; but, supply independent 5.0v to V_DDA analog supply voltage (pin 1) and V_DDO operational amplifier supply voltage (pin 28). Yes?

Bottom line: The ASRC seems to work some mystical stuff. Not sure how or why. Maybe keeping the MCLK out of that tiny SSOP device, where I2S signals are travelling molecules apart, is part of the dreamy magic.

But with even in the mess with the SRC4192, the inferior of the two ASRCs tried thus far, I keep preferring the ASRC mess. Sounds cleaner and more dynamic. Maybe the superior Amanero has something to do with it ???

About the " logic voltage levels" issue ... The 1305 runs just fine even down to 2.7vdc (I am feeding both analog and digital V pins with the same Tekpower supply -- not ideal, but that's just breadboard convenience ). I'd still like 5v (nominal) on all the 1305's +V pins I can get away with. (I assume the logic voltage level limits are for the 1305's V_DDD digital supply voltage only). In other words ... keep V_DDD digital supply voltage (pin 10) at 3.3v; but, supply independent 5.0v to V_DDA analog supply voltage (pin 1) and V_DDO operational amplifier supply voltage (pin 28). Yes?

Bottom line: The ASRC seems to work some mystical stuff. Not sure how or why. Maybe keeping the MCLK out of that tiny SSOP device, where I2S signals are travelling molecules apart, is part of the dreamy magic.

Sorry for my wrong expression.To what end ? One of the benefits offered by the ASRC is the separation of the clock domains. The output clock can be a new clean clock. Operating both sides with the input master clock means any crud derived from the MCLK on the input side is simply added back on the output side.

Audio source from Amanero maybe 44.1/48khz, then MCLK will set to 22.5792/24.576mhz for each.

SRC4192 was used to upsample 4x the source 44.1/48k -> 176.4/192k.

You are right, and crud may pass to the output side.

But is it better than a YSF210B or a CXD1144/CXD1244 nevermind a PMD100 or a custom solution ? I have a dac with one of these things in it and all it seems to do is smear itself over all that passes through it at the same as forcing the different sample rates of my many files into the same bland mess. Fortunately it can be switched out.Just as an oversampling filter?

No idea, I don't know any of those chips. If you want an as high as possible performance hardware oversampling filter, you can probably best use an FPGA and configure it to behave as a long interpolating FIR filter with no intermediate roundings and with one dithered rounding stage at the output, with protection against overflow and with some headroom for intersample overshoots.

For what it's worth, I have an SRC4392 in my DAC converting everything to 200 kHz sample rate and it doesn't sound like a mess to me. I apply some preprocessing before putting the signal through the SRC4392 and I have switched off the SRC4392's decimation filter.

For what it's worth, I have an SRC4392 in my DAC converting everything to 200 kHz sample rate and it doesn't sound like a mess to me. I apply some preprocessing before putting the signal through the SRC4392 and I have switched off the SRC4392's decimation filter.

But is it better than a YSF210B or a CXD1144/CXD1244 nevermind a PMD100 or a custom solution ? I have a dac with one of these things in it and all it seems to do is smear itself over all that passes through it at the same as forcing the different sample rates of my many files into the same bland mess. Fortunately it can be switched out.

========

"Imagination Is More Important Than Knowledge"

Albert Einstein

Yes, but he was talking relativistically -- meaning in a contextual framwork 😉

========

rfbrw: We need more context.

Please provide more details about your setup.

What precedes those DFs you noted (YSF210, CXD1144/CXD1244, PMD100)? E.g., is it in a CDP where you have a decoder chip (which one)?

Is it in a DAC with a receiver and/or USB chip -- which one(s)? Or an Amanero?

And what follows your DF chips ... DAC chip, and its output stage and/or or i/v stage.

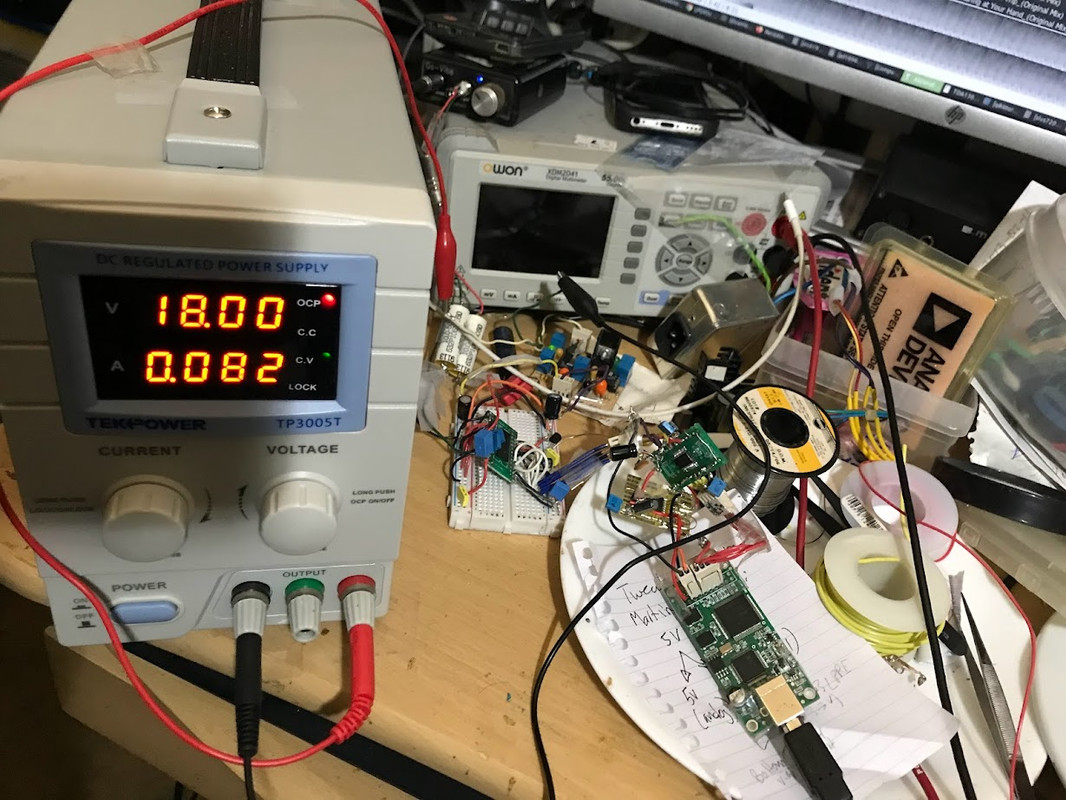

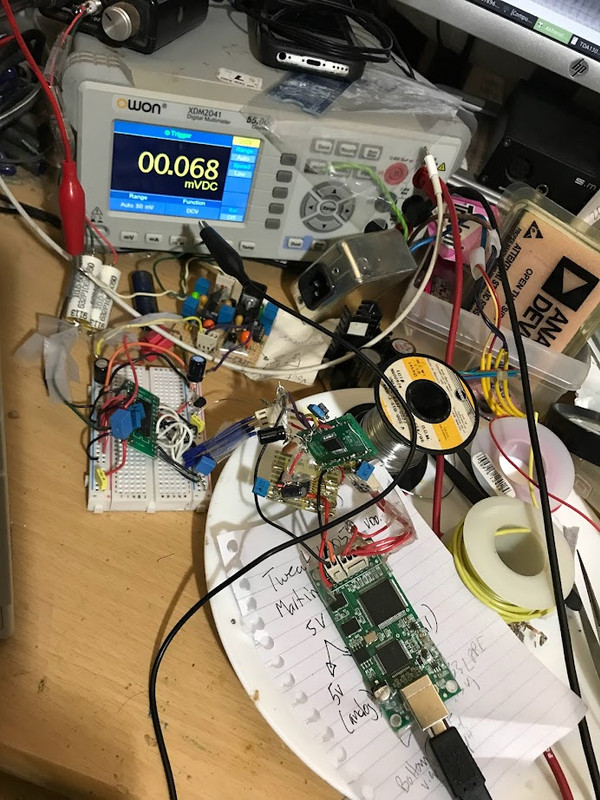

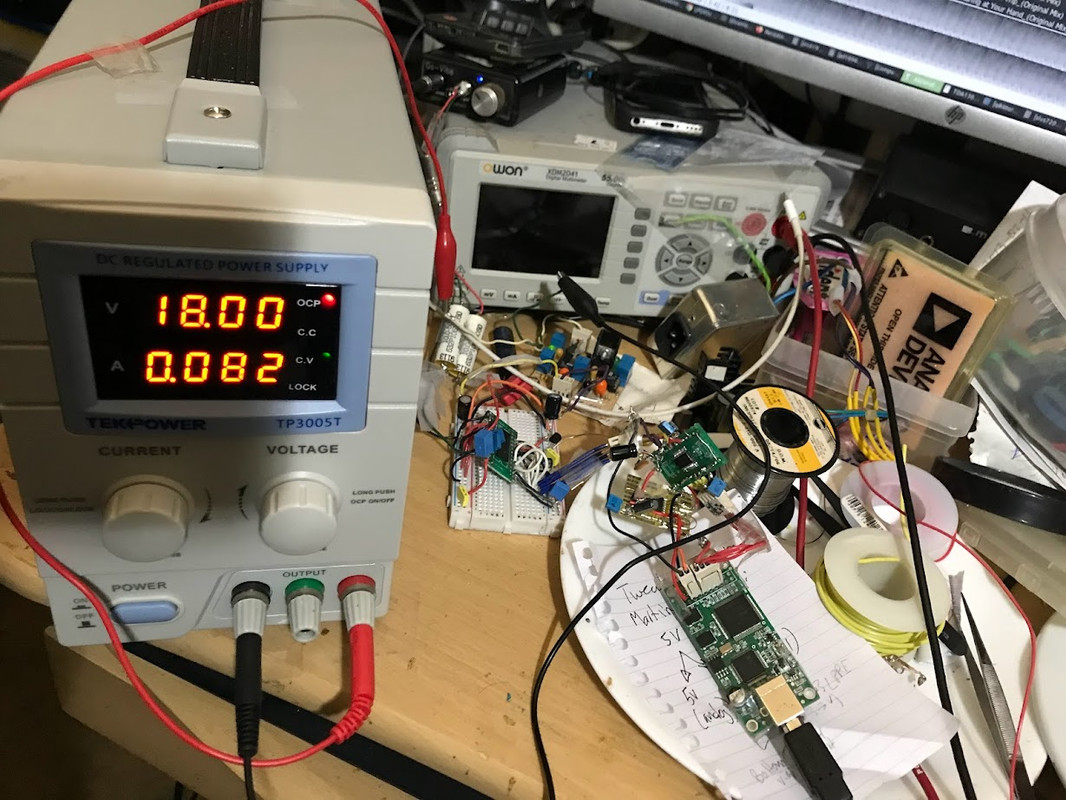

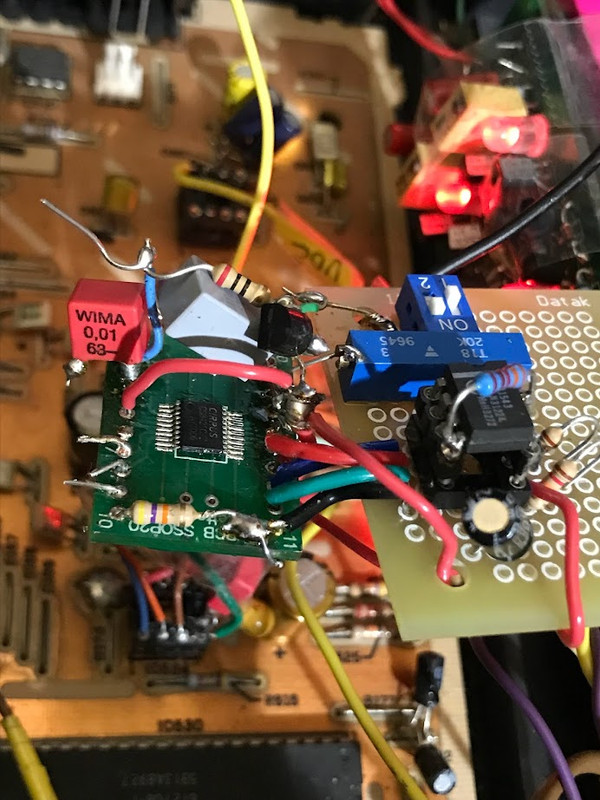

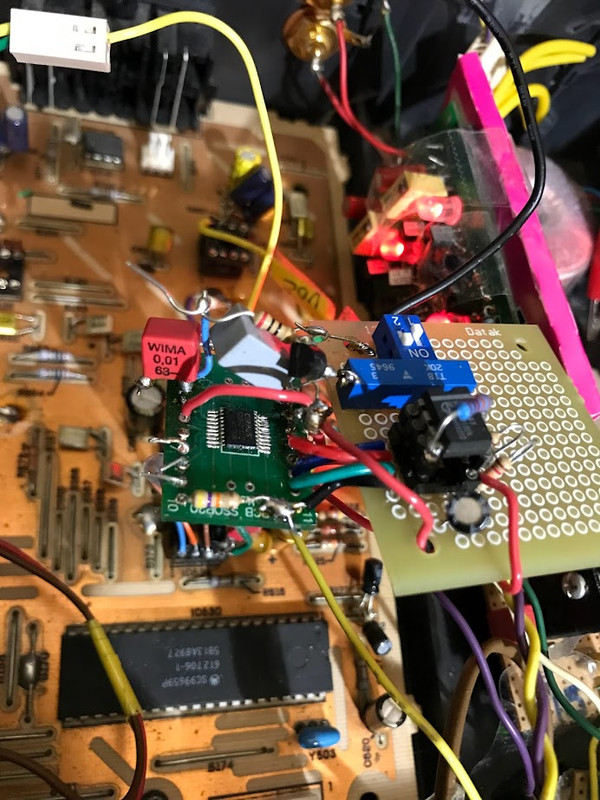

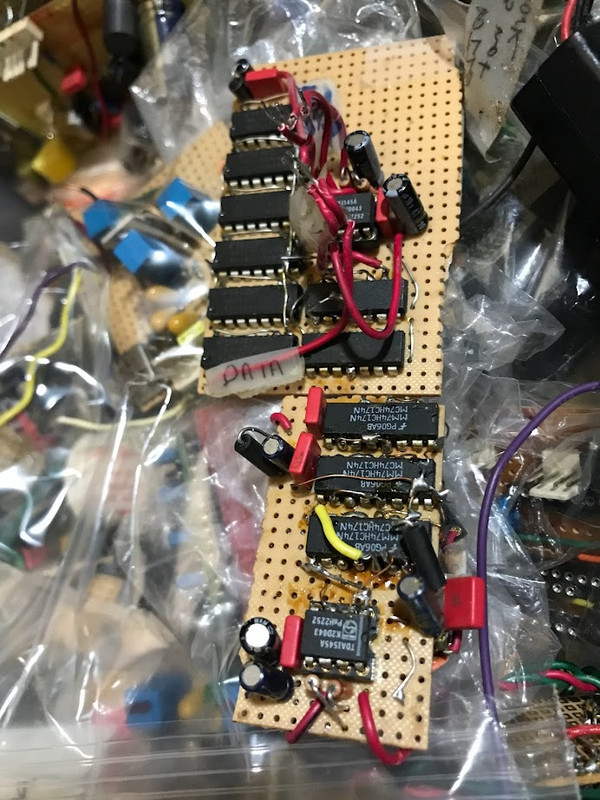

Some major improvements to the messy project ...

TDA1305 now using a highly-regulated (see **) 5.0vdc on its V (analog) and V (internal opamp) pwr pins. Pin 10 (V_DDD) now a uses three-pin LP2950-33LPRE to bring 5.0v to 3.3v (ideal for I2S from incoming 3.3v devices). About that 3.3V for V_DDD. It seems that other DAC datasheets --PCM 1792, 1794, etc -- specifically mention V_DDD being fed 3.3v.

And, yes, the sonic improvements are quite significant.

** There is "new" protoboard in these images ... not so new as I built a few Flea's over 13 yrs ago, including the one in the photos... notice the 18.00V. Martin should recognize that.

TDA1305 now using a highly-regulated (see **) 5.0vdc on its V (analog) and V (internal opamp) pwr pins. Pin 10 (V_DDD) now a uses three-pin LP2950-33LPRE to bring 5.0v to 3.3v (ideal for I2S from incoming 3.3v devices). About that 3.3V for V_DDD. It seems that other DAC datasheets --PCM 1792, 1794, etc -- specifically mention V_DDD being fed 3.3v.

And, yes, the sonic improvements are quite significant.

** There is "new" protoboard in these images ... not so new as I built a few Flea's over 13 yrs ago, including the one in the photos... notice the 18.00V. Martin should recognize that.

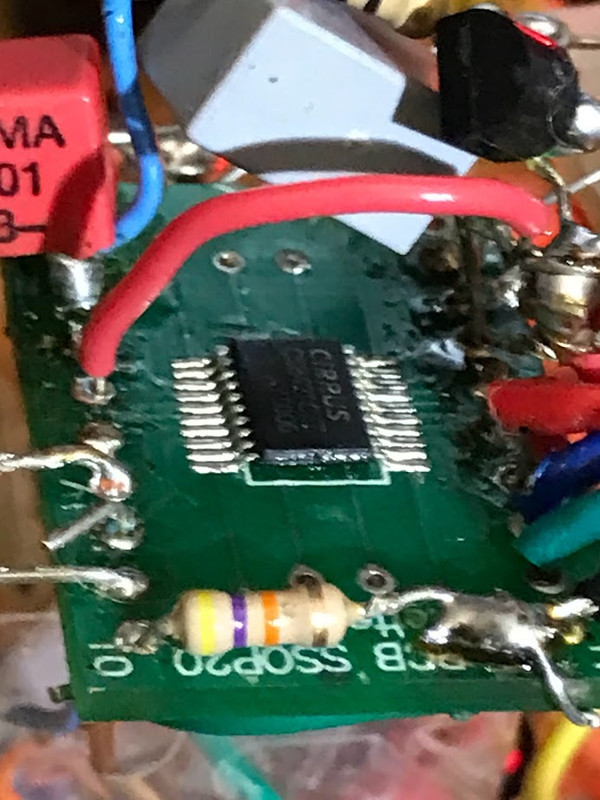

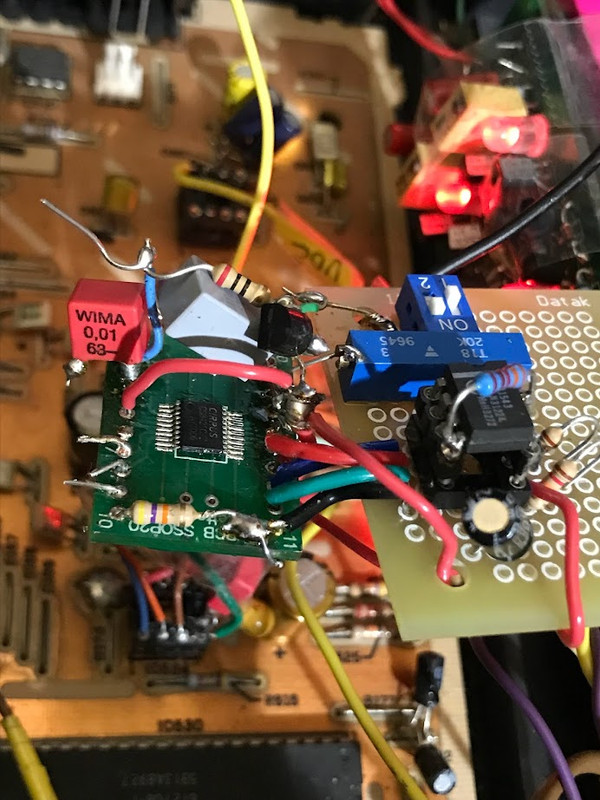

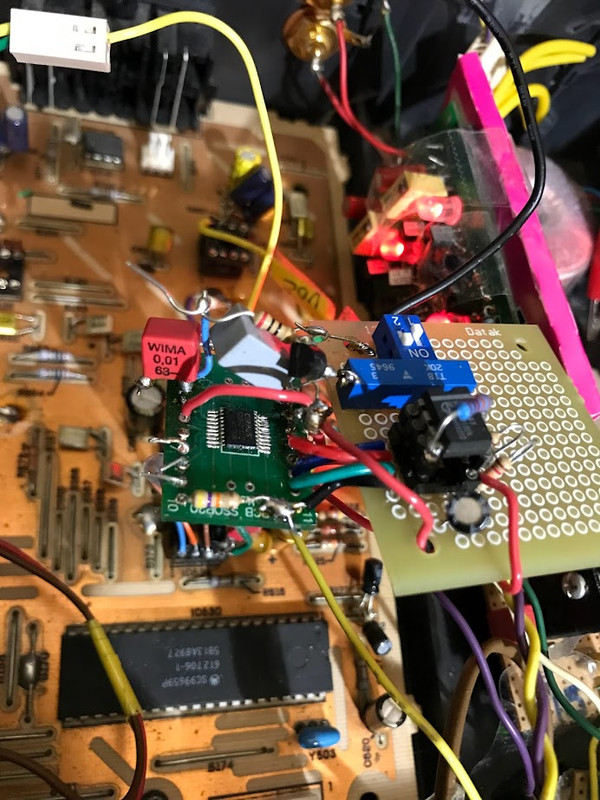

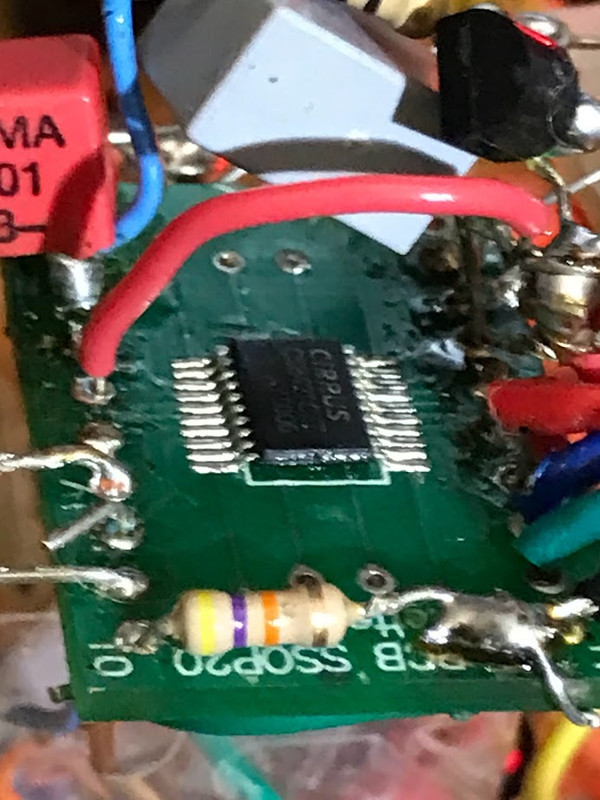

In this thread, I've successfully implemented the AD1896 and SRC4192 asrc's. After quite bit of time tweaking, some very good-sounding success with the last of the ASIC-based ASRCs in my kit. This one, the CS8421, currently feeding a tda1543 from my DREAM Project test-bed experiment. Not using a downstream digital filter. The 8421 is essentially up-sampling at 2x.

Note the long, variable resistor. The 8421's Output Port Configurations are based on weird resistor values. See DS: Table 3. Serial Audio Output Port Start-Up Options (SAOF).

Note the DIP switch. No. 2 is for toggling between I2S and other modes. Working on an I2S to EIAJ solution for "Sony" format DACs using this/any ASRC alone. Format conversion using glue logic is messy!

===========

These I2S to EIAJ converters work but are messy. (These must be a more elegant soln!)

===========

Note the long, variable resistor. The 8421's Output Port Configurations are based on weird resistor values. See DS: Table 3. Serial Audio Output Port Start-Up Options (SAOF).

Note the DIP switch. No. 2 is for toggling between I2S and other modes. Working on an I2S to EIAJ solution for "Sony" format DACs using this/any ASRC alone. Format conversion using glue logic is messy!

===========

These I2S to EIAJ converters work but are messy. (These must be a more elegant soln!)

===========

Too much romance to my eyes but if you are looking for them: I have TDA1543 and TDA1545 (soic) in stock in numbers.

Never ever measure a TDA1543 DAC.

Never ever measure a TDA1543 DAC.

Last edited:

The CS8421 is significantly more sensitive than the other two ASRC's that I noted. For example:the CS8421, currently feeding a tda1543

+2.5-V Digital Supply (VD)

+3.3-V or 5.0-V Digital Interface (VL)

Note the to-92 small lp2950-33lpre3 regulator in the photos. This is a 3.3 v reg. part with a 20R in series to drop the 3.3 to 2.5V. I had no 2.5v reg so I had to improvise with a 3.3v part! Works well, but man is that VD/VL voltage difference critical.

Still trying to get another I2S dac -- tda1387 -- to work. And then the 1545 EIAJ. No luck with either those thus far. But 1543 sounds very, very good with no noise and clean separation. Do have some issues where signal not latching, but restarting the CD player fixes this. Again, the CS8421 is very touchy ... but when it works, it does so well.

Check you inbox.Too much romance to my eyes but if you are looking for them: I have TDA1543 and TDA1545 (soic) in stock in numbers.

Never ever measure a TDA1543 DAC.

========

If anyone has seen my DREAM Project thread, you'll note I can swap out DACs and DFs and ASRCs fairly quickly, into and out of the same Maganavox dream machine, with the Rudolf I/V.

About the 1543 ... I never paid much attn to it until recently.

The "Economy" description on the DS cover page did Philips no favors.

This DAC can sound very good and clean if you supply it with decent power. And it does very well in NOS or asrc or DF.

Now listening to Synchronicity, thru asynchronous 1543 😉

Why don't you just use left-justified output format with CS8421?Working on an I2S to EIAJ solution for "Sony" format DACs using this/any ASRC alone. Format conversion using glue logic is messy!

- Home

- Source & Line

- Digital Line Level

- Revisiting ASRC (sample rate conversion) and up-sampling