Soren,

a needed information for the filter diy fraction 😉

What is the possible maximum number of coefficients for the DSD FIR1 filters?

The DSD Filters are decimation FIR filters from DSD Clock down to 352 Khz, max number of coefficients is 1016, see 1021filt_103.txt for config details.

+1

No sound after upgrade to 1.03, had to rollback to 0.99. mine is v2 stock board.

What could be the issue, none of the inputs working, DAC locks onto optical/spdif/i2s inputs (tested all 3 separately) but no sound

Let me look into it, I did all my testing on a rev1 board, shouldn't be that many differences....

Let me look into it, I did all my testing on a rev1 board, shouldn't be that many differences....

Was able to update both of my balanced mode v2's no problem.

Let me look into it, I did all my testing on a rev1 board, shouldn't be that many differences....

Mine is to a rev 2 board tried about 5-6 times to update,but sound only with 0.99.

Mine is to a rev 2 board tried about 5-6 times to update,but sound only with 0.99.

Can you please show an uManager "# set" dump ?

DoP over SPDIF...

Soren: I work for a company which makes an Ethernet Renderer with I2S (LVDS) and SPDIF output. Indeed, our device will output DoP directly on its SPDIF output. I do not know how many other sources do this, but I can confirm that ours does, so DoP decoding on the SPDIF input would be desirable for our customers.

I'm preparing the next dam1021 firmware release in a few days, will include full DSD support up to DoP128 and native DSD256 over the I2S interface, limited only by the USB to I2S interface's capabilities. The new DSD functionality will convert DSD directly to 352K PCM using a 1024 tab FIR decimation filter.

I have a question: It's actually the USB to I2S interface that handle DoP, the question is if there is a need for DoP support over SPDIF interface, if so I need to do my own DoP firmware.... So do anybody have any hardware that actually outputs DoP over SPDIF ?

I would also like to take suggestions about any simple functionality that need to be added before release, like to have the "V00" status output to indicate no signal, which will be added. Any suggestions have to be simple and easily tested here without additional hardware.

Soren: I work for a company which makes an Ethernet Renderer with I2S (LVDS) and SPDIF output. Indeed, our device will output DoP directly on its SPDIF output. I do not know how many other sources do this, but I can confirm that ours does, so DoP decoding on the SPDIF input would be desirable for our customers.

check out...

It is: Sonore Signature Rendu, see website:

Sonore.us

Designed to be the best SPDIF/I2S (LVDS) source possible, no compromises.

barrows - interested in such a thing! What company is this if I may?

//

It is: Sonore Signature Rendu, see website:

Sonore.us

Designed to be the best SPDIF/I2S (LVDS) source possible, no compromises.

Is this what you mean?:Can you please show an uManager "# set" dump ?

# set

Conspeed = 115200

Volume = -99

Filter = Linear

Mode = Normal

#

With the new firmware the MCLK pin now is clocking at 12288000 instead of 24576000.

Had to change the botic driver parameter snd_soc_botic.clk_48k to the new value in order for sound to play at normal speed from beaglebone black.

@Soekris, can you please verify if that is true. Further to that are there any plans for enabling FSEL in the next firmware?

Thanks

Had to change the botic driver parameter snd_soc_botic.clk_48k to the new value in order for sound to play at normal speed from beaglebone black.

@Soekris, can you please verify if that is true. Further to that are there any plans for enabling FSEL in the next firmware?

Thanks

Try volume 00!Is this what you mean?:

# set

Conspeed = 115200

Volume = -99

Filter = Linear

Mode = Normal

#

Volume 00= no go..Try volume 00!

Actualy I see that nomatter how I set the volumecontrol itś allways on -99,strange!

Last edited:

With the new firmware the MCLK pin now is clocking at 12288000 instead of 24576000.

Had to change the botic driver parameter snd_soc_botic.clk_48k to the new value in order for sound to play at normal speed from beaglebone black.

@Soekris, can you please verify if that is true. Further to that are there any plans for enabling FSEL in the next firmware?

Thanks

MCLK/FSEL is not supported yet, although MCLK currently are supposed to output Master Clock divided by two, mostly for my testing. Did some changes to internal clock structure, will output div by two again in next version.

Implementing MCLK/FSEL is more a question about available time to set up testing, coding should be easy....

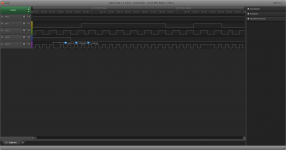

I tried my saleae logic analyzer and have noticed that MCLK has a few glitches. Is this normal?

That actually looks like glitch free clock switching when locking to new clock....

Volume 00= no go..

Actualy I see that nomatter how I set the volumecontrol itś allways on -99,strange!

How do you control volume, do you have a potmeter ?

Can you please also do a dump of power up status on the Serial Port ?

And maybe a dump of uManager "filters" command, when locked ?

How do you control volume, do you have a potmeter ?

Can you please also do a dump of power up status on the Serial Port ?

And maybe a dump of uManager "filters" command, when locked ?

Yes I have a potentiometer.

How do I do that?(Power up status) (and filters command?)

That actually looks like glitch free clock switching when locking to new clock....

Well that capture is taken while the DAM had locked on signal and sound was playing. More to that in the measured setup MCLK was coming out of DAM to the beaglebone black which is slaved on the DAM. Could you please explain what you mean by locking to new clock? (Forgive my ignorance on this but I thought that MCLK should be steady clocking while locked on the signal)

maybe this is the powerup status:Yes I have a potentiometer.

How do I do that?(Power up status) (and filters command?)

R1.03

I3

L000

F5

V+00

I3

I1

L044

V-02

V-07

V-13

V-19

V-27

V-34

V-41

V-48

V-53

V-57

V-60

V-63

V-65

V-67

V-68

V-70

V-72

V-74

V-76

V-78

V-79

V-80

V-99

V-99

V-99

V-99

V-99

V-99

V-99

V-79

V-78

V-76

V-73

V-66

V-58

V-47

V-34

V-23

V-15

V-08

V-03

V+01

V+04

V+06

V+08

V+10

V+10

V+10

V+10

V+10

V+10

And when I turn the volume pot it works as it should.(But no sound)

How about the filters?

Well that capture is taken while the DAM had locked on signal and sound was playing. More to that in the measured setup MCLK was coming out of DAM to the beaglebone black which is slaved on the DAM. Could you please explain what you mean by locking to new clock? (Forgive my ignorance on this but I thought that MCLK should be steady clocking while locked on the signal)

Does the "24 Mhz" listed on the top line means it's sampling with 24 Mhz ? Then it's kinda useless....

Yes I have a potentiometer.

How do I do that?(Power up status) (and filters command?)

Enter uManager with "+++", enter "filters" command....

While connecting info: How is you board powered ?

Last edited:

- Home

- Vendor's Bazaar

- Reference DAC Module - Discrete R-2R Sign Magnitude 24 bit 384 KHz