A short test tonight, - and Im even more confused. Started with the smallest gap in the xformer and inductance was 400uH +20uH external. It works and regulates ok, but does not look like, ZVS. Mosfets cool under load.

Adjusted the gap to get the design-goal of 120uH +20uH external. It still works an we have ZVS, but Mosfets heat up?

My Best guess is that the lower inductances raise the ciculating current enough to tigger Cdv/dt false-gate-trig.

Kind regards TroelsM

I thought circulation currents? and the slow body diode mosfet? strange to have no zvs as the rest do work oke with cool mosfets, you now we have upper resonance technologie but also lower resonance, do you not have a mistake there? strange, i suggests try mosfets with low on resistance, and fast body diode, As I saw there is a small crossconduction left in your scope pic, it is excacly where the current peak is also, maybe a bigger deadtime and back to the 400 uH and 20 uH and try.

regards

I did a simple simulation today of the halfbridge and LLC -network to look more at the possible shoot-through. From the sim it looks like that I simply need more deadtime. I'm working with L6599 and deadtime cannot be set directly.

I'm trying to adjust turn-on-gate-resistance and it appears to have an effect similar to longer deadtime ( turn-on is delayed)

Kind regards TroelsM

I'm trying to adjust turn-on-gate-resistance and it appears to have an effect similar to longer deadtime ( turn-on is delayed)

Kind regards TroelsM

I did a simple simulation today of the halfbridge and LLC -network to look more at the possible shoot-through. From the sim it looks like that I simply need more deadtime. I'm working with L6599 and deadtime cannot be set directly.

I'm trying to adjust turn-on-gate-resistance and it appears to have an effect similar to longer deadtime ( turn-on is delayed)

Kind regards TroelsM

chip with programmed deadtime can be sometimes get trouble, a fet with lowe gate capacitance and a faster rise/fall time can do also the trick,and yes a bigger resistor on gate but do slow the risetimes more and as such maybe it do not work.

regards

Did you measure magnetizing current?Short test with bigger gate-resistor for slow turn on, did not work. Still heats up at No load, so heat is not caused by Ron.

Øv! (danish. Hard to translate)

Kind regards TroelsM

have a look at #45No, No time to measure anything Else than the switching waveforms and they looked like I would expect. (with My limited experience). How would you measure that Best?

Simulated a bit more and I think the heat is due to Cdv/dt shoot-through. When googling that term I found a document from IR taking about it (CDV/DT INDUCED TURN-ON IN SYNCHRONOUS BUCK REGULATORS, Thomas Wu, International Rectifier)

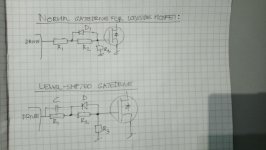

One of the proposed solutions is to use "ac"-drive for the lowside mosfet in order to drive the gate below Vss and thus getting a better margin before Cdv/dt problems arise.

As proposed the AC-drive is simply implemented by putting a cap in series with the gate-signal so that it swings +/-6V instead of the normal +12V with respect to Vss.

I think that it would be better to drive the mosfet with an asymetric signal: +10V/-5V and to implement that I think the attached "levelshifted gatedrive" could be used.

The Cap level-shifts as shown in the IR-paper, but R1 and R3 will define a DC-offset so that we can have asymmetric drive.

In my simple sim R1 and R2 is 1K, R2 can be 22R and C could be 47nF for 50-200KHz operation

I dont claim it to be a new invention, but I dont think I have seen it before. Do you think it will work and have you seen it before?

Kind regards TroelsM

One of the proposed solutions is to use "ac"-drive for the lowside mosfet in order to drive the gate below Vss and thus getting a better margin before Cdv/dt problems arise.

As proposed the AC-drive is simply implemented by putting a cap in series with the gate-signal so that it swings +/-6V instead of the normal +12V with respect to Vss.

I think that it would be better to drive the mosfet with an asymetric signal: +10V/-5V and to implement that I think the attached "levelshifted gatedrive" could be used.

The Cap level-shifts as shown in the IR-paper, but R1 and R3 will define a DC-offset so that we can have asymmetric drive.

In my simple sim R1 and R2 is 1K, R2 can be 22R and C could be 47nF for 50-200KHz operation

I dont claim it to be a new invention, but I dont think I have seen it before. Do you think it will work and have you seen it before?

Kind regards TroelsM

Attachments

Last edited:

You have seen this before in #34I dont claim it to be a new invention, but I dont think I have seen it before. Do you think it will work and have you seen it before?

Kind regards TroelsM

My scope plot shows the ac drive of the gates with their neg voltage sections.@voltwide: Sorry, I dont understand what you mean?

Kind regards TroelsM

In my application a standard LLC-driver chip NCP1396 is coupled via caps of some 10nF to the gates of the powerMOSFETs. Due to dead-time the duty cycle is a bit smaller than 50%, resulting in a slight asymmetry behind the coupling caps making the pos pulses a bit bigger than the neg ones.OK, now I got it. It appears to be symmetrical gatedrawn around zero volt. What I'm proposing is a way to make it a-symmetrical. - if that could possibly be a good thing?

Considering the resulting Rdson there is not much difference between +7V and +12V gate drive. So I do not see the urge to make things more complicated than necessary by applying an asymmetric gate drive signal.

There may not be a big difference between +/-6V and +8/-4V, but I'm only adding a single resistor to the standard setup so I dont see it as much more complicated.

I havnt tested it in real-life yet, but hopefully I can within the next days.

Thanks for all the good input.

Kind regards TroelsM

I havnt tested it in real-life yet, but hopefully I can within the next days.

Thanks for all the good input.

Kind regards TroelsM

I don't have much to say, but a small amount if experience with somewhat smaller so called logic level MOSFETs.

I found that despite the threshold voltage being low, I actually required more than the 5V TTL drive signal.

So I buffered with BJT and FET to drive the next H Bridge. Using a FET I found that it performed far quicker switching than BJT but turn off was vastly improved using a totem pole driver to pull up or down the gate.

In the end i stuck with BJT drivers as they seemed to need less complex circuitry, and I'm lazy.

I found that despite the threshold voltage being low, I actually required more than the 5V TTL drive signal.

So I buffered with BJT and FET to drive the next H Bridge. Using a FET I found that it performed far quicker switching than BJT but turn off was vastly improved using a totem pole driver to pull up or down the gate.

In the end i stuck with BJT drivers as they seemed to need less complex circuitry, and I'm lazy.

I have simulated and tested the "level-shifted-drive" or "AC-drive" for the low-side-mosfet and I think it works.

There is still some tweaking to do on the levels and the gate-drive-resistor for teh top-side-mosfet should also be trimmed.

The mosfets still heat a little more than I would like, but some heat is to expected, so maybe I just need to be more realistic

There is still some tweaking to do on the levels and the gate-drive-resistor for teh top-side-mosfet should also be trimmed.

The mosfets still heat a little more than I would like, but some heat is to expected, so maybe I just need to be more realistic

Tested a little more yesterday and it turns out that my transformer was saturating at a current around the level of the curculating resonant current. Thus it was acting like a short. ( so much for trusting the calculators to do the math, and being too laxy to double-check ;-) ).

Anyways. I added turns and made the gap bigger and now the transformer will work with 12Ap before saturation. Simulations show that current should be below 10A.

Furthermore I found a difference between the simulation and the prototype that may explain why the voltage was dropping under load in the prototype: I had simulated with output capacitor-ESR around 30mOhm and in real life im using 3x330u/100V in each rail giving approx 130moHm total ESR in each rail.

With an classD connected to the LLC and heavy electronic music I get approx 200Wp@8Ohm with very little heat anywhere. I would really like to avoid the rail-sagging, but with an amplifier as load it may not be a big problem after all.

TroelsM

Anyways. I added turns and made the gap bigger and now the transformer will work with 12Ap before saturation. Simulations show that current should be below 10A.

Furthermore I found a difference between the simulation and the prototype that may explain why the voltage was dropping under load in the prototype: I had simulated with output capacitor-ESR around 30mOhm and in real life im using 3x330u/100V in each rail giving approx 130moHm total ESR in each rail.

With an classD connected to the LLC and heavy electronic music I get approx 200Wp@8Ohm with very little heat anywhere. I would really like to avoid the rail-sagging, but with an amplifier as load it may not be a big problem after all.

TroelsM

I used a spreadsheet called IRS27951_angol made by LoryLaci from the forum.

And Im NOT blaming the great tool at all, I'm was just too lacy to measure my TX before using it.

( maybe the tool did calculate everything correctly, and maybe I just didnt understand the results..)

kind regards TroelsM

And Im NOT blaming the great tool at all, I'm was just too lacy to measure my TX before using it.

( maybe the tool did calculate everything correctly, and maybe I just didnt understand the results..)

kind regards TroelsM

I used a spreadsheet called IRS27951_angol made by LoryLaci from the forum.

And Im NOT blaming the great tool at all, I'm was just too lacy to measure my TX before using it.

( maybe the tool did calculate everything correctly, and maybe I just didnt understand the results..)

kind regards TroelsM

Ahh Oke I did look at it, this is for a complete smps supply, the program I mention is only for transformer not a resonant one. but it can be used as wel.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Power Supplies

- Heating in LLC HB mosfets ?