Yes, at this moment, a quickly "ready-to-use"project maybe more meaningful and fun, since there are no manufactures can be this fast for a new chip.

Meanwhile, the OP is still hardworking on the really important things to improve the over-all performance.

A bad example of "over complexed jitter reduction solution"is topping d90(for which I have one). It has higher actually measured jitter than a common xmos solution while adopted such a complex design.

Topping used a cheap power supply solution and a bad PCB placement due to the overall cost and dimensional size limits.That's what the OP wants to avoid.

Meanwhile, the OP is still hardworking on the really important things to improve the over-all performance.

A bad example of "over complexed jitter reduction solution"is topping d90(for which I have one). It has higher actually measured jitter than a common xmos solution while adopted such a complex design.

Topping used a cheap power supply solution and a bad PCB placement due to the overall cost and dimensional size limits.That's what the OP wants to avoid.

Last edited:

Have a Topping D90 here too. Problem with so-called 'measured jitter' if done with FFTs it that FFT skirts are widened in an FFT by two different sorts of problems. Only one of them involves jitter. Jitter is an error of timing. Vref power supply noise creates errors of amplitude. The two types of errors can be considered roughly equivalent so long as they are small enough. Probably best to keep in mind they are two different things though.

Last edited:

Topping D90 has mediocre Vref which in this case is the main cause for the wide FFT skirts.

Reportedly its the secondary stage voltage regulators: https://www.analog.com/media/en/technical-documentation/data-sheets/adp7112.pdf

First stage uses SMD 317 type regulators. IIRC the second stage regulators were operating down near dropout.

First stage uses SMD 317 type regulators. IIRC the second stage regulators were operating down near dropout.

Ah OK, I see, thanks. Yes the ADP7112 is not super low noise.

For a moment I thought you were discussing the D90SE, which has a very different implementation of the Vref. I have used, and plan to use, something similar to the D90SE, so I was just worried that I might have overlooked some problems with that approach.

For a moment I thought you were discussing the D90SE, which has a very different implementation of the Vref. I have used, and plan to use, something similar to the D90SE, so I was just worried that I might have overlooked some problems with that approach.

Not only so. Topping used a dc-dc switching circuit to generate 3.3v and 1v for powering the CPLD and xmos chip. The crystal for clock is powered by a cheap chip and even under EMI bombard by the transformer, rectifier diode, the dc-dc mentioned above.

Have a look at how Holo May DAC designer did it... Each frequency (45.158MHz and 49.152MHz) has two cristal oscillators in PLL; the "cheap" one and the expensive one (CVHD-957). That will give you clues on how to do it properly... and achieve excellent results.Please tell me more about jitter issue.

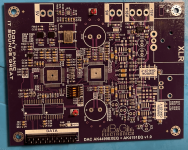

Attachments

FPGA is used for USB converter to I2S. You can use XMOS or ARM + FPGA.what about fpga? when are they used?

If somebody will be interested about this DAC to have, the only option will be already mounted and tested PCBs. The most important to me is to use high quality parts. Different parts - different sound.so, how do plan to share it?

at cost or are you planning to charge premium?If somebody will be interested about this DAC to have, the only option will be already mounted and tested PCBs. The most important to me is to use high quality parts. Different parts - different sound.

It hard to say at this moment. AKM chips are not available yet. When every information about prices of semiconductors will be clear I will let You know.I am interested too, by mounted and tested PCBs.

What about price ? Do you have an idea ?

- Home

- Source & Line

- Digital Line Level

- DAC AK4499EX Project