That will be the best - but answer is NO. All usb/i2s boards are emulating IC logic circuits with internal hardware blocks with software control. Everything is packed so close and in minimum space. There is a lot types of any unwanted "energy" in small DIE space inside the micro controllers and FPGA chips used in USB boards... Groud bouces and gliches are enormous creating huge HF noise.May I ask which method the USB board is using for converting I2S to PMC signal? FIFO?

Thanks

Unfortunately this is the common for all boards and every integrated chip employed... Only master clocks are external.

The main goal is not the sound but the space with reduced elements and price. With flexibile software access ofcourse.

.

For the contemporary FIFOs pretty much the same thing, high level of integration and software control. Emulating "old" classic FiFo. But FiFos was used with classic ICs long before MCs and FPGAs. Of-course significantly larger board areas, and all was bigger 🙂

@Tam Lin If we use shift register which propagation delay is longer as hold time in DAC, then everything will be fine? The HCT meets this requirement 🙂 ... AHCT was also tested and it worked (and it should not because shift’s Tpd < dac’s Th) 🤔

Of course we can use circuitry where BCK for shift registers is slightly slowed down. Or the stop-clock version where BCK is generated for DAC chips. The advantage still be questionable because no one compared these versions 🤣

I tried HCT and AHCT on the pavouk version of the AD1865 DAC. They didn't have AHCT at the local store so I put the HCT on. Later when I bought the AHCT I replaced it and didn't hear any difference.

Next thing I will try is PCM63 without shift registers.

@Tam Lin I know what you want to say. These shift registers are tricky and they messed my head many times.

Consider DAC input as the next shift register. So if you connect DACs shift register on the chain, what will happen? 🤔

If the first three registers worked, why the fourth should be broken?

Many of the favored NOS DAC chips have setup and hold times of 10ns or more. Many of the favored shift registers have propagation delays of 5ns or less. The two don’t work together because you end up with the input to the DAC chip changing during the DAC’s hold time. In the extreme you have a PCM1702 with a 15ns hold time and an AHCT164 with a typical prop delay of 3.4ns.

You may ask, why use AHCT when HCT will do the job? For most diyAudiophiles faster is always better and there are many applications where HC logic is too slow. It's best to avoid I2S and shift registers, altogether.

I think that is not related with shift registers... Because dac store word in internal memory register UNTIL get command to go to conversion when LE going from Hi to LO state. That is LE line and it happening 2X in FS period (for I2S) or 1 X in FS period for AD/PCM format.@Tam Lin If we use shift register which propagation delay is longer as hold time in DAC, then everything will be fine? The HCT meets this requirement 🙂 ... AHCT was also tested and it worked (and it should not because shift’s Tpd < dac’s Th) 🤔

Of course we can use circuitry where BCK for shift registers is slightly slowed down. Or the stop-clock version where BCK is generated for DAC chips. The advantage still be questionable because no one compared these versions 🤣

Relation SCK and DATA is "only": when SCK starts then load data word as SCK last.

After that - waiting to LE line to go from HI to lO.

IF it happens then conversion of digital binary word starts and we have analog result at the output.

That repeating...

.

One special case is (which is exact happening in this or similar designs is that we have loading next data word BUT in the same moment when conversion of the previous data word starts. AND that could be related with set and hold issues maybe.

Also a big issue is when nothing happening in the dac, (and that is long period after data was loaded waiting to be converted, ALL lines has to be Lo or 0. That means true stopped clock and just one LE burst when needed.

So do not let the data loading in the same time. For 20bit word in the 64bit window of LE occurring, you have plenty of 44 bits of time when dac doing nothing... if you divide that by 2 that's leaving 22bits of time from LE event to the word reception and another 22bits for same word going to conversion.

.

This with delayed SCK is probably for other type of conversion 1bit or so when LE line don't have a reason to exist...

.

Set and hold minimum timing is given only for the cases when data word is tightly packed in max word length of DAC and LE is exactly in the edges of this window, when LSB of word N is together with MSB of the word n=1. and conversion is going on in the "middle"...

Which is NOT the case in existing format.

Last edited:

Next thing I will try is PCM63 without shift registers.

Please do it. You are our local leader. 🤣

It is not "the same" yamaha use one or more DSP-a in addition, and probably some additional processing. So the "delay" in lines is not the same...I do not know. In this way, the shift registers were done the same as the PCM63P was in the Yamaha - only without the filter chip... Plus it has one more power supply. We will compare our different versions. I don't touch this DAC anymore. This is perfection

Does the input signal should be time delayed, slowed, before or after the register before inputing the dac chip then ? So few milli second, could it be made by smd coils in a pass band hardware conf?Not true. The shifters will have no effect on the sound provided the circuit is designed correctly. In your case, the circuit is clearly broken. That should have been obvious to any one who saw the schematic and knew how DACs operate. Of course, this is diyAudio where no one looks at a datasheet except to copy the pin-out diagram.

The problem is, at the rising edge of BCK the DAC latches the next data bit and shifts it into the sample register. At the same time, the rising edge of BCK tells the I2C shifter to move the next bit to the input of the DAC chip. Well, which bit is the DAC supposed to use. The bit that was in its input the moment BCK was asserted or the new data bit from the I2S shifter after BCK was asserted. Or maybe a garbled mixture of the two. Simply put, the I2S shifter is updating the sample bit at the very moment the DAC is trying to read it. This error is repeated in nearly every I2S circuit I have seen in this forum! Whether or not it induces audible errors depends on the circuit timing details and the hearing ability of the listener.

I called attention to this problem in my last post here but Miro blew me off. But, what do I know? I'm a software guy and all of you are hardware experts. The forum cognoscenti have told me my contributions are not useful and, although I read a lot of datasheets, I don't know how things work in the real world. OK, I'll shut up let you experts do things your way. It's just that after seeing the same stupid mistakes repeated over and over I can no longer hold my tongue.

Does the input signal should be time delayed, slowed, before or after the register before inputing the dac chip then ? So few milli second, could it be made by smd coils in a pass band hardware conf?

This is Pioneer PD-8500 CD player

According to datashit, IC 732, IC 733 the MC74HCU04N chip can work as an inverter or a signal amplifier. In this case, the signal is inverted 180 degrees on the first input, but the same signal passes through the second gate and rotates another 180 degrees. So we have back to the input in terms of logical states. It can therefore only function as an I2S bus pulse amplifier. The SM5813 filter used in the CD player meets the requirements of PCM63 blocks. So why are these systems used instead shifter registers? On the one hand, they eliminate errors resulting from voltage drops on quite long I2S signal paths, about 30 cm, but on the other hand, they cause some delays due to the imperfection of the MC74HCU04N circuits.If we don't have a filter chip, then there must be shifter registers. And a short wired connection.

Last edited:

Miro, did you look at what Doede Duma did on DDDAC? There is a similar schematic, the same shift registers, I2S input. The DAC IC is PCM1794 also in NOS mode. I'm not expert enough to talk about it, because I'm a mechanical engineer. 🤣

But Doede Duma was not the first and only one with 5-6 shifters.

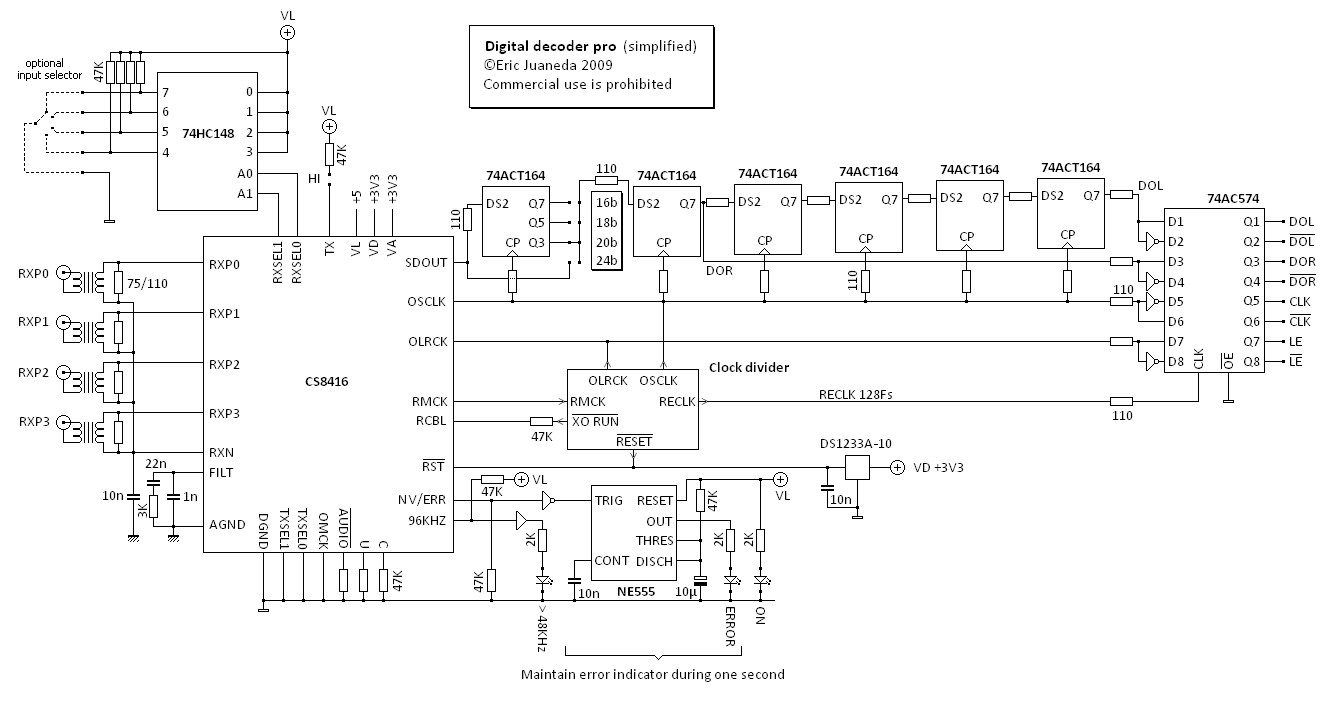

-Eric Juaneda :

I could upload pictures continuously for 5 days of audio/video/pc devices that have even more sifters🤣

-Eric Juaneda :

I could upload pictures continuously for 5 days of audio/video/pc devices that have even more sifters🤣

Last edited:

View attachment 1075965

This is Pioneer PD-8500 CD player

According to datashit, IC 732, IC 733 the MC74HCU04N chip can work as an inverter or a signal amplifier. In this case, the signal is inverted 180 degrees on the first input, but the same signal passes through the second gate and rotates another 180 degrees. So we have back to the input in terms of logical states. It can therefore only function as an I2S bus pulse amplifier.

I thought the inverter strings are intended to add small delays...?

on 30cm I2S cable ? 😉I thought the inverter strings are intended to add small delays...?

on 30cm I2S cable ? 😉

OK than why 2 inverters instead of one line driver?

To drive long lines a buffer at the source would be the choice (74HCT125). These inverter strings I have seen in circuits of commercial products even if lines are very short: surely they add delay to align timing...

It is not "the same" yamaha use one or more DSP-a in addition, and probably some additional processing. So the "delay" in lines is not the same...

Probably.😛These inverter strings I have seen in circuits of commercial products even if lines are very short: surely they add delay to align timing...

The two registers cancel logically but at the last output you have added 360° phase time cause the substract as it was a coil? ...signal is analog, no ?

Hum, I do not know why I talked about coil to delay in a passband conf as a coil is non only 180° more plus the eventual mH but also a low pass filter, uh!

Forgett it.

I assume experienced RF pcb designer as our Marce member alas inactive today, knew this and had pro soft suit and expensivz to mesure it. Seems diy in digital domain is a lost cause...

Hum, I do not know why I talked about coil to delay in a passband conf as a coil is non only 180° more plus the eventual mH but also a low pass filter, uh!

Forgett it.

I assume experienced RF pcb designer as our Marce member alas inactive today, knew this and had pro soft suit and expensivz to mesure it. Seems diy in digital domain is a lost cause...

- Home

- Source & Line

- Digital Line Level

- DAC AD1862: Almost THT, I2S input, NOS, R-2R