I know what you mean. The question is how to do it simple? How to shift the LE without touching it with flip-flops? ... you can do the "pulse" from LRCK, but the result can be jitter from propagation delay.It is most important to understand that finishing register loading and LE changing state from 1 to 0 is happening almost instantly. And that is the cae ONLY if Rigt Justified format used... Because of that only LE in this case has to be precise but other syncs are also important. And Jitter in time can have max afect.

IF you left few bits of BCK when registers are already loaded, and LE stays in place, jitter could not be from that importance and DAc have much more time to "rest" and go to the conversion.

That is Whu Time Simultaneous format did this and Pacific Microsonic done the same - left blank sertain amount of BCKs prior to LE change state.

.

Only if we have 32 bit word we simply have to use all 32 bit for channel word and make it like pure Right Jusified format.

In all other cases we dont have to.

For 24 bit word we have 4 bits at each side of the word and 4 bits before each command to conversion.

Psu - 1 have 4700 and 6800/25V. I am planning change on 16V.Which capacitors exactly?

On the Dac board have many Wima 0.1uF and 6pcs Kemet 0.1uf (ceramic). I also will change all of them on np0 smd.

Yes. That's all that matters. At least for those of us who don’t know much about theory, but we love good audio devices.Exactly, the listening test is the best way 😊

I said that all other R2R LSB not affected or corrupted?What do you mean by "bits are corrupted"?

Thermometer from MSBs in AD1862/AD1865 is not for a higher precision, but rather for eliminating glitch. R-2R ladder is inside the AD1862/5 for the LSBs, is not?

Hard to say if the full R2R ladder is incorporated in any advanced R2R chips, even DAC8811 has the 3 MSBs segmented and the rest is R2R 🤔

Exactly, the listening test is the best way 😊

.

Thermomether code actually is not for the derease glitches but for the precision.

Look at the module before themother encoder - ADDer. this module is for glitches...

ADDer is emulating the only true non-glitch code - Gray code.

.

There are nO ladder R2R inside any of DAC chips. R2R ladder is network of passive Resistors

There are NO pasive kcomponents in DACs

They are using active elements to emulate R. Refer to for the example TDA1541A internal structure schematic.

It is not complicated I already done something. It is much simplier than for TDA1540/41 TS mode. No need to move LE at all just optionally cut-out the unnecessary "1" stateI know what you mean. The question is how to do it simple? How to shift the LE without touching it with flip-flops? ... you can do the "pulse" from LRCK, but the result can be jitter from propagation delay.

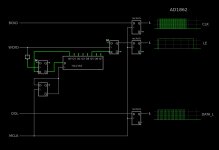

Take a look at the simplified input format of AD1862. That is more like time simultaneous format without inverted MSB, and sign.

So jut one half of BCK pulse needed to tell the dac to go into DA konversion...

It is more like Time simoultaneous format trigering conversion not like Rigt Justified.

And You dont have to delay the LR latch.

Zoran, did you check my simulation I posted in #3957? Attached a screenshot of the output of my circuit (in this case fed from the PMD200): as far as I understand the timing satisfies your remarks - or am I missing something?

Attachments

Do not use the 0,1 uF at the output of the 7xxx reg ic, a simple 100 uF is enough, then decouple at load pins on Miro's board.Psu - 1 have 4700 and 6800/25V. I am planning change on 16V.

On the Dac board have many Wima 0.1uF and 6pcs Kemet 0.1uf (ceramic). I also will change all of them on np0 smd.

If you reduce the voltage of the smoothing caps then reduce the secondaries outputs acordingly. Remember the 1.41 x rule we talk already in the thread. 12V secondaries for instance will be too much with a 16V smoothing cap. This first cap shoukd always be surdimensioned in temperature and voltage rattings. Epcos and Pan FC are perfectly fine. Btw I use an long life Epcos as smoothing then the FC at reservoir cap on PSU 2.

No, I won't. Isn't Wima's located before MC stabs?Do not use the 0,1 uF at the output of the 7xxx reg ic, a simple 100 uF is enough, then decouple at load pins on Miro's board.

If you reduce the voltage of the smoothing caps then reduce the secondaries outputs acordingly. Remember the 1.41 x rule we talk already in the thread. 12V secondaries for instance will be too much with a 16V smoothing cap. This first cap shoukd always be surdimensioned in temperature and voltage rattings. Epcos and Pan FC are perfectly fine. Btw I use an long life Epcos as smoothing then the FC at reservoir cap on PSU 2.

0.1 and 0.33uf. I don't touch them.

You say that 4700uf can swap on 100uf or I don't get your Idea???

Yes the low values are mandatory on the input pin only.

I just didn't get the idea for the 4700 uF there. The big cap before the reg suffice an ideally should be higher capacitance and voltage type in order to have the lowest esr and ideally just a decoupling at the load. Sometimes a little value can calm down things at the ic output, typically 10 to 100 uF , but it should be tested each time imo with listening test if mandatory or not.

If the idea is more to have a constant current source with the 4700 uF then I will raise it to 10 000 uF then the ic will just serve to feed it and will have no behavior at all. Simulation s can tell you other things though. Experimentating is the key.

I just didn't get the idea for the 4700 uF there. The big cap before the reg suffice an ideally should be higher capacitance and voltage type in order to have the lowest esr and ideally just a decoupling at the load. Sometimes a little value can calm down things at the ic output, typically 10 to 100 uF , but it should be tested each time imo with listening test if mandatory or not.

If the idea is more to have a constant current source with the 4700 uF then I will raise it to 10 000 uF then the ic will just serve to feed it and will have no behavior at all. Simulation s can tell you other things though. Experimentating is the key.

@sworder84 The main advantage with PSU-1 is that you can use very big capacitor values on the output. Big capacitor can serve as a battery 😉 If you struggle to find the capacitors, look for Nichicon or Panasonic Low ESR or Low impedance type and use these 🙂

So in this scenario the output cap should be with lower esr (better)than the input main cap = higher capacitance and voltage for the output cap and as you are here feed it through a 1R resistor..

But nothing should stop anyone to try the PSU just with a final decoupling at the IC of the oap (w/o that big cap) just in case the 7xxx are able to enough transcient 😉 ! And big caps are expensive...🙁

But nothing should stop anyone to try the PSU just with a final decoupling at the IC of the oap (w/o that big cap) just in case the 7xxx are able to enough transcient 😉 ! And big caps are expensive...🙁

Hear by yourself... experimenting and listening are what matters.@diyiggy, I heard that bass will be suffering with a low value of capacitor, not?

Surely, at some point the technical reality of the LF cut-off frequency and the effect component values has on it has to kick in somewhere along the line or do you think a value that gives a 100Hz cut off can somehow overcome that limitation by its exotic nature?Hear by yourself... experimenting and listening are what matters.

PS Audio SL Three has RF CHOKE in parallel with Silver Mica and resistor of 100 ohms

How this affects the sound?

The choke seems to raise the HF and possibly compensate some HF loss due to NOS. Does not seem ideal.

Odd - IIRC that's a tank circuit, making a band-pass stop filter of sorts. If the values are right, resonant at 730 kHz.

I've found that even the 47pF cap itself isn't needed in my environment.

I've found that even the 47pF cap itself isn't needed in my environment.

Last edited:

- Home

- Source & Line

- Digital Line Level

- DAC AD1862: Almost THT, I2S input, NOS, R-2R