Thanks Ian,

so the 3 pS is measured at the last stage of the FIFO board (feeded by the Clock board which is after it)) but is there any added jitter after crossing the flat cable to the Clock board (which is physically the last stage)?

I assume the MCLK signal is the same but does the I2S signals (be it DSD over PCM) at the output of the uf-l Clock board ? Still 3 pS (the Bitclock signal)?

Is there a little waste between the FIFO board and the clock board dur to the non 100 % shielded flat cable (EMI catching?) for instance or due to the fact the I2S signal after the FIFO board is travelling trough the Clock board ?

Again sorry of my poor understanding

so the 3 pS is measured at the last stage of the FIFO board (feeded by the Clock board which is after it)) but is there any added jitter after crossing the flat cable to the Clock board (which is physically the last stage)?

I assume the MCLK signal is the same but does the I2S signals (be it DSD over PCM) at the output of the uf-l Clock board ? Still 3 pS (the Bitclock signal)?

Is there a little waste between the FIFO board and the clock board dur to the non 100 % shielded flat cable (EMI catching?) for instance or due to the fact the I2S signal after the FIFO board is travelling trough the Clock board ?

Again sorry of my poor understanding

Last edited:

Thanks Ian,

so the 3 pS is measured at the last stage of the FIFO board (feeded by the Clock board which is after it)) but is there any added jitter after crossing the flat cable to the Clock board (which is physically the last stage)?

I assume the MCLK signal is the same but does the I2S signals (be it DSD over PCM) at the output of the uf-l Clock board ? Still 3 pS (the Bitclock signal)?

Is there a little waste between the FIFO board and the clock board dur to the non 100 % shielded flat cable (EMI catching?) for instance or due to the fact the I2S signal after the FIFO board is travelling trough the Clock board ?

Again sorry of my poor understanding

3ps is the noise floor my 8GS/s LeCroy measurement. For my OCXO, the finial jitter could be 1ps RMS or less. That's why I said I would follow the specification of XO for phase noise (or jitter for time domain).

The additive jitter of my clock board is around 20 fs.

Ian

3ps is the noise floor my 8GS/s LeCroy measurement. For my OCXO, the finial jitter could be 1ps RMS or less. That's why I said I would follow the specification of XO for phase noise (or jitter for time domain).

The additive jitter of my clock board is around 20 fs.

Ian

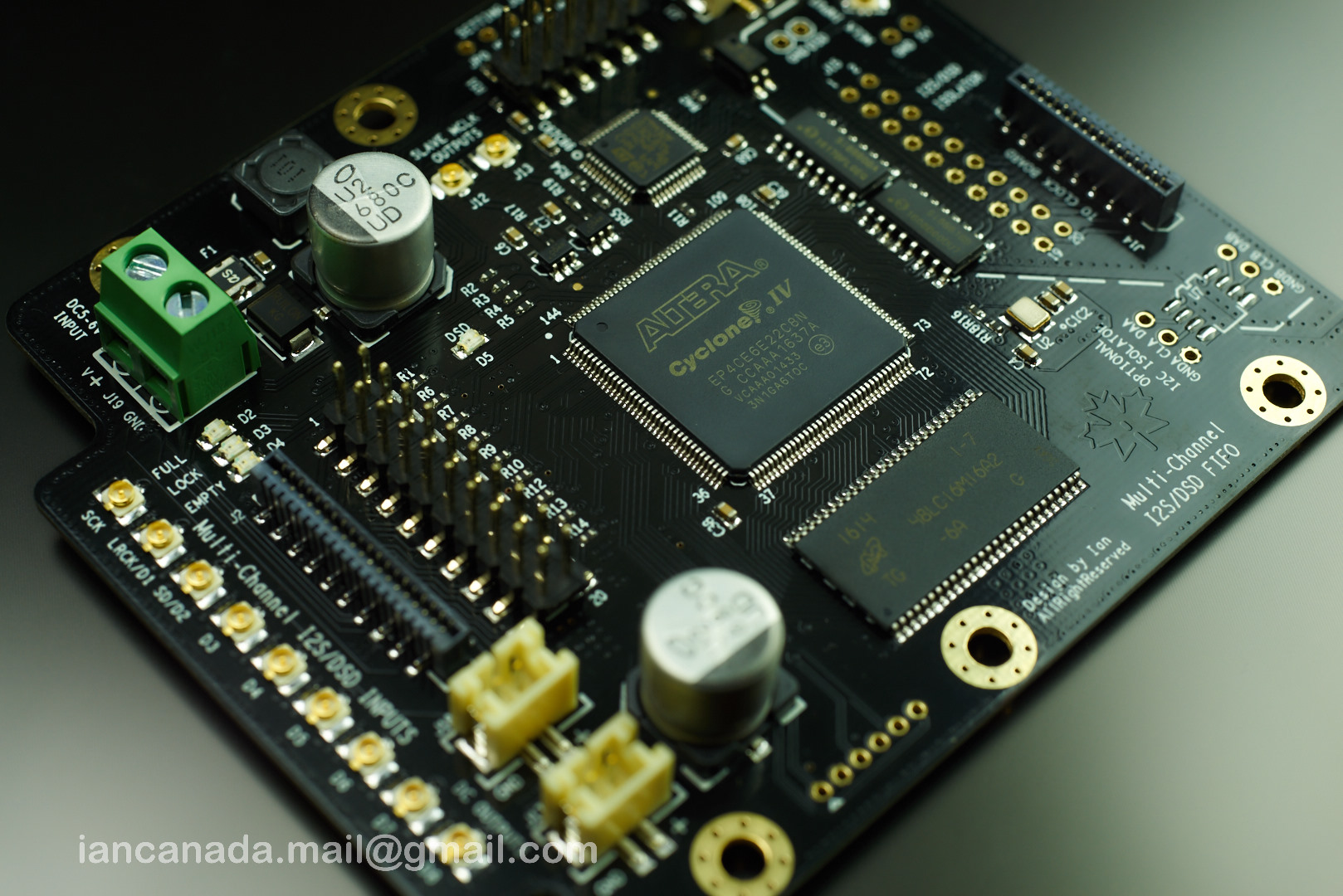

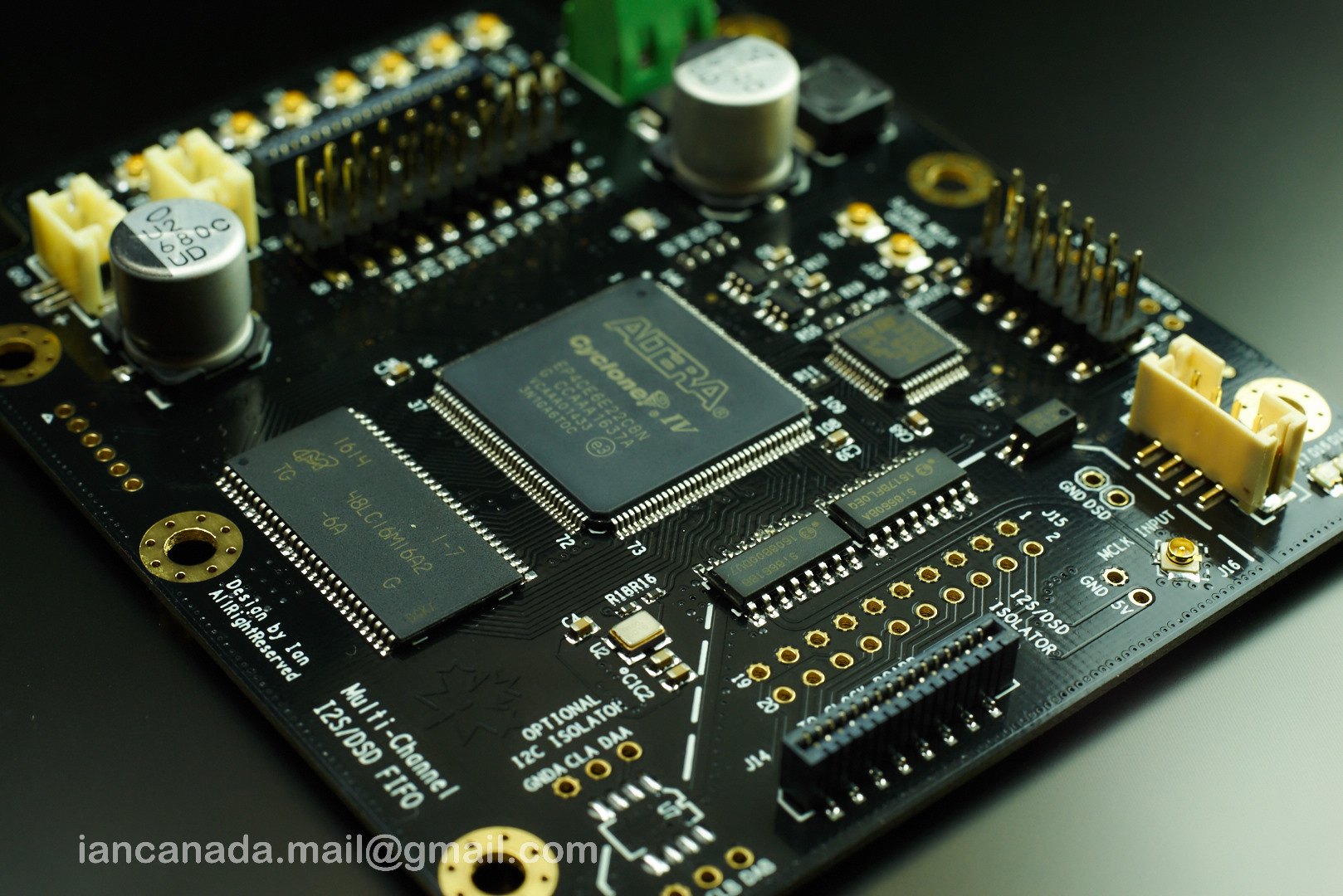

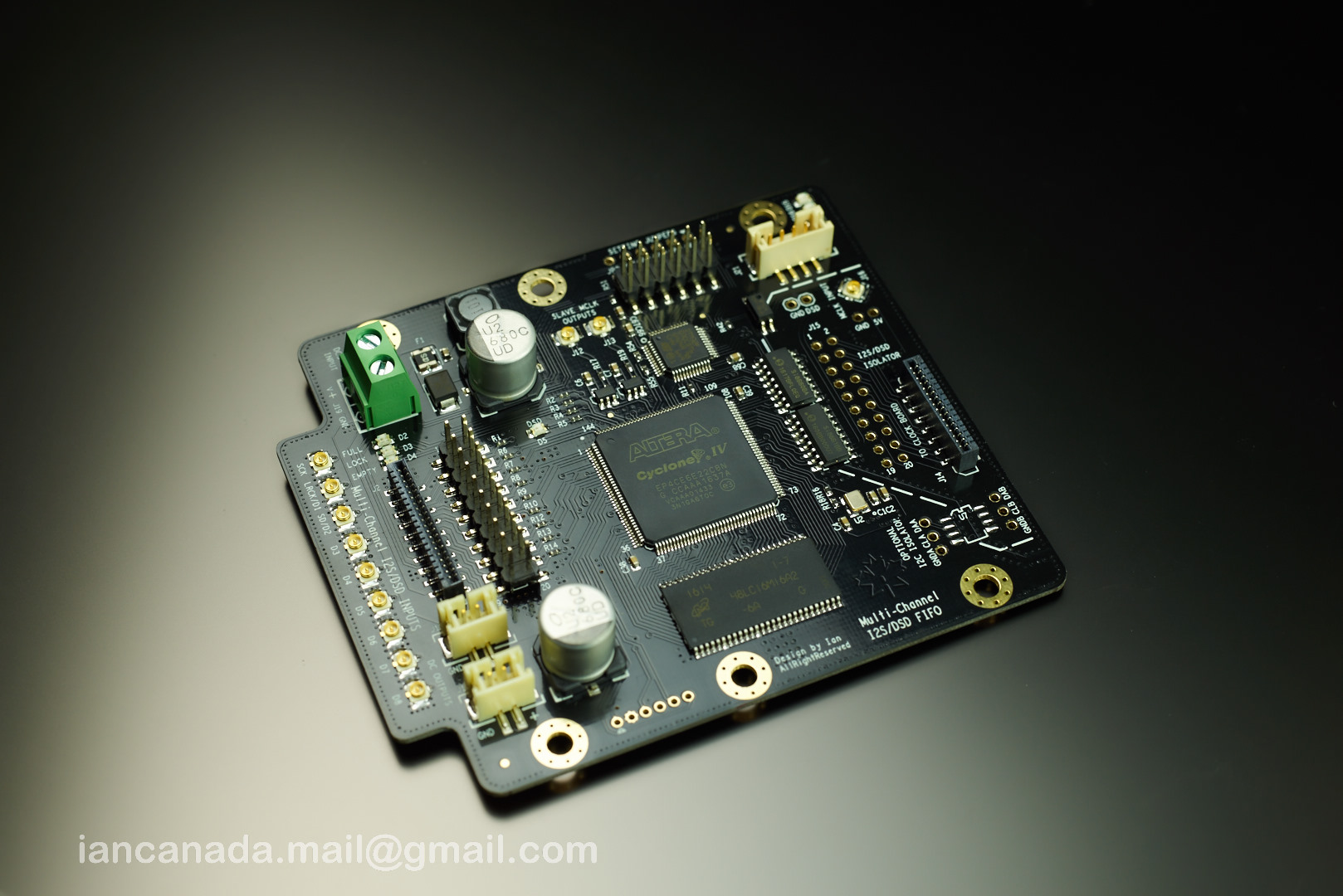

Awesome stuff Ian! I still have your FIFO II rocking my system and am looking to get your MC FIFO too 😀

Are you planning to update the I2StoPCM boards in future? Would it be possible to have two additional outputs (u.fl): 2 x continuous BCLK outputs?

I currently use your FIFO system to drive my AYA II (Pedja) DAC (dual-mono). The AYA II requires a separate, continuous BCLK for the TDA1541A DEM clock feed. At the moment, I have quite a bit of a hacked setup where I use 2 x I2StoPCM boards. One to drive PCM audio into DAC input. And the other I2StoPCM to supply continuous BCLK supply (set via jumpers) for DEM input 😛

Alternatively, I will use your MC FIFO and feed the AYA via spare MCLK outputs.

Awesome stuff Ian! I still have your FIFO II rocking my system and am looking to get your MC FIFO too 😀

Are you planning to update the I2StoPCM boards in future? Would it be possible to have two additional outputs (u.fl): 2 x continuous BCLK outputs?

I currently use your FIFO system to drive my AYA II (Pedja) DAC (dual-mono). The AYA II requires a separate, continuous BCLK for the TDA1541A DEM clock feed. At the moment, I have quite a bit of a hacked setup where I use 2 x I2StoPCM boards. One to drive PCM audio into DAC input. And the other I2StoPCM to supply continuous BCLK supply (set via jumpers) for DEM input 😛

Alternatively, I will use your MC FIFO and feed the AYA via spare MCLK outputs.

Hi,

Your dual PCM board project is awesome!

With special firmware, PCM board function can be integrated into MC FIFO kit. You will have enough SCK if so. We can talk about is later.

Regards,

Ian

It's fantastic result Ian, I was a little afraid about this flat (non coax; antena EMI catching? We read things as non specialist without understanding the limit of it) link between the Fifo and the clock board 😱 !

That's very handy for us to have populated the isolator stage on the FIFO board and to have upgraded the LDOs on the clock board 🙂

That's very handy for us to have populated the isolator stage on the FIFO board and to have upgraded the LDOs on the clock board 🙂

Last edited:

Awesome stuff Ian! I still have your FIFO II rocking my system and am looking to get your MC FIFO too 😀

Are you planning to update the I2StoPCM boards in future? Would it be possible to have two additional outputs (u.fl): 2 x continuous BCLK outputs?

I currently use your FIFO system to drive my AYA II (Pedja) DAC (dual-mono). The AYA II requires a separate, continuous BCLK for the TDA1541A DEM clock feed. At the moment, I have quite a bit of a hacked setup where I use 2 x I2StoPCM boards. One to drive PCM audio into DAC input. And the other I2StoPCM to supply continuous BCLK supply (set via jumpers) for DEM input 😛

Alternatively, I will use your MC FIFO and feed the AYA via spare MCLK outputs.

Have the PCM boards not a spare uf-l Bclk output at the botom of the board ??? So you use two AYA 2014 board ? Funny ! Would like to know if feeding the DEM clock is better than the normal way : I use all the Ian's stuffs on my AYA 2014 board as well (PCM board included) but quite happy with this typology, I didn't benchmark the rest of DEM re-clocking (a bit afraid of the jitter than the 74 flip/flop chip could introduce... , I use a smd silver mica cap instead = classic way))

Last edited:

Have the PCM boards not a spare uf-l Bclk output at the botom of the board ??? So you use two AYA 2014 board ? Funny ! Would like to know if feeding the DEM clock is better than the normal way : I use all the Ian's stuffs on my AYA 2014 board as well (PCM board included) but quite happy with this typology, I didn't benchmark the rest of DEM re-clocking (a bit afraid of the jitter than the 74 flip/flop chip could introduce... , I use a smd silver mica cap instead = classic way))

I have dual mono AYA so each AYA requires one bclk = one Ian i2stoPCM board. The other i2stoPCM board is dedicated to outpouring two continuous bclk for each AYA DEM (which is a bit of a waste of an board).

I never try classical way so I can't compared but DEM reclock has quiet background and is crystal clear.

Same for me but the classic way for the clock instead the dem-reclocck. ; this DAC is fantastic !🙂

@ Ian : please a photograph of the bottom of the lady 🙂

@ Ian : please a photograph of the bottom of the lady 🙂

Who cares about yet 'nother digital project board ... But: Jin .... dude ... that photography!! Nice Flickr page, man.

Now, work on a latest-n-greatest USB interface board and Canon EOS that puppy.

Now, work on a latest-n-greatest USB interface board and Canon EOS that puppy.

Who cares about yet 'nother digital project board ... But: Jin .... dude ... that photography!! Nice Flickr page, man.

Now, work on a latest-n-greatest USB interface board and Canon EOS that puppy.

I use SONY now 😀

Ian

The AD165 little core board is nice also on your Flickr album ... Could be very fun unpopulated as there are few parts and allowing both the posibility to use chemical smd cap as vias for more classic ones on the same traces area 🙂

Last edited:

I use SONY now 😀

Ian

pssst, you might get lynch by canikon users 😀

Hello Ian,

Is it possible to connect your S/PDIF board to the MC FIFO & MC CLOCK boards?

Thanks,

Sean

Is it possible to connect your S/PDIF board to the MC FIFO & MC CLOCK boards?

Thanks,

Sean

Hello Ian,

Is it possible to connect your S/PDIF board to the MC FIFO & MC CLOCK boards?

Thanks,

Sean

It's possible but the FW of S/PDIF board needs to be update.

Regards,

Ian

Ian,

Those boards look great. Cool photography too.

Unfortunately i'm not sure there is a multichannel DAC out there which matches your level of quality.

Please take the plunge and design a mutichannel DAC+IV 🙂

For multichannel source i think DIYINHK board is a candidate.

Those boards look great. Cool photography too.

Unfortunately i'm not sure there is a multichannel DAC out there which matches your level of quality.

Please take the plunge and design a mutichannel DAC+IV 🙂

For multichannel source i think DIYINHK board is a candidate.

.... and... I'M IRON-MAN !

(do you think DIYinkh makes good boards... common !)

I would ask the guy behind Buffallo to update his Bufallo board with the lastest ESS chips !

@Ian : would you re print some Clock Board II as well or update it with new LDOs or not any wisch for that one ? Some on shelf yet ?

(do you think DIYinkh makes good boards... common !)

I would ask the guy behind Buffallo to update his Bufallo board with the lastest ESS chips !

@Ian : would you re print some Clock Board II as well or update it with new LDOs or not any wisch for that one ? Some on shelf yet ?

Last edited:

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter