I have a dilemma with the controller pcb yet... I'll use an I2C isolator, the Si8605 and it has 2 sides, "A" and "B". Which side must point to the 5.0V arduino and which to the 3.3V DAC?

(I'm a little confused with the datasheet)

(I'm a little confused with the datasheet)

plans for I2s isolation and/or FLIP/FLOP

Zarandok,

Very nice project! Do you have plans for adding i2S isolation and flip/flops?

I guess the miniDSP i2S signal would benefit from it, as it is considered to be somewhat noisy in the I2S and not very well timed...?

Zarandok,

Very nice project! Do you have plans for adding i2S isolation and flip/flops?

I guess the miniDSP i2S signal would benefit from it, as it is considered to be somewhat noisy in the I2S and not very well timed...?

Thanks! I am considering at the time another layout with Si570 (I2C controlled programmable oscillator) and flip-flops. But I'm not sure that should I use rather single flip-flops (e.g. 74AUP1G79) or a 8x (e.g. Potato PO54G374A)...

Zarandok,

Very nice project! Do you have plans for adding i2S isolation and flip/flops?

I guess the miniDSP i2S signal would benefit from it, as it is considered to be somewhat noisy in the I2S and not very well timed...?

I used single flip-flops on my original AK4490 but my Rev.2 (Dual AK4493s, PCBs are in the fab. 🙂 ) will use the Potato part. It should easily outperform the 74AUP1G79s. It makes for a cleaner layout too.

Btw, I'll also be upgrading my Si570 to an Si544.. that should also be interesting.

Btw, I'll also be upgrading my Si570 to an Si544.. that should also be interesting.

Attachments

Very nice, thank you! You have take care about the trace lenghts too...🙂

One question: you are don't using a clock buffer, the DACs and the output MCLK to the receiver are directly connected to the clock. What's your consideration about that?

One question: you are don't using a clock buffer, the DACs and the output MCLK to the receiver are directly connected to the clock. What's your consideration about that?

The Si has very high current output. It can handle the load with ease. Heck, it could even handle the 6 x flip-flops + 2 x AK4490s + XMOS receiver in the previous board.

In applications like Ian's where he has no control over what will be driven by his board it is a good idea to use a clock buffer.

In my case, I knew exactly what I would be driving so I chose to keep it simple.

In my case, I knew exactly what I would be driving so I chose to keep it simple.

Which Si570 (544) output type do we need?

"LVPECL, LVDS, CML, HCSL, CMOS, DualCMOS"

Do you simply connect the OE pin to Vdd (if OE polarity: high)?

"LVPECL, LVDS, CML, HCSL, CMOS, DualCMOS"

Do you simply connect the OE pin to Vdd (if OE polarity: high)?

Last edited:

CMOS (or even better dual CMOS if you can find it - you might be able to omit the clock buffer if 2 outputs are enough for your use case).

If you don't need to be able to enable/disable the Si you can leave the OE pin floating (its internally pulled high or low so as to keep the Si enabled).

If you don't need to be able to enable/disable the Si you can leave the OE pin floating (its internally pulled high or low so as to keep the Si enabled).

I like the option of bypassing the clock buffer and the OE options.

I would like a lot more bypassing on the Si570/544 and the Potato chip (in the form of several different value 0603 caps).

And more GND vias.

I would like a lot more bypassing on the Si570/544 and the Potato chip (in the form of several different value 0603 caps).

And more GND vias.

I'm considering what other clocks can be use with my Si5xx footprint, perhaps design an universal pattern. But the NDK clocks are simply too small, unfortunatelly not possible if I don't want to get a short with the bigger 6 pin examples. Alternatives are the Crystek C33xx and CCDH-575 models, they have about the same size, but only 4 pads.

The Si clocks have relativ high phase noise, and are sentitive to the power supply (experience of Ian) regardless to the good PSRR value. That's why I thinking about alternatives....

The Si clocks have relativ high phase noise, and are sentitive to the power supply (experience of Ian) regardless to the good PSRR value. That's why I thinking about alternatives....

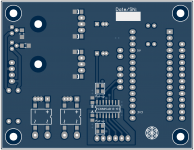

Attachments

Last edited:

- Home

- Source & Line

- Digital Line Level

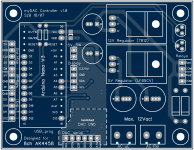

- AK4458 multichannel DAC with I2S input