You have ufl connectors already soldered in or solder tabs where you can solder wires.

There is no header that goes to the dac.

There is no header that goes to the dac.

Greetings all. I have an Amanero/Hermes/Cronus with a BIII DAC. USB to I2S in async plays and sounds great. Plays DSD and hi rez files. However it won't play in sync. Just trying standard redbook for now in sync.

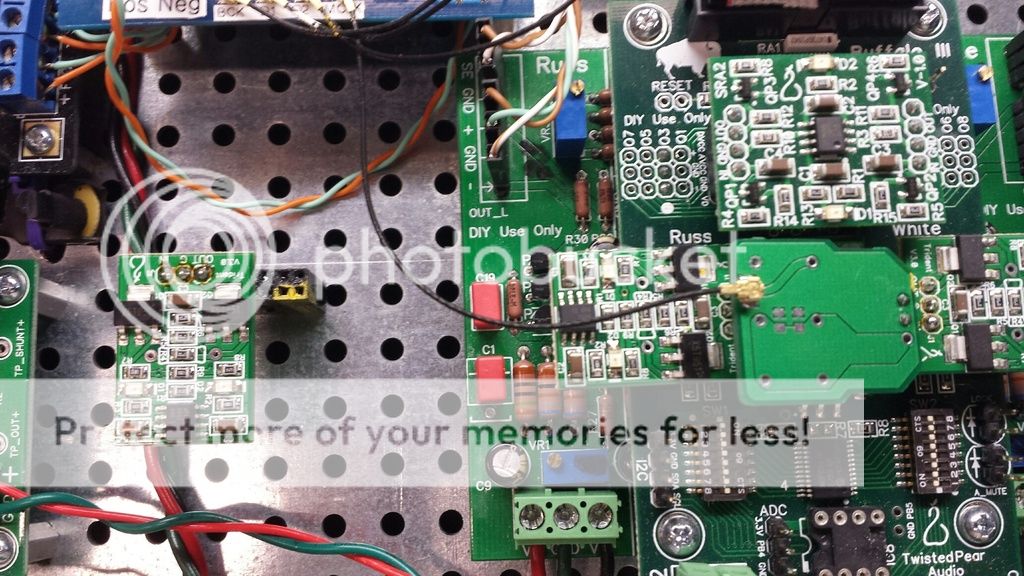

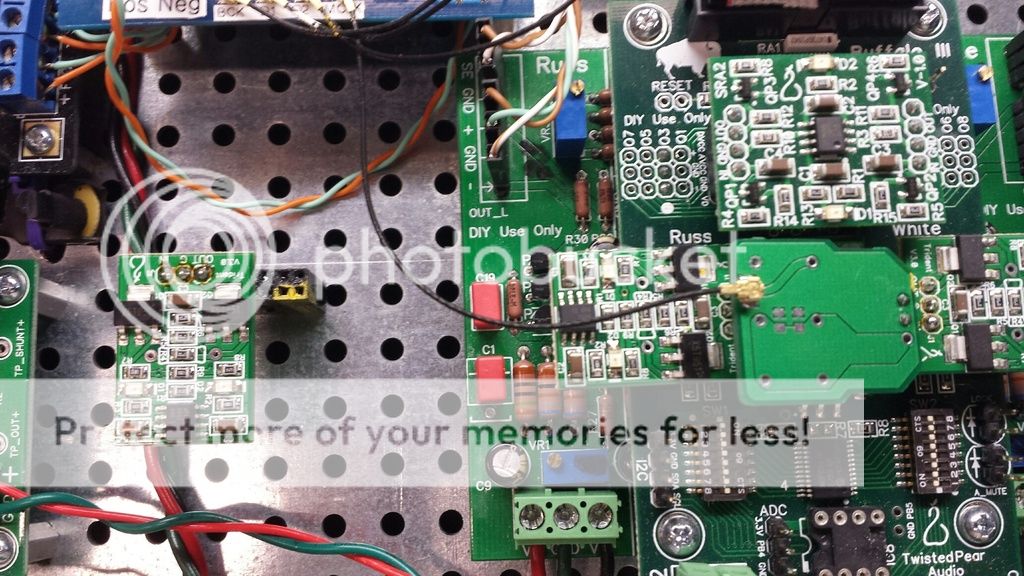

I am all U.fl to Sidecar and clock. I have v1.0.2 BIII so I have header on top of board for external clock connection. Resistors mounted in R1-R7. Trident for BIII clock removed, OSF off, tried all DPLL settings. Amanero from TP so flashed properly. I tried another Amanero I flashed to slave and same thing, plays in async but not in sync. Cronus powered by Salas 5v PS. Tried upping voltage, no help. I have a different USB to I2S module and it will play in sync so I am looking for help in diagnosing why no sync with the Cronus.

Reading some of the other posts, I put a scope on the CS pin and the signal doesn't change regardless of clock divider jumper position. I'm no tech, just have enough knowledge to be dangerous...lol... so unsure if I am testing correctly.

This is the setup, using Ian's BIII clock board to connect clock. No clock is attached to Ian's board, just using it as U.fl to clock header. All U.fl cables just under 4"/100mm. It's a friends DAC and I had to give it back so he can at least listen to it using SPDIF. But I tried the Amanero/Hermes/Cronus in my BIII DAC and it plays great in async but won't play in sync, so once it is fixed in my DAC it should work in his.

I made a park position for the Trident so it would not be lost.

I am all U.fl to Sidecar and clock. I have v1.0.2 BIII so I have header on top of board for external clock connection. Resistors mounted in R1-R7. Trident for BIII clock removed, OSF off, tried all DPLL settings. Amanero from TP so flashed properly. I tried another Amanero I flashed to slave and same thing, plays in async but not in sync. Cronus powered by Salas 5v PS. Tried upping voltage, no help. I have a different USB to I2S module and it will play in sync so I am looking for help in diagnosing why no sync with the Cronus.

Reading some of the other posts, I put a scope on the CS pin and the signal doesn't change regardless of clock divider jumper position. I'm no tech, just have enough knowledge to be dangerous...lol... so unsure if I am testing correctly.

This is the setup, using Ian's BIII clock board to connect clock. No clock is attached to Ian's board, just using it as U.fl to clock header. All U.fl cables just under 4"/100mm. It's a friends DAC and I had to give it back so he can at least listen to it using SPDIF. But I tried the Amanero/Hermes/Cronus in my BIII DAC and it plays great in async but won't play in sync, so once it is fixed in my DAC it should work in his.

I made a park position for the Trident so it would not be lost.

Last edited:

It might be beneficial to buffer the clock signal - the clocks on the Cronus are already driving a few gates.

Honestly I would suggest staying async as you avoid any possibility of DAC supply and I/O timing issues. The DAC supplies have to come up in the correct sequence relative to the master clock being applied to the DAC. This may not be simple to achieve.

Honestly I would suggest staying async as you avoid any possibility of DAC supply and I/O timing issues. The DAC supplies have to come up in the correct sequence relative to the master clock being applied to the DAC. This may not be simple to achieve.

Thanks for the input Russ.

Could I try powering the Cronus with the DAC's Placid HD? How much more mA will I need? I installed larger heat sinks on the Placid HD, 2.5" IIRC.

Could I try powering the Cronus with the DAC's Placid HD? How much more mA will I need? I installed larger heat sinks on the Placid HD, 2.5" IIRC.

I have a different USB to I2S module and it will play in sync...

Is there a significant difference in sound by switching to synchronous?

Is there a significant difference in sound by switching to synchronous?

No.

Thanks for the input Russ.

Could I try powering the Cronus with the DAC's Placid HD? How much more mA will I need? I installed larger heat sinks on the Placid HD, 2.5" IIRC.

You could - but I suspect that would not be the heart of the issue. You should plan for around 100ma.

Hello guys!

I start writing here because on tp forum I am talking alone for a week. I started worrying about Russ and Brian until yesterday when I saw Russ posts here.

To be short I have a problem with cronus combo.

The clocks on it are 45&49mhz.

When I run the dac async everything works fine. The problem comes in when I connect b3 mck to cronus mck. I get double the pitch for what I am streaming and It won`t stream 384khz files.

Last week a new cronus combo arrived. After I replaced the old one with the new one the problem kept showing up.

After that I have disoldered the 100mhz vcxo that is on b3.

Now the dac plays normally in sync until 192khz files. If I want to stream 384khz files I have to turn off oversampling filter on b3.

Is this normal?

Having in house some IDT 74FCT38072SDCGI 200mhz clock buffers I resoldered today the 100mhz vcxo back again on b3 board but left it unpowered and put a clock buffer between cronus mck output and b3 mck input.

Guess what now I can stream files until 192khz in sync without any problem or double pitch. For 384khz I still have to turn off oversampling filter.

It may be that others managed to get the cronus/b3 combo working sync without any buffer but for me was a very long road to dyscover the problem behind.

I am very curious if there are others that are running cronus/b3 in sync and stream without problems 384khz files.

I start writing here because on tp forum I am talking alone for a week. I started worrying about Russ and Brian until yesterday when I saw Russ posts here.

To be short I have a problem with cronus combo.

The clocks on it are 45&49mhz.

When I run the dac async everything works fine. The problem comes in when I connect b3 mck to cronus mck. I get double the pitch for what I am streaming and It won`t stream 384khz files.

Last week a new cronus combo arrived. After I replaced the old one with the new one the problem kept showing up.

After that I have disoldered the 100mhz vcxo that is on b3.

Now the dac plays normally in sync until 192khz files. If I want to stream 384khz files I have to turn off oversampling filter on b3.

Is this normal?

Having in house some IDT 74FCT38072SDCGI 200mhz clock buffers I resoldered today the 100mhz vcxo back again on b3 board but left it unpowered and put a clock buffer between cronus mck output and b3 mck input.

Guess what now I can stream files until 192khz in sync without any problem or double pitch. For 384khz I still have to turn off oversampling filter.

It may be that others managed to get the cronus/b3 combo working sync without any buffer but for me was a very long road to dyscover the problem behind.

I am very curious if there are others that are running cronus/b3 in sync and stream without problems 384khz files.

Hello guys!

.....................and put a clock buffer between cronus mck output and b3 mck input.

Hello schultzsch!

Congrats on your success! I had been following your thread at TP hoping to learn a solution to my issue.

Can you show me exactly how you implemented the buffer? I'm not as smart as you are, need pictures, instructions. lol

Hello ScompRacer!

I do not recommend using the same part as me because being a dual channel output you have to load both outputs equally for best performance. It could work well on a dual mono b3.

Here is the datasheet:

http://www.idt.com/document/dst/74fct38072s-datasheet

My chip is an 8 pin soic. You need to do the following connections:

pin 1 : connect to 3.3v from cronus

pin 2 : connect to 3.3v from cronus

pin 3 : connect here cronus mck output

pin 4 : ground

pin 5 : ground

pin 6 : first mck output that goes to first buffalo dac

pin 7 : second mck output that goes to second dac if you have dualmono if not leave it open

pin 8 : ground

For simplicity you cand tie toghether pin 1&2. They are both VDD. Do not power up the chip from more than 3.3V.

You need a 10nf decoupling cap between pin 1&2(VDD) and ground

If you are using wires/traces longer than 1 inch you need to connect some 33r resistors in series with buffer outputs and b3 dac/s.

For me this is not a solution because with this implementation you create a beautiful ratsnest in clock signal way having 100mhz signal that flies all over the place.But for testing purpose it works.

It was better if those buffers were implemented on the cronus board but unfortunately they are not! Maybe the next revision of boards will have on them some buffers.

I repeat .. I used dual channel buffers because I had them in house.

I do not recommend using the same part as me because being a dual channel output you have to load both outputs equally for best performance. It could work well on a dual mono b3.

Here is the datasheet:

http://www.idt.com/document/dst/74fct38072s-datasheet

My chip is an 8 pin soic. You need to do the following connections:

pin 1 : connect to 3.3v from cronus

pin 2 : connect to 3.3v from cronus

pin 3 : connect here cronus mck output

pin 4 : ground

pin 5 : ground

pin 6 : first mck output that goes to first buffalo dac

pin 7 : second mck output that goes to second dac if you have dualmono if not leave it open

pin 8 : ground

For simplicity you cand tie toghether pin 1&2. They are both VDD. Do not power up the chip from more than 3.3V.

You need a 10nf decoupling cap between pin 1&2(VDD) and ground

If you are using wires/traces longer than 1 inch you need to connect some 33r resistors in series with buffer outputs and b3 dac/s.

For me this is not a solution because with this implementation you create a beautiful ratsnest in clock signal way having 100mhz signal that flies all over the place.But for testing purpose it works.

It was better if those buffers were implemented on the cronus board but unfortunately they are not! Maybe the next revision of boards will have on them some buffers.

I repeat .. I used dual channel buffers because I had them in house.

Last edited:

Hello guys!

I am very curious if there are others that are running cronus/b3 in sync and stream without problems 384khz files.

Absolutely, I am right doing so right now.

I know Miero and a few others have as well.

Hello ScompRacer!

It was better if those buffers were implemented on the cronus board but unfortunately they are not! Maybe the next revision of boards will have on them some buffers.

Actually this was a design choice because the MCK pin at the B3 header is not necessarily intended to be an output only pin.

It was intended to potentially allow the clock to be sourced from the DAC itself responding the CS signal. 🙂

One thing to try would be to short the two termination Rs at the XOs on the Cronus and instead just (completely optionally) add one series termination R at the mck pad of the B3 header (say 21R but it should work even without any)

Last edited:

I will try to bypass R8 & R9 on cronus board and insert another 33r on the mck line that goes to b3

You still did not respond to one question.

If I have 45&49mhz clocks on cronus and run the dac sync, is it possible to stream 384khz files with the oversampling filter on?

You still did not respond to one question.

If I have 45&49mhz clocks on cronus and run the dac sync, is it possible to stream 384khz files with the oversampling filter on?

I will try to bypass R8 & R9 on cronus board and insert another 33r on the mck line that goes to b3

You still did not respond to one question.

If I have 45&49mhz clocks on cronus and run the dac sync, is it possible to stream 384khz files with the oversampling filter on?

Absolutely - you just have to open up the DPLL bandwidth so that it free-wheels.

If you are using custom firmware always read back the register you think you set to be sure you actually did. 🙂

Very strange.

I am sure that the register changes because I can hear the difference on low sample rate files such as 44.1khz where the effect is something like a low pass filter, the sound it's not so shiny with the filter off. Another thing that confirms osf turning on or off is to stream dsd. With osf off the dac won`t stream dsd.

So for me the OSF register shifts correctly.

The dpll bandwidth is setup as you described but still no lock for 384khz files with oversampling filter on.

I am sure that the register changes because I can hear the difference on low sample rate files such as 44.1khz where the effect is something like a low pass filter, the sound it's not so shiny with the filter off. Another thing that confirms osf turning on or off is to stream dsd. With osf off the dac won`t stream dsd.

So for me the OSF register shifts correctly.

The dpll bandwidth is setup as you described but still no lock for 384khz files with oversampling filter on.

That's not really something you can check by ear 🙂 Read the register back to be sure you are doing what you need to do. Also I am not talking about the filter - I am talking about the bandwidth,

Last edited:

So what that gets down to just this - I absolutely have no way to know what will work with your custom firmware - I only have my own to test.

Ok you are right.

Since I am not a programmer and I do not know how to read register status I will take the easy way and switch my controller with yours. This way we will speak the same language.

Since I am not a programmer and I do not know how to read register status I will take the easy way and switch my controller with yours. This way we will speak the same language.

Ok, I pulled off the i2c strip connector that arrives to b3 from my controller board and connected in b3 original atiny.

The dac won`t lock to 384khz signals no matter if switch 2 position 4 (which oversampling filter and reclocking) is on or off.

It will also play dsd files no matter of sw2:4 position and this seems strange to me because es9018 needs oversampling filter on to play dsd files.

The dac won`t lock to 384khz signals no matter if switch 2 position 4 (which oversampling filter and reclocking) is on or off.

It will also play dsd files no matter of sw2:4 position and this seems strange to me because es9018 needs oversampling filter on to play dsd files.

- Home

- More Vendors...

- Twisted Pear

- Cronus - It's about time.