Miro, All,

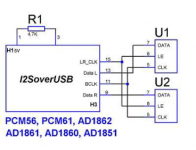

Seeking your opinions on reclocking. Most reclock solutions out there will be placed before the i2s input on the DAC board - and then afterwards gets divided left and right via the shift registers. But would it not be better to do the channel splitting first, and then do the reclocking. So the schema would look something like:

bck and lrck in to the flip flop via 2 inputs each

split data taken after the shift registers L and R goes into another 2 lanes

Alignment via MCK

and then BCK, LRCK and Data L and Data R go to each DAC chip.

So the reclock is done last thing just before the DAC chips?

What do you think?

Seeking your opinions on reclocking. Most reclock solutions out there will be placed before the i2s input on the DAC board - and then afterwards gets divided left and right via the shift registers. But would it not be better to do the channel splitting first, and then do the reclocking. So the schema would look something like:

bck and lrck in to the flip flop via 2 inputs each

split data taken after the shift registers L and R goes into another 2 lanes

Alignment via MCK

and then BCK, LRCK and Data L and Data R go to each DAC chip.

So the reclock is done last thing just before the DAC chips?

What do you think?

Sure, this is a good option. Has nice clocks.

Richard, Abraxelito recommends CM6631A for his DACs.

Richard, Abraxelito recommends CM6631A for his DACs.

Last edited:

Yep, that's true, and I've used that feature in a PCM63 dac I have here, plus I have a spare JLsounds board as well. However, the source I'm thinking of is an SD card player so there is no such options with that.

I am thinking I will first try a reclock before the shift register, and if there is any hint of difference, I will to do it after the split. Interested in any other comments you might have.

Fran

I am thinking I will first try a reclock before the shift register, and if there is any hint of difference, I will to do it after the split. Interested in any other comments you might have.

Fran

I'm curious to learn what in the shift register will introduce timing issues? It seems like a pretty robust synchronous thing locked to your new clock.

@woodturner-fran

... the only thing you can improve with a new clock is LRCK (for AD1862 and AD1865). Only this signal is directly responsible for the resulting sound. (of course, BCK and DATA must be reasonably aligned to avoid bit loss, but in most cases this is fulfilled)

... the only thing you can improve with a new clock is LRCK (for AD1862 and AD1865). Only this signal is directly responsible for the resulting sound. (of course, BCK and DATA must be reasonably aligned to avoid bit loss, but in most cases this is fulfilled)

Thanks Miro - that is really useful to know. I'll knock up a board tomorrow night hopefully and give it a whirl. This thing sounds so good right now, any improvement is well into bonus territory.

A few friends here are embarking on their own builds..... I think demand for AD1862 chips is going up!

A few friends here are embarking on their own builds..... I think demand for AD1862 chips is going up!

I wasn't kidding with starting this thread guys, AD1862 is the real deal 😀

Buy in stock while the price is low. It may happen to cost >70USD as it was with the PCM1704.

Buy in stock while the price is low. It may happen to cost >70USD as it was with the PCM1704.

The very high quality sound and simplicity of building this AD1862 DAC is very appealing to me. We have seen several options for I/V and output stage experiments with excellent results. For me, I didn’t want to complicate the layout with the addition of external reclocking, that’s just me though. If you can squeeze out a bit more performance going this route, I say go for it! 😉

@woodturner-fran

... the only thing you can improve with a new clock is LRCK (for AD1862 and AD1865). Only this signal is directly responsible for the resulting sound. (of course, BCK and DATA must be reasonably aligned to avoid bit loss, but in most cases this is fulfilled)

IME on other projects reclocking all three has distinct SQ benefits - with digital, timing is everything!

For me, I didn’t want to complicate the layout with the addition of external reclocking, that’s just me though.

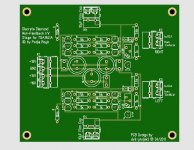

Compact, even simpler - no shift registers - and reclocked i2s inputs... Just add your choice of output stage and power supplies.

I'm wondering if it might be possible to do a version of the board on the same footprint but with Pedja's IV stage incorporated.

Last edited:

You could also use this PCM-Board from Ian or may be better wait for Andrea Mori's FIFO. If he can manage the source decoupling (proof of concept), then there is hardly a better solution.

A quick bit of research has turned up that there was previously a group buy for PCBs to build Pedja's circuit and gerber files were made available. I think I'll order a small batch from JLC...

I'll happily obtain some for others if there is any interest but I think it would be sensible to restrict that to Europe as with shipping costs it will probably be more cost efficient to order boards direct from JLC for citizens of US/Aus/etc.

I've attached a zip file with the gerber package.

I checked Mouser and it looks like the only part not available from them is the single 2SK170 that is required.

I'll happily obtain some for others if there is any interest but I think it would be sensible to restrict that to Europe as with shipping costs it will probably be more cost efficient to order boards direct from JLC for citizens of US/Aus/etc.

I've attached a zip file with the gerber package.

I checked Mouser and it looks like the only part not available from them is the single 2SK170 that is required.

Attachments

Would you have a link to that nautiboy (the thread)?

Did a search there, but couldn't find it. I'm obviously using crappy search terms!

Trying to bone up on these!

Did a search there, but couldn't find it. I'm obviously using crappy search terms!

Trying to bone up on these!

Compact, even simpler - no shift registers - and reclocked i2s inputs... Just add your choice of output stage and power supplies.

I'm wondering if it might be possible to do a version of the board on the same footprint but with Pedja's IV stage incorporated.

I love your stacked board solution NB, have you powered up yet?

Pedja’s OPA861 I/V output stage is fantastic also 😉

OK, found it....... need to develop my search term abilities as well as everything else!

Would you have a link to that nautiboy (the thread)?

Did a search there, but couldn't find it. I'm obviously using crappy search terms!

Trying to bone up on these!

does the gerber file of Pedja's OPA861 I/V output stage exit?

I would like to give a try.

Buy the way, if using JLsound USB board to skip shift registers and using 2 Miro's PCB for right and left channel separately with own power supplies, will it be better for lowering cross talk between channels?

(as the pcb is relatively small and cheap, it may only cost several dollars more for one additional PCB, but will have one additional power supply)

I would like to give a try.

Buy the way, if using JLsound USB board to skip shift registers and using 2 Miro's PCB for right and left channel separately with own power supplies, will it be better for lowering cross talk between channels?

(as the pcb is relatively small and cheap, it may only cost several dollars more for one additional PCB, but will have one additional power supply)

I love your stacked board solution NB, have you powered up yet?

Pedja’s OPA861 I/V output stage is fantastic also 😉

did you finally removed the feedback between it and the output ? (even better!)

OK, found it....... need to develop my search term abilities as well as everything else!

Good stuff Fran. I'm guessing there's a thread on it that led to the GB but I didn't have tme to search more this morning.

I love your stacked board solution NB, have you powered up yet?

Cheers Vunce. Not powered up yet - this project is down my to do list at about #4 or 5... I've already sent some PCBs to a couple of guys active on this thread and i suspect they may get it up and running

before me.

before me.Your welcome to the gerber files if you want to experiment - obviously 'untested'.

- Home

- Source & Line

- Digital Line Level

- DAC AD1862: Almost THT, I2S input, NOS, R-2R