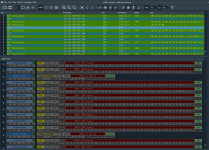

Hi everyone. I just re-implemented the UAC2 in another hardware platform. If you remember my last implementation is based on STM32, which is quite annoying to work with, involving a lot of hacking and tinkering. That project is quite incomplete also as DSD/DoP playback could not (or very difficult) be supported with peripherals on STM32, without core in the datapath, causing very high power consumption and instability. The new implementation is based on FX2LP, almost the stantard choice to communicate between programmable logic (FPGA/CPLD) and PC by USB. The core is completely out of the datapath, all logics are carried on the CPLD including buffering. Currently it can support up to PCM 768k/32bit 2ch playback and DoP detection (not playback yet). The project is still work in progress to be open-sourced, but I would like to share some progress with you.

Attachments

Hi,

Makes sense if you target multichannel high sample rate applications. For example, I can't output 768kHz on PIC32MZ due to peripheral limitations, to do so it would require CPLD too.

But this would make a nice eval board for many other applications, not only limited to audio.

How the MCU is programmed? Does it need external programmer?

That's a bit surprising, there are many examples of implementation on STM32 🙂STM32, which is quite annoying to work with, involving a lot of hacking and tinkering.

That is interesting but quite expensive, it is really possible to do on MCU where all the hardware is already there and do the transfers using DMA.The core is completely out of the datapath, all logics are carried on the CPLD including buffering.

Makes sense if you target multichannel high sample rate applications. For example, I can't output 768kHz on PIC32MZ due to peripheral limitations, to do so it would require CPLD too.

But this would make a nice eval board for many other applications, not only limited to audio.

Don't forget to add 5.1k resistors to CCx pins of USB-C connector.I just re-implemented the UAC2 in another hardware platform.

How the MCU is programmed? Does it need external programmer?

Yes there are, but seems they also require external logics to achieve DSD playing. I meant to say without external logic DSD/DoP will be difficult.That's a bit surprising, there are many examples of implementation on STM32

If cost is a concern have a look of Lattice LCMXO2 series. They provide 1-2k LUTs with fraction of the price compare to similar models from Intel/Altera. The current design costs around 450 LEs which can fit into an EPM570. Solutions with other MCUs like Amanero or XMOS uses an EPM240 or XC2C64 for re-clocking anyway, so that should not be a huge increase in cost.That is interesting but quite expensive, it is really possible to do on MCU where all the hardware is already there and do the transfers using DMA.

Makes sense if you target multichannel high sample rate applications. For example, I can't output 768kHz on PIC32MZ due to peripheral limitations, to do so it would require CPLD too.

But this would make a nice eval board for many other applications, not only limited to audio.

The MCU is programmed through USB directly, with Cypress USB Control Center. If SDA of external EEPROM is disconnected while booting the chip automatically boots into factory mode in which you can program the EEPROM by reconnecting SDA.Don't forget to add 5.1k resistors to CCx pins of USB-C connector.

How the MCU is programmed? Does it need external programmer?

I do it in my project York without external logic:Yes there are, but seems they also require external logics to achieve DSD playing. I meant to say without external logic DSD/DoP will be difficult.

https://github.com/eclipsevl/york_p..._pic32mz_uac2_osfw.X/src/drivers/usb/usb_PL.c

Note: this is not main branch of my firmware and the DoP detection code is not written by me. The author is mentioned in the header.

Function usb_PL_DoP_Recognition() is called after start of the stream to determine if it is PCM or DoP. It does not run constantly.

The data transfer is done using DMA.

I'm using both STM32F7 and H7 SAI and processing of DSD is very similar to PCM. DoP is slightly more complex but not much. IME most complication with DSD/DoP comes from muting as some players send zero data as silence instead of DSD silence. This leads to DC and pops at output if not muted properly. STM32F7 SAI has some limitations with audio clock handling but these are fixed in STM32H7 SAI. With 45M/49M clocks both can do 768k/32 PCM. H7 can do DSD1024 but F7 is limited to DSD256.Yes there are, but seems they also require external logics to achieve DSD playing. I meant to say without external logic DSD/DoP will be difficult.

What peripheral on the STM32 do you use for 2ch DSD output? 2 data channels of a SAI? Thanks.processing of DSD is very similar to PCM

IIRC the DoP data comes interleaved in channel but DMA for peripherals only deals with continuous data, so you have to manually copy the data to two seperate buffers right? This have to be done by the core so I am expecting the power consumption to be quite high. Did you measure the temperature or current the chip is consuming? H7 runs faster but does not come with integrated USB PHY which is a big shame. Also I have heard of some issues with cache mess with DMA in Cortex-M7 devices, have you encouter any problem of this kind?I'm using both STM32F7 and H7 SAI and processing of DSD is very similar to PCM. DoP is slightly more complex but not much. IME most complication with DSD/DoP comes from muting as some players send zero data as silence instead of DSD silence. This leads to DC and pops at output if not muted properly. STM32F7 SAI has some limitations with audio clock handling but these are fixed in STM32H7 SAI. With 45M/49M clocks both can do 768k/32 PCM. H7 can do DSD1024 but F7 is limited to DSD256.

How do you recognize native DSD streams? I have not dig deep into this topic yet.I'm using both STM32F7 and H7 SAI and processing of DSD

Yep, this one indeed requires constant monitoring of the stream and switching to 0xAA output if zeros stream is detected.most complication with DSD/DoP comes from muting as some players send zero data as silence instead of DSD silence.

Two interfaces running synchronouslyWhat peripheral on the STM32 do you use for 2ch DSD output? 2 data channels of a SAI? Thanks.

Two synchronized SAI data channels.What peripheral on the STM32 do you use for 2ch DSD output? 2 data channels of a SAI?

You can achieve required data streams for peripherals using combination of multiple DMA channels.IIRC the DoP data comes interleaved in channel but DMA for peripherals only deals with continuous data

In Linux I've done this using an alternate setting with RAW data format and adding VID/PID to https://github.com/torvalds/linux/blob/master/sound/usb/quirks.c. I haven't implemented an ASIO driver so only DoP in Windows.How do you recognize native DSD streams? I have not dig deep into this topic yet.

Have not measured this with DoP. IIRC normal current consumption is about 150mA.Did you measure the temperature or current the chip is consuming?

It is quite easy to add an external USB PHY. Cache issues can be solved by RTFM.H7 runs faster but does not come with integrated USB PHY which is a big shame. Also I have heard of some issues with cache mess with DMA in Cortex-M7 devices, have you encouter any problem of this kind?

I measured the current consumption of STM32H7 (@550MHz). With PCM playing (any sample rate) current consumption is about 190mA. With DoP256 current consumption is about 195mA. So not much of an impact.Did you measure the temperature or current the chip is consuming?

The xDuoo one, VID/PID is 152A/8807Which drivers are you using?

This project is cool. The DSD and DOP module seems not work properly at present.

It might have Endian issue.

It might have Endian issue.

Below changes in dsd_master.v make the DOP and DSD work.

assign ch1_out = ch1_tx_reg[31];

assign ch2_out = ch2_tx_reg[31];

.....................................................................................................................

STATE_WAIT_DOP,

STATE_XFER_DOP: begin

case (req_count)

3'd0: next_ch1_data_in_reg[23:16] = data_in[15:8];

3'd1: next_ch1_data_in_reg[31:24] = data_in[7:0];

3'd4: next_ch1_data_in_reg[7:0] = data_in[15:8];

3'd5: next_ch1_data_in_reg[15:8] = data_in[7:0];

3'd2: next_ch2_data_in_reg[23:16] = data_in[15:8];

3'd3: next_ch2_data_in_reg[31:24] = data_in[7:0];

3'd6: next_ch2_data_in_reg[7:0] = data_in[15:8];

3'd7: next_ch2_data_in_reg[15:8] = data_in[7:0];

STATE_WAIT_DSD,

STATE_XFER_DSD: begin

case (req_count[1:0])

2'd0: next_ch1_data_in_reg[31:16] = {data_in[7:0],data_in[15:8]};

2'd1: next_ch1_data_in_reg[15:0] = {data_in[7:0],data_in[15:8]};

2'd2: next_ch2_data_in_reg[31:16] = {data_in[7:0],data_in[15:8]};

2'd3: next_ch2_data_in_reg[15:0] = {data_in[7:0],data_in[15:8]};

............................................................................................................................

next_ch1_tx_reg = ch1_tx_reg << 'h1;

next_ch2_tx_reg = ch2_tx_reg << 'h1;

test with es9038q2m DAC

result:

1,DSD test with ASIO driver up to DSD512.

2,DOP test withh ASIO and WASAPI up to DSD256 (DOP512 with noise,may be cpld timing constrains issue)

3,DOP not work stable some times no sound output. there are pop and crack sound output while switch music.

assign ch1_out = ch1_tx_reg[31];

assign ch2_out = ch2_tx_reg[31];

.....................................................................................................................

STATE_WAIT_DOP,

STATE_XFER_DOP: begin

case (req_count)

3'd0: next_ch1_data_in_reg[23:16] = data_in[15:8];

3'd1: next_ch1_data_in_reg[31:24] = data_in[7:0];

3'd4: next_ch1_data_in_reg[7:0] = data_in[15:8];

3'd5: next_ch1_data_in_reg[15:8] = data_in[7:0];

3'd2: next_ch2_data_in_reg[23:16] = data_in[15:8];

3'd3: next_ch2_data_in_reg[31:24] = data_in[7:0];

3'd6: next_ch2_data_in_reg[7:0] = data_in[15:8];

3'd7: next_ch2_data_in_reg[15:8] = data_in[7:0];

STATE_WAIT_DSD,

STATE_XFER_DSD: begin

case (req_count[1:0])

2'd0: next_ch1_data_in_reg[31:16] = {data_in[7:0],data_in[15:8]};

2'd1: next_ch1_data_in_reg[15:0] = {data_in[7:0],data_in[15:8]};

2'd2: next_ch2_data_in_reg[31:16] = {data_in[7:0],data_in[15:8]};

2'd3: next_ch2_data_in_reg[15:0] = {data_in[7:0],data_in[15:8]};

............................................................................................................................

next_ch1_tx_reg = ch1_tx_reg << 'h1;

next_ch2_tx_reg = ch2_tx_reg << 'h1;

test with es9038q2m DAC

result:

1,DSD test with ASIO driver up to DSD512.

2,DOP test withh ASIO and WASAPI up to DSD256 (DOP512 with noise,may be cpld timing constrains issue)

3,DOP not work stable some times no sound output. there are pop and crack sound output while switch music.

- Home

- Source & Line

- PC Based

- Yet another UAC2 implementation, based on CY7C68013A and CPLD, up to 768k/32bit 2ch (tested)