The code is effectively unsigned binary ranging from 0 up to the number of bits your model of dac chip has. The code is a number you can count to. It can be written in binary, octal, hex, decimal, Roman Numerals, or whatever you want. Its still the same number of bits.

Last edited:

I get that the datasheet is telling us the DAC needs unsigned binary data.

The AD5791 has a register choose binary or twos complement form for the DAC register,

maybe the DACx1001 detects it automatically, doesnt make sense that they would leave this detail out of the datasheet though.

So what do you think is the most likely possibility?

The AD5791 has a register choose binary or twos complement form for the DAC register,

maybe the DACx1001 detects it automatically, doesnt make sense that they would leave this detail out of the datasheet though.

So what do you think is the most likely possibility?

Last edited:

I don't trust the glue logic that has been proposed so far can be relied upon to get the dac working with I2S.

Therefore I go back to what I said before about writing out the bit pattens the dac needs including clock timing and other constraints. Also write out I2S format. Go step by step to transform the I2S into what the dac needs. It amounts to some timing diagrams, similar to what is shown in the dac datasheet, but in this case showing bit patterns for each step of the logic needed to transform from I2s format to dac format.

Unless you think it through on that level you won't understand it clearly enough to troubleshoot if it doesn't work on the first try. And it will be more likely that it will work on the first try.

Therefore I go back to what I said before about writing out the bit pattens the dac needs including clock timing and other constraints. Also write out I2S format. Go step by step to transform the I2S into what the dac needs. It amounts to some timing diagrams, similar to what is shown in the dac datasheet, but in this case showing bit patterns for each step of the logic needed to transform from I2s format to dac format.

Unless you think it through on that level you won't understand it clearly enough to troubleshoot if it doesn't work on the first try. And it will be more likely that it will work on the first try.

Last edited:

The whole thing is pretty strange, that nobody else in the original thread picked up on this either.

I was relying on the glue logic to simplify this project, its becomes too complicated otherwise, too many possible sources of error, I'm not going to attempt it anymore.

I was relying on the glue logic to simplify this project, its becomes too complicated otherwise, too many possible sources of error, I'm not going to attempt it anymore.

Last edited:

Using a 4 bit setup, the MSB being inverted removes the sign bit such that +7 (0111) binary two's complementary becomes +15 (1111) straight binary. Bipolar zero is now +8 straight binary and the most negative value is 0000. I imagine it was simply something taken as read as opposed to not being picked up.The MSB being inverted is the sign bit, not a data bit.

Yeah, normally when someone learns digital starting with the basics of notation, etc., and then common digital circuits, such as an adder, then the need for two's complement may arise because of a need to perform subtraction. We can add a negative number maybe more easily that subtract a positive number. To convert a positive number to negative in two's complement form, just invert all the bits and add one (including any necessary carries to the next higher order columns). I did provide links for reference, at least.

but it only works for positive 2sC values?

2sC -7 (1111) = +1 SB (8-7)

2sC -7 inverted MSB (0111) = +3 SB

2sC -7 (1111) = +1 SB (8-7)

2sC -7 inverted MSB (0111) = +3 SB

The history of it doesn't matter too much when we get to the topic of I2S bus versus SPI bus. For our purposes here, two's-complement form is just a standard convention for representing sample values. I already linked to material on how to convert from one format to the other.

Maybe one small detail not often mentioned is that there is no negative zero used in two's-compliment, thus the minimum and maximum values that can be represented are not quite symmetrical around zero. Its only 1-bit difference, but it has been measured in dacs.

Maybe one small detail not often mentioned is that there is no negative zero used in two's-compliment, thus the minimum and maximum values that can be represented are not quite symmetrical around zero. Its only 1-bit difference, but it has been measured in dacs.

Last edited:

Mi

Definitely F for binary arithmetic class.2sC -7 (1111) = +1 SB (8-7)

2sC -7 inverted MSB (0111) = +3 SB

Hi all, I haven't been frequenting the site as much. I had some job role changes and dont support our audio products anymore (but I still support our precision DACs like the DAC11001). Let me see if I can shed some light here:

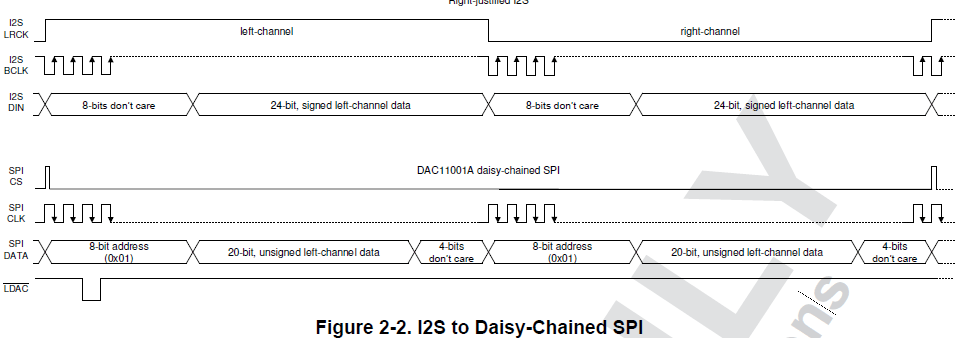

Daisy-chain is useful because you can connect two DACs in series and thereby alternate devices that are being updated. Here is a little better figure showing the modification I was doing:

I preferred RJ data because we need to insert a 8-bit address value to address the correct register (0x01). For you to use I2S, you will likely need to shift or delay the DIN by 7 bits to make room.

There are some key design challenges to overcome when created the I2S-to-SPI digital logic.

• The SPI clock is inverted compared to the I2S clock.

• The 8 most-significant bits in the I2S frame are "don't-cares" while the DAC11001A requires this to be the

DAC address, 0x01.

• The 4 least significant bits (LSBs) for the DAC11001A are "don't-cares". This is not a major issue as 24-bit

data is common in I2S, so no shifting is necessary.

• The LRCK is 50% duty-cycle signal, while the DAC11001A requires an active-low chip select line.

• It is desired that both the DACs latch the data at same time, so an LDAC signal must be generated as well.

• The data value in I2S is a signed 24-bit integer, while the DAC11001A requires an unsigned integer. This

means the most-significant bit of the data value will need to be inverted.

Inverting the data's MSB is a simple way of converting two's complement data to unsigned data. Take a look:

Daisy-chain is useful because you can connect two DACs in series and thereby alternate devices that are being updated. Here is a little better figure showing the modification I was doing:

I preferred RJ data because we need to insert a 8-bit address value to address the correct register (0x01). For you to use I2S, you will likely need to shift or delay the DIN by 7 bits to make room.

There are some key design challenges to overcome when created the I2S-to-SPI digital logic.

• The SPI clock is inverted compared to the I2S clock.

• The 8 most-significant bits in the I2S frame are "don't-cares" while the DAC11001A requires this to be the

DAC address, 0x01.

• The 4 least significant bits (LSBs) for the DAC11001A are "don't-cares". This is not a major issue as 24-bit

data is common in I2S, so no shifting is necessary.

• The LRCK is 50% duty-cycle signal, while the DAC11001A requires an active-low chip select line.

• It is desired that both the DACs latch the data at same time, so an LDAC signal must be generated as well.

• The data value in I2S is a signed 24-bit integer, while the DAC11001A requires an unsigned integer. This

means the most-significant bit of the data value will need to be inverted.

Inverting the data's MSB is a simple way of converting two's complement data to unsigned data. Take a look:

| Two's complement value | I2S Code Description | Value with MSB inverted | Unsigned meaning |

| 0x7FFFF (+524287 dec) | Full-scale - 1LSB | 0xFFFFF (+1048575 dec) | Full-scale (VREFH-1LSB) |

| 0x00001 | +1LSB above zero-scale | 0x80001 (+524289) | mid-scale +1lsb |

| 0x00000 | zero-scale (some call mid-scale) | 0x80000 (+524288) | mid-scale (~0V) |

| 0xFFFFF | -1LSB below zero-scale | 0x7FFFF (+524287) | mid-scale -1lsb |

| 0x80000 (-524288 dec) | -Full-scale | 0x00000 (0) | VREFL |

Something I'm trying to understand is why the main shift register has 2 inputs held high instead of one.

I think it could be to have a longer LDAC pulse so that the LDAC minimum low time (20ns) is satisfied even at the highest clock rates,

however the shift register output also drives the XOR and it causes the audio data MSB to be inverted.

View attachment 1287228

The reason there are two bits being inverted is to accomplish 2 main things and 1 bonus:

1. We need to invert the MSB of the two's complement data to convert it to straight binary.

2. The DAC annoyingly needs to be addressed, and the data register of the DAC is address 0x01. Working under the assumption that the 8 MSB bit positions of 24-bit RJ I2S in a 32-bit frame are 0x00, I invert bit 24 to get my address.

Bonus: I wanted a LDAC pulse that has to be some delay after CS edge. 7 bit-times was sufficient, so I just reused this 2-bit pulse as my LDAC signal as well. Saved a few gates.

- Home

- Source & Line

- Digital Line Level

- TI DACx1001 discussion - I2S input, Vref etc