I am trying to build a wifi airplay module for Airplay as of now. Though the Linkplay modules can do much more and can possibly replace Moode / Volumio / PCP on Raspberry pi.

So my challenges are the PCB design and selection of DAC chip. I still do not know if the Linkplay board will play the game or not as PE does not share much info on it. But since the cost was $10, I could not help picking one up.

So Far I have been able to connect the link play module to my local wifi and have my iPhone play connect to it like an Airplay Device and the phone transfer's the audio to it.

I am also able to send API get-command to it check what is playing on it and change volume - this works.

LinkPlay Module has I2S audio out of about 24bit / 192kHz.

Also, the I2S pins are BCLK, LRCLK, and DATA_OUT. Only MCLK is not provided.

The Biggest Question that arises is which DAC and how to connect

PCM5102

ESS9023

?

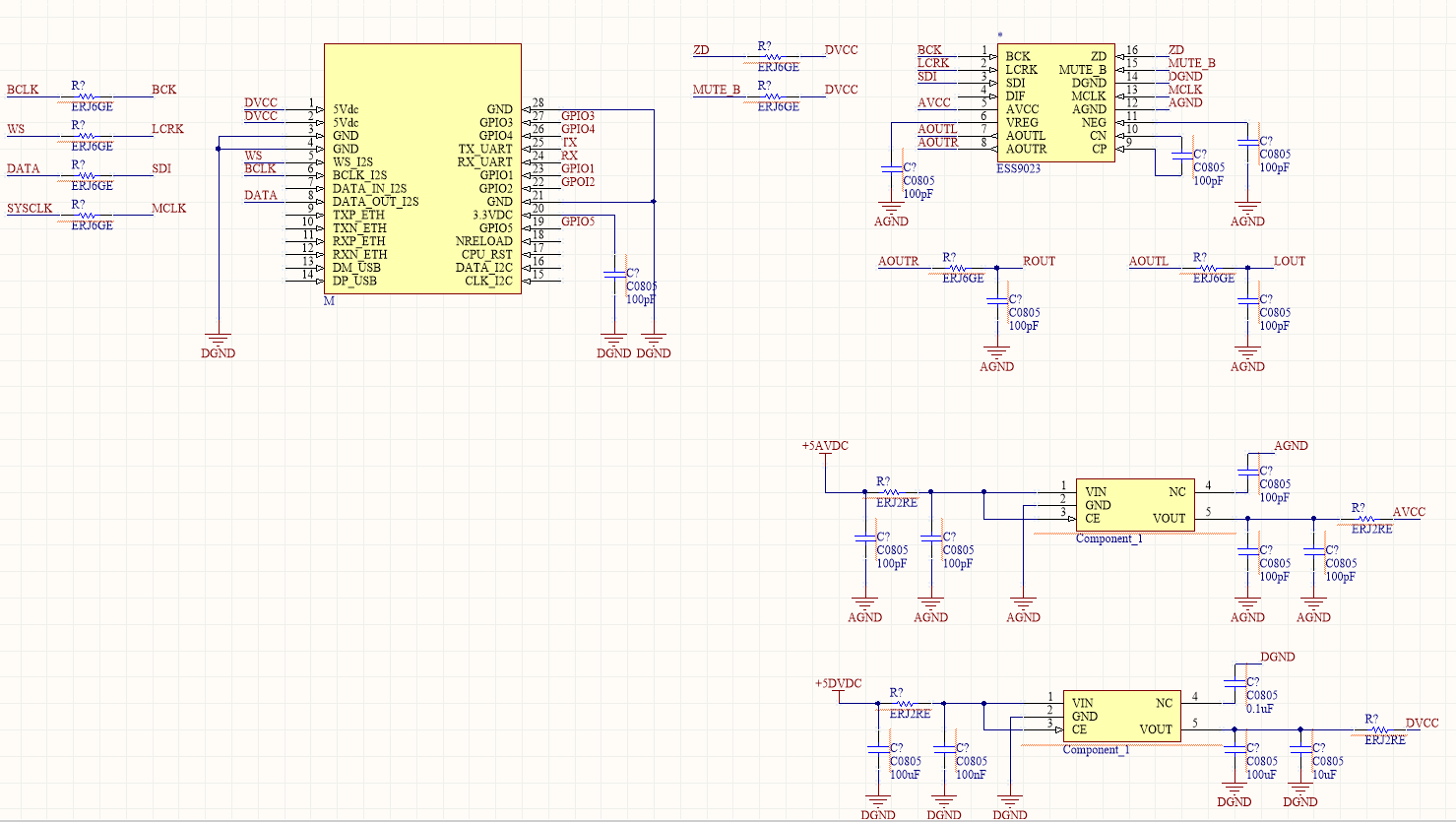

this is the schematic i have built so far - the Resistor the output of the Regulators is going to be chokes and not resistor, its a place holder

So my challenges are the PCB design and selection of DAC chip. I still do not know if the Linkplay board will play the game or not as PE does not share much info on it. But since the cost was $10, I could not help picking one up.

So Far I have been able to connect the link play module to my local wifi and have my iPhone play connect to it like an Airplay Device and the phone transfer's the audio to it.

I am also able to send API get-command to it check what is playing on it and change volume - this works.

LinkPlay Module has I2S audio out of about 24bit / 192kHz.

Also, the I2S pins are BCLK, LRCLK, and DATA_OUT. Only MCLK is not provided.

The Biggest Question that arises is which DAC and how to connect

PCM5102

ESS9023

?

this is the schematic i have built so far - the Resistor the output of the Regulators is going to be chokes and not resistor, its a place holder

Personally I really like the Wolfson DACs. They are easy to integrate, sound amazing and a couple support full line level outputs. Alas, Cirrus Logic bought them out but they're still made. Look at the Cirrus website and pick the WM8### parts. Should be available from the usual suspects.

Mat

Mat

ES9023 doesn't appear to have internal ASRC. That means it would need I2S signals to be synchronous with MCLK, but the module doesn't output an MCLK. Therefore to use ES9023 you would need to add an MCLK source and an ASRC chip, then use that MCLK as the reference clock for the dac chip and for the ASRC. The ASRC would go between the module and the dac chip to resample the I2S stream so that its synchronous with your added MCLK.

Is there an Hardware based ASRC option?ES9023 doesn't appear to have internal ASRC. That means it would need I2S signals to be synchronous with MCLK, but the module doesn't output an MCLK. Therefore to use ES9023 you would need to add an MCLK source and an ASRC chip, then use that MCLK as the reference clock for the dac chip and for the ASRC. The ASRC would go between the module and the dac chip to resample the I2S stream so that its synchronous with your added MCLK.

or

PCM5102 would do the job? Since it’s data sheet says it will work on 3wire bus.

AD1896 appears to require a MCLK signal.

PCM5102 can be configured to operate without a master clock. Page 2 of the datasheet says:

"The integrated PLL on the device removes the requirement for a system clock (commonly known as master

clock), allowing a 3-wire I2S connection and reducing system EMI."

PCM5102 can be configured to operate without a master clock. Page 2 of the datasheet says:

"The integrated PLL on the device removes the requirement for a system clock (commonly known as master

clock), allowing a 3-wire I2S connection and reducing system EMI."

You are missing something. MCLK, BCLK, and LRCK usually all have to be synchronous. However most of the ESS dac chips have internal ASRC, so a synchronous MCLK is optional for them. That said, ES9023 doesn't include ASRC.

In the above screenshot , could the red boxed sentence mean that we can use this ESS9023 with a 49.152MHz Oscilator (TXCO)

Found the below schematic,

https://www.audiophonics.fr/en/dac-...c-es9023-raspberry-pi-a-b-20-i2s-p-11215.html

Last edited:

Fs is the frame sample rate, for PCM digital audio Fs is the LRCK frequency. When the table indicates the MCKLK is 256fs, that means it is, for example, exactly 256 x 192kHz = 49,152MHz. However, no two different (say for example, 49,152MHz) clocks are exactly synchronous with each other. They all differ a little bit in frequency and jitter.

The way it normally works that the I2S clocks are derived from a single MCLK by using frequency divider logic. That division can happen in a USB board, some dac chips can do the division and generate the I2S clocks, etc.

Generally speaking, if no ASRC, no PLL, no FIFO buffer, then all clocks must be synchronous.

Of course, some old dac chips didn't use an MCLK signal since they were not oversampling. In the case of PCM5102, it can generate a master clock using in internal PLL, although that's about the worst way to do it.

The way it normally works that the I2S clocks are derived from a single MCLK by using frequency divider logic. That division can happen in a USB board, some dac chips can do the division and generate the I2S clocks, etc.

Generally speaking, if no ASRC, no PLL, no FIFO buffer, then all clocks must be synchronous.

Of course, some old dac chips didn't use an MCLK signal since they were not oversampling. In the case of PCM5102, it can generate a master clock using in internal PLL, although that's about the worst way to do it.

Last edited:

I can shop from either RS or Element14 and they carry only TI and that is too limited, PCM5102A is around $4.5 + local Taxes.You are missing something. MCLK, BCLK, and LRCK usually all have to be synchronous. However most of the ESS dac chips have internal ASRC, so a synchronous MCLK is optional for them. That said, ES9023 doesn't include ASRC.

Currently, I have one ESS so designing a board with it.

Okay. Then you need a I2S source device that uses the same MCLK as the dac does. MCLK can be from inside the source device, or maybe near the dac chip.

Near the dac chip is normally preferred. In that case you send a copy of the dac chip MCLK to the source device. You would need a source device that can be configured to use an external MCLK.

EDIT: some dac chips can generate I2S clocks for the source device to use, if the source device supports operating in I2S 'slave mode.'

Otherwise you can bridge the two MCLK domains with an ASRC (or a more expensive FIFO buffer).

Near the dac chip is normally preferred. In that case you send a copy of the dac chip MCLK to the source device. You would need a source device that can be configured to use an external MCLK.

EDIT: some dac chips can generate I2S clocks for the source device to use, if the source device supports operating in I2S 'slave mode.'

Otherwise you can bridge the two MCLK domains with an ASRC (or a more expensive FIFO buffer).

Some possible examples at: https://www.mouser.com/c/semiconduc...verters/?q=sample rate converter&sort=pricing

However, not all of them may be suitable for what you need. The TI SRC419x series are good. Have to read the data sheets to know the differences.

Otherwise, you might look for an older dac chip that doesn't use MCLK. Or you could consider an ESS dac chip that includes ASRC, such as ES9038Q2M.

That said, there is lot to know to be able to design a good dac board. Layout for RF is important. That includes using multilayer boards with ground planes.

However, not all of them may be suitable for what you need. The TI SRC419x series are good. Have to read the data sheets to know the differences.

Otherwise, you might look for an older dac chip that doesn't use MCLK. Or you could consider an ESS dac chip that includes ASRC, such as ES9038Q2M.

That said, there is lot to know to be able to design a good dac board. Layout for RF is important. That includes using multilayer boards with ground planes.

@aditya , I see the specific issue you raised about the chart in ES9023 datasheet. I think they could have taken that bit about 'asynchronous mode' from their other datasheets. ES9023 doesn't have control registers or dedicated pins to select between asynchronous or synchronous modes, anyway not that I know of at the moment. Also, the block diagram does not show an ASRC block, which is necessary for asynchronous mode (although there is a jitter suppression block). So far as I can tell it is only synchronous mode. Otherwise, maybe it is only asynchronous? Maybe it has automatic switching between modes?

Last edited:

Hey Thank MarkW4,@aditya , I see the specific issue you raised about the chart in ES9023 datasheet. I think they could have taken that bit about 'asynchronous mode' from their other datasheets. ES9023 doesn't have control registers or dedicated pins to select between asynchronous or synchronous modes, anyway not that I know of at the moment. Also, the block diagram does not show an ASRC block, which is necessary for asynchronous mode (although there is a jitter suppression block). So far as I can tell it is only synchronous mode. Otherwise, maybe it is only asynchronous? Maybe it has automatic switching between modes?

I am still trying to get the Digital Audio stuff in my tiny head, but yes the block is from the ESS9023 datasheet. So yes it could as you say,

I could try to "wire" an oscillator to the board I have (Arylic) and do the shortest wire possible connection to try but, fear I may damage the oscillator by that method.

Looking around for more info on ES9023, found this:

"Orange : MCLK -> nc (ES9023 is in asynchronous mode)"

...where presumably, nc = no connection.

Found it at: https://discourse.zynthian.org/t/dac-teradak-es9023/1606/2

On the other hand there is something about at 100-ohm resistor at:

http://home.teradak.com/products/84.html

EDIT: As is not unusual for ESS, looks like they left some info out of the datasheet.

"Orange : MCLK -> nc (ES9023 is in asynchronous mode)"

...where presumably, nc = no connection.

Found it at: https://discourse.zynthian.org/t/dac-teradak-es9023/1606/2

On the other hand there is something about at 100-ohm resistor at:

http://home.teradak.com/products/84.html

EDIT: As is not unusual for ESS, looks like they left some info out of the datasheet.

Last edited:

- Home

- Source & Line

- Digital Line Level

- Simple DAC for LinkPlayA28/31