Good idea.It might be useful to do a sensitivity analysis on device match for paralleling.

Hans

The effect is surprisingly mild.It might be useful to do a sensitivity analysis on device match for paralleling.

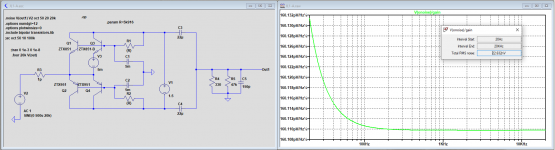

I created a ZTX851-B with 2/3 Hfe of the ZTX851.

Then I adjusted the base resistance from 6k5 to 5k9 to keep the total current through the transistors in both cases at 5.5mA.

Result in noise goes from 22.616nV to 22.618nV, almost no difference at all !

Hans

Attachments

The effect is surprisingly mild.

I created a ZTX851-B with 2/3 Hfe of the ZTX851.

Then I adjusted the base resistance from 6k5 to 5k9 to keep the total current through the transistors in both cases at 5.5mA.

Good, there is Vbe match too possibly more important. The emitter ballast resistors hurt the noise and at a couple of milliamps 1 Ohm does not do much. I don't know the distribution one might expect, but it only takes 18mV for 2:1 ratio. Usually the need for matching is overstated, it might be nice to put a number on it.

As a next step, I gave the ZTX851-B a 5mV Vbe offset, still keeping the total current through the transistors at 5.5mA.

Noise went up a tiny little bit to 22.632nV.

For the time being, this circuit seems quite resistive to individual transistor differences,

Hans

Noise went up a tiny little bit to 22.632nV.

For the time being, this circuit seems quite resistive to individual transistor differences,

Hans

Attachments

Wayne has done some measurements, as well as coming up with a quick and nifty matching jig. On small samples 80% are within 500uV on Vbe. Hfe varies from 140-200 with the main hump being 140-160.

Wayne has done some measurements, as well as coming up with a quick and nifty matching jig. On small samples 80% are within 500uV on Vbe. Hfe varies from 140-200 with the main hump being 140-160.

With all respect, the temp coeff of a semiconductor lies around 2mV/degree.

You will need a robot in a temp controlled room to measure Vbe differences of 500uV !

Picking them up by hand is already enough to let the Vbe change several mV.

Hans

On small samples 80% are within 500uV on Vbe.

Wafer to wafer? I don't believe it, pulled off of tape and reel in sequence maybe. As Hans said you would need an almost perfect iso-thermal test set up to even make such a claim.

Last edited:

This is 10 pulled out a bag at random. I did say 'small samples'. And I do know that for you a small sample used to be 10^5. 🙂

Wayne is selling a few of his MC stages to record cutters out there, so I will keep an eye if he notes any shift across batches. I certainly wouldn't use this data to start a volume run.

Wayne is selling a few of his MC stages to record cutters out there, so I will keep an eye if he notes any shift across batches. I certainly wouldn't use this data to start a volume run.

I think that matching will not be really critical.It might be useful to do a sensitivity analysis on device match for paralleling.

If I simulate the Duraglit with e.g. 6mA Ic the resulting noise en noise density is 173pV/rtHz (for the amp alone, Rs = 0), If current is simply doubled, noise reduces to 140 pV/rtHz. If two transistors are in parrallel with 6mA each, noise reduces to 122pV/rtHz. This lower value can be explained as in the later case, Rbb of the transistors is also halved while for doubled Ic alone, everything is halving except Rbb.

If transistors are slightely mismatched, the reulting net penalty in noise performance will be small (result will be between 122pV/rtHz and 140pV/rtHz from the example above)

That is exactely what I found (one of my posst from a couple of weeks ago) when creating ZTX device models with Hfe of 100, 200 and 300 (min, typ and max values from datasheet) and simmed various combinations out of them including paralleling two of such different devices. When adjusting the collector current by changing the base resistors, performance was not changing at all.The effect is surprisingly mild.

I created a ZTX851-B with 2/3 Hfe of the ZTX851.

Then I adjusted the base resistance from 6k5 to 5k9 to keep the total current through the transistors in both cases at 5.5mA.

Result in noise goes from 22.616nV to 22.618nV, almost no difference at all !

Hans

I also measured about 40 ZTX transistors (npn and pnp each) from 3 different batches, the Hfe spread was well within the datasheet spec range (min. for npn 148, max for npn 235, min for pnp 175, max for pnp 255). Vbe differences were smaller than 10mV.

Last edited:

I think that matching will not be really critical.

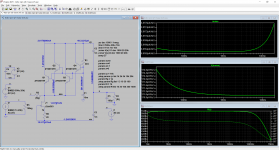

Simply seeing if completely dumping the emitter resistors makes sense they only add noise.

That was also my take. Leave them out if not really required. As the BJTs re (Vt/Ic) is still a few Ohms, 1R of external resistor in addition will have no significant effect in stabilizing the operating points.

You need 2SK363 BL or V grade (Vp<-0.5V) and to cross your fingers. The JFET will be at the very limit of saturation, too close to my taste to the linear region. Vds>Vgs-Vp~-0.5+1.2=0.7V since Vpmax=-1.2V. It could work, but I personally would not use such a JFET active load for a power supply voltage of less that 3.5V. Otherwise, for 2.5V, you have only 1.25V for a Vbe of 0.6V and the remainder 0.65V to keep the JFET in saturation.

I use 2sk369V.

At ~500µA, saturation is obtained with Vds ~100mV.

I have not the possibility to make a proto until 2 or 3 weeks.

No problem, but I think it is still improvable.I hope you don't mind, but I'd like to add it to the compendium.

The pure simplicity of the Duraglit, despite some Hfe concerns, is still a thing of beauty to my eyes.

Hans

I completely agree

I use 2sk369V.

At ~500µA, saturation is obtained with Vds ~100mV.

For the 2SK369, it may work better. Theoretically, based on the datasheet, the highest Vdsat is 200mV.

Matching the two JFETs is not very critical, but I would use two devices from the same tube.

“Quote:

Originally Posted by Bonsai View Post

I hope you don't mind, but I'd like to add it to the compendium.

No problem, but I think it is still improvable.

—————-

Sure - I’ll probably add it in the next week or so. On the sims I did it’s in the top 5 or 6 for noise.

Originally Posted by Bonsai View Post

I hope you don't mind, but I'd like to add it to the compendium.

No problem, but I think it is still improvable.

—————-

Sure - I’ll probably add it in the next week or so. On the sims I did it’s in the top 5 or 6 for noise.

innovative

Not so much, but the jfet as input current sink is not so common and allow high gain.

One single ended npn transistors input circuit.

Thanks for sharing this. Could you add the Spice models for the 2 semiconductors to the schematic (or as a separate file)?

Thank you,

Thanks for sharing this. Could you add the Spice models for the 2 semiconductors to the schematic (or as a separate file)?

Thank you,

Here they are.

No change since #1379.

Attachments

- Home

- Source & Line

- Analogue Source

- Richard Lee's Ultra low Noise MC Head Amp